博客作者:Dario Fresu

在設(shè)計(jì)電磁兼容性(EMC)表現(xiàn)優(yōu)異的 PCB 時,疊層結(jié)構(gòu)的選擇是需要掌握的核心概念之一。

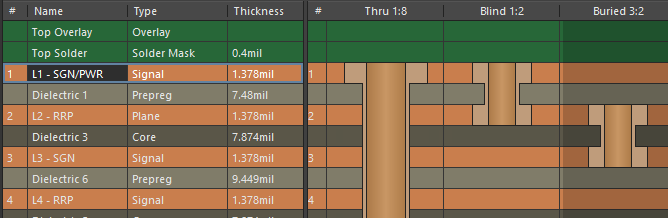

圖 1:Altium Designer 中的層疊管理器工具

這一環(huán)節(jié)之所以至關(guān)重要,是因?yàn)樗c PCB 設(shè)計(jì)中電磁場的約束緊密相關(guān)。

在 “掌握 PCB 設(shè)計(jì)中的 EMI 控制” 系列的第三篇文章中,我們將進(jìn)一步探討這些概念,并介紹其他重要的 EMC 設(shè)計(jì)要點(diǎn)。

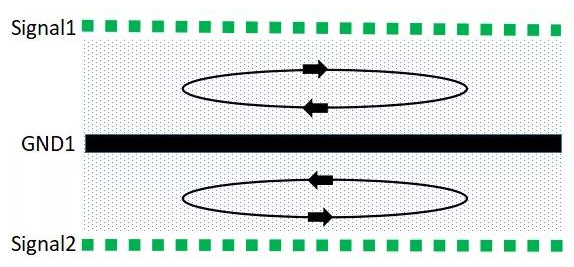

對于信號在電路中的傳播,需要兩個導(dǎo)體形成完整的電流環(huán)路:一個導(dǎo)體傳輸信號,另一個提供返回路徑,以確保電流流通并有效傳輸信號。我們將前者稱為信號導(dǎo)體,后者稱為信號返回與參考導(dǎo)體—— 后者之所以得名,不僅因?yàn)樗鼮樾盘柼峁﹨⒖茧娢唬ɑ蛄汶娢唬€因?yàn)樗仨殲樾盘栯娏鞣祷卦炊颂峁┳钚∽杩孤窂健閷?shí)現(xiàn)這一路徑,最佳配置是選擇平面(而非走線),且該平面不應(yīng)有分割、切口或其他可能導(dǎo)致信號阻抗不連續(xù)的結(jié)構(gòu)。

從這一基本概念可知,每個信號層都需搭配第二個導(dǎo)體(即返回參考平面)以提供返回和參考路徑。遵循這一簡單規(guī)則,我們可通過為每個信號層匹配相鄰的返回參考平面(RRP)來設(shè)計(jì)疊層結(jié)構(gòu)。

以下是幾種可將電磁干擾降至最低的疊層結(jié)構(gòu)示例。

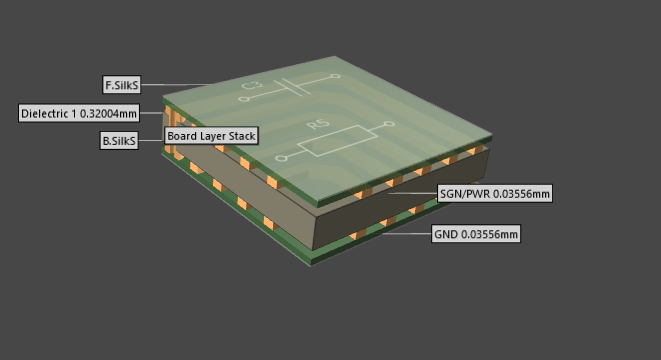

雙層板疊層示例

對于雙層板疊層,一種配置是:一層專門用于信號和電源走線,另一層為完整的返回參考平面。

圖 2:Altium Designer 中層疊可視化工具顯示的雙層板疊層示例

該平面不應(yīng)有分割或大的間隙,同時避免信號走線跨越間隙 —— 這會導(dǎo)致阻抗不連續(xù)、擴(kuò)大電流環(huán)路并最終增加輻射發(fā)射。若需通過過孔跨層,應(yīng)確保過孔路徑盡可能短,且避免在其他信號走線下方穿越。

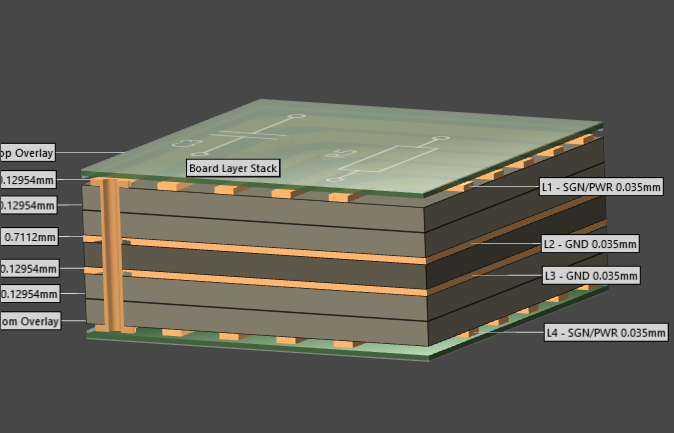

四層板疊層示例

當(dāng)元件和走線密度增加、需要第二層信號層時,四層板疊層更為適用。盡管三層板可實(shí)現(xiàn)類似配置,但從制造角度看,廠商通常更傾向于提供成對的疊層結(jié)構(gòu),因此四層板是更優(yōu)選擇。

四層板有兩種高效配置:

第一種配置中,返回參考平面作為嵌入式平面位于疊層內(nèi)部,即第 1 層和第 4 層為信號平面,第 2 層和第 3 層分別為第 1 層和第 4 層信號提供返回和參考路徑。

第二種配置中,返回參考平面位于第 1 層和第 4 層(充當(dāng)電路的屏蔽層),而信號層位于嵌入式的第 2 層和第 3 層。在此配置中,需增大第 2 層與第 3 層的間距以避免信號場相互干擾,確保每個信號層僅與返回參考平面耦合。

在兩種配置中,均需在返回參考平面之間添加縫合過孔,其主要作用包括:

形成法拉第屏蔽以減少輻射和外部干擾;

維持平面等電位并降低共模電壓;

為跨層信號提供返回和參考路徑。

此時,電源也可布設(shè)在信號層。

圖 3:Altium Designer 中層疊可視化工具顯示的四層板疊層示例

四層板中完全專用電源層的情況未在此討論,因?yàn)閺?EMC 設(shè)計(jì)角度不建議這樣做 —— 處理不當(dāng)可能產(chǎn)生共模電壓噪聲,該話題需另文詳述。

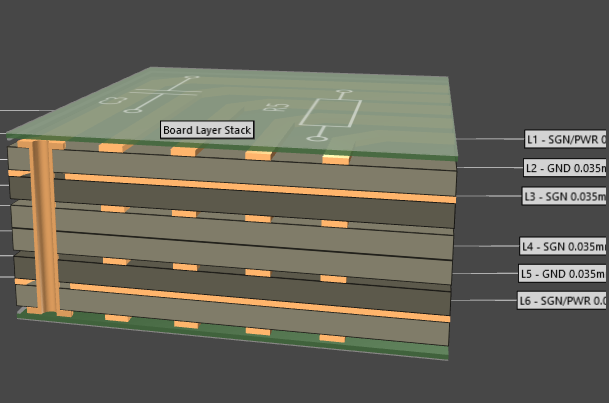

六層板疊層示例

六層板在信號層和電源層分配上提供了更高自由度。

圖 4:Altium Designer 中層疊可視化工具顯示的六層板疊層示例

以下兩種疊層結(jié)構(gòu)具備出色的 EMC 性能:

疊層 1:信號布設(shè)在第 1 層和第 6 層,返回參考平面位于第 2 層和第 5 層,第 3 層和第 4 層為額外信號層。此配置中,第 2 層和第 5 層可作為所有四個信號層的返回和參考平面,這得益于趨膚效應(yīng)—— 它允許平面兩側(cè)承載不同電流而不混合。趨膚效應(yīng)指交流電傾向于在導(dǎo)體表面分布(表面電流密度最大、中心最小),這是由于交流電產(chǎn)生的變化磁場誘導(dǎo)渦流,抑制導(dǎo)體中心的電流流動并迫使電流向表面聚集。在此類疊層中,電源網(wǎng)絡(luò)可與信號層共面布設(shè)。

疊層 2:信號布設(shè)在第 1 層和第 6 層,第 2 層和第 5 層為返回參考層,第 3 層和第 4 層為電源平面。此疊層尤其適用于高功率需求或需要低阻抗電源網(wǎng)絡(luò)的場景,建議返回參考層和電源層均采用完整均勻的平面 —— 避免在單層使用不同多邊形(可能產(chǎn)生共模噪聲并在連接電纜時導(dǎo)致輻射發(fā)射),應(yīng)為每個電壓單獨(dú)分配平面以避免此類問題并改善電路板的電源傳輸網(wǎng)絡(luò)(PDN)。

與四層板類似,需確保內(nèi)層信號層與電源層間距足夠大以避免耦合干擾,同時最大化信號層與返回參考層的耦合,并盡可能在返回參考平面間添加縫合過孔。

借助 Altium Designer實(shí)現(xiàn)簡單多層疊層設(shè)計(jì)

幸運(yùn)的是,Altium Designer 的集成層疊管理器工具可簡化 PCB 疊層選擇流程:

通過該工具,可創(chuàng)建自定義疊層或使用預(yù)設(shè)疊層,大幅降低 PCB 設(shè)計(jì)師的工作復(fù)雜度;還可創(chuàng)建更高級的疊層類型,并直接計(jì)算信號特征阻抗(無需依賴第三方工具)。

這僅是 Altium Designer 眾多功能之一,它支持無縫且精準(zhǔn)的 PCB 項(xiàng)目創(chuàng)建,讓設(shè)計(jì)流程不僅更輕松,也更具愉悅性。

下一篇文章中,我們將探討如何設(shè)計(jì)和優(yōu)化 PCB 以實(shí)現(xiàn)低 EMI。

關(guān)于Altium

Altium有限公司隸屬于瑞薩集團(tuán),總部位于美國加利福尼亞州圣迭戈,是一家致力于加速電子創(chuàng)新的全球軟件公司。Altium提供數(shù)字解決方案,以最大限度提高電子設(shè)計(jì)的生產(chǎn)力,連接整個設(shè)計(jì)過程中的所有利益相關(guān)者,提供對元器件資源和信息的無縫訪問,并管理整個電子產(chǎn)品生命周期。Altium生態(tài)系統(tǒng)加速了各行業(yè)及各規(guī)模企業(yè)的電子產(chǎn)品實(shí)現(xiàn)進(jìn)程。

-

pcb

+關(guān)注

關(guān)注

4366文章

23484瀏覽量

409500 -

altium

+關(guān)注

關(guān)注

48文章

979瀏覽量

120162 -

emc

+關(guān)注

關(guān)注

172文章

4163瀏覽量

186898 -

電磁干擾

+關(guān)注

關(guān)注

36文章

2391瀏覽量

106551 -

疊層

+關(guān)注

關(guān)注

0文章

30瀏覽量

10114

原文標(biāo)題:【技術(shù)博客】掌握 PCB 設(shè)計(jì)中的 EMI 控制之如何為 EMC 設(shè)計(jì)選擇疊層結(jié)構(gòu)

文章出處:【微信號:AltiumChina,微信公眾號:Altium】歡迎添加關(guān)注!文章轉(zhuǎn)載請注明出處。

發(fā)布評論請先 登錄

單層板到八層板的疊層,究竟應(yīng)該怎么設(shè)計(jì)與選擇

PCB疊層EMC規(guī)劃與設(shè)計(jì)思路

PCB疊層設(shè)計(jì)避坑指南

PCB疊層設(shè)計(jì)

原創(chuàng)|PCB設(shè)計(jì)中疊層結(jié)構(gòu)的設(shè)計(jì)建議

PCB疊層設(shè)計(jì)的原則和結(jié)構(gòu)

【資料】淺談PCB疊層設(shè)計(jì)

如何進(jìn)行PCB疊層的EMC設(shè)計(jì)

淺談PCB疊層EMC規(guī)劃與設(shè)計(jì)思路

PCB設(shè)計(jì)時如何選擇合適的疊層方案

PCB疊層結(jié)構(gòu)設(shè)計(jì)詳解

各種疊層結(jié)構(gòu)的PCB圖內(nèi)部架構(gòu)設(shè)計(jì)

如何為EMC設(shè)計(jì)選擇PCB疊層結(jié)構(gòu)

如何為EMC設(shè)計(jì)選擇PCB疊層結(jié)構(gòu)

評論