1、關于如何在VHDL模塊調用一個Verilog模塊

在VHDL模塊聲明一個要與調用的Verilog模塊相同名稱的元件(component),元件的名稱和端口模式應與Verilog模塊的名稱和輸入/輸出模式相同。注意Verilog區分大小寫,VHDL不區分,所以模塊名字一定要完全一致,不能搞混。

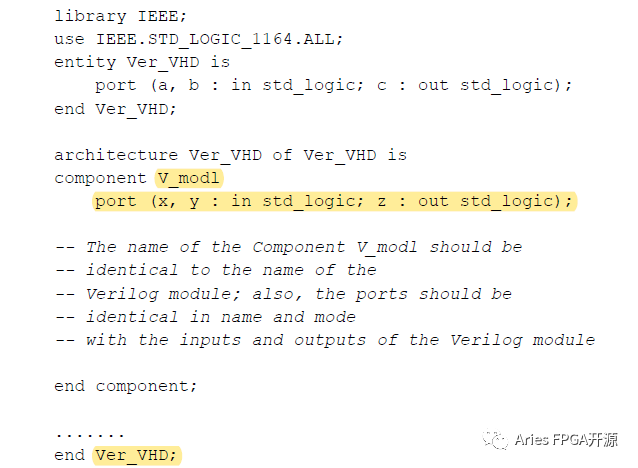

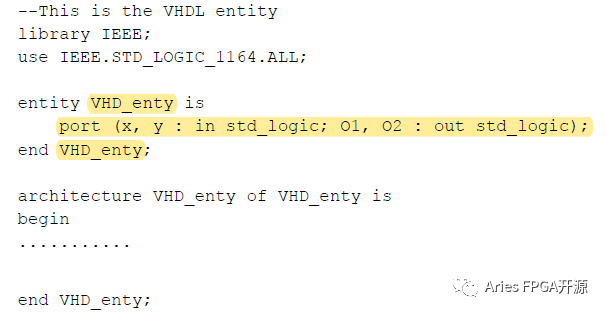

舉個例子:下面是一個VHDL模塊,在里面聲明了一個元件(component)

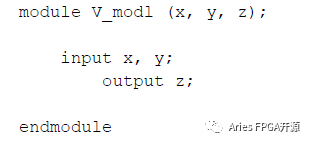

看Verilog模塊再

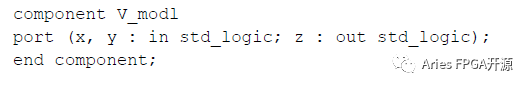

VHDL的模塊就是通過聲明一個元件(component)來調用這個Verilog模塊,將元件聲明提出來講,如下圖:

對比這個Verilog模塊和VHDL中聲明的元件不難發現,模塊名/端口/輸入輸出模式完全一樣,這和VHDL自己調用用VHDL的元件(component)基本一樣。

2、關于如何在Verilog中調用VHDL模塊

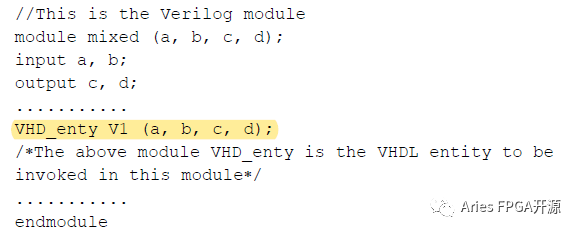

在Verilog中,通過在Verilog模塊中輸入其名稱(標識符)及端口來調用VHDL實體。模塊的參數應該與實體的類型和端口的方向匹配,可以映射到Verilog模塊的VHDL端口為:in,out和inout;在某些模擬器中,不允許使用緩沖區。Verilog模塊只能使整個VHDL實體可見。

舉個例子:下圖是一個Verilog模塊調用了VHDL模塊(高亮處)

下圖是一個VHDL模塊

Simulator(模擬器,注:這個是英文原版使用的詞語,我的理解就是一些EDA)首先在Verilog模塊中查找,以查看是否有任何名為VHD_enty的Verilog模塊。如果找不到,模擬器將在VHDL實體中查找。當模擬器找到名稱為VHD_enty的實體時,它將該實體綁定到Verilog模塊。在代碼中,輸入a被傳遞到輸入端口x;輸入b傳遞給輸入y。VHDL實體計算輸出O1和O2;這兩個輸出分別傳遞到Verilog輸出c和d。調用VHDL模塊與調用功能或任務非常相似。

例子舉完了,下面驗證一下

驗證:在Verilog中調用VHDL模塊實體(VHDL調用Verilog考慮到比較簡單,大家用的更多是Verilog,就不舉例子了)

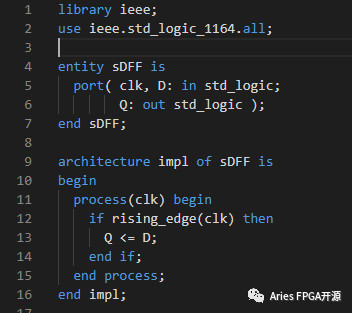

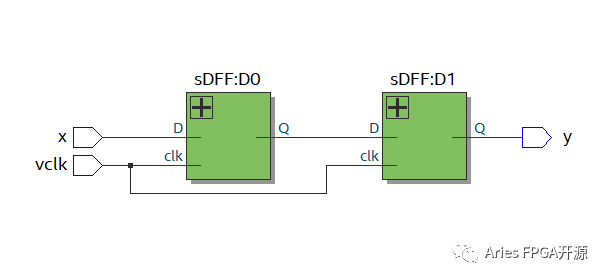

驗證內容:使用Verilog調用兩個VHDL寫的D觸發器模塊實現打兩拍。

這個代碼是一個用VHDL語言寫的D觸發器模塊,在FIFO中也寫過。

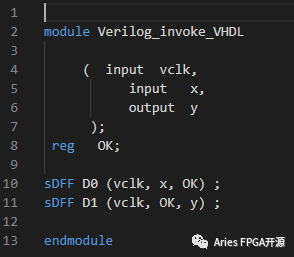

這個代碼是Verilog寫的,在內部調用兩個由VHDL寫的D觸發器,實現兩級D觸發器。

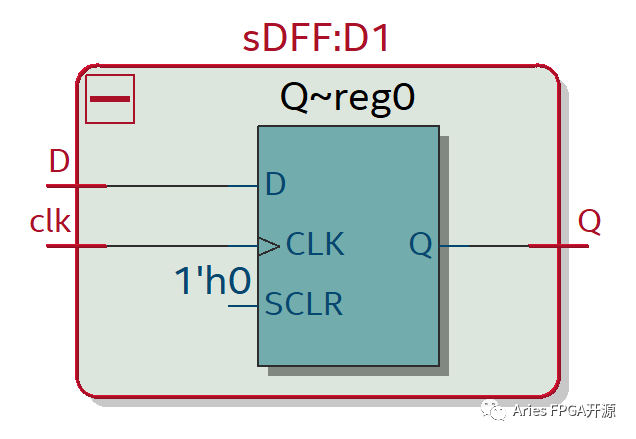

上圖是VHDL寫的D觸發器綜合出的原理圖,注意對應的端口。

上圖是Verilog代碼綜合出來的原理圖,從代碼上看,定義了vclk、x、y三個端口,連接VHDL寫的兩個D觸發器,基本的調用過程就是這樣。

總結:兩者的互相調用過程都不復雜,舉個基礎的例子只是為了大家熟悉這個過程。在實際中難免會遇到有互相調用的地方。

編輯:jq

-

FPGA

+關注

關注

1643文章

21982瀏覽量

614557 -

vhdl

+關注

關注

30文章

819瀏覽量

129600 -

觸發器

+關注

關注

14文章

2033瀏覽量

61916

原文標題:關于VHDL和Verilog模塊互相調用的問題

文章出處:【微信號:zhuyandz,微信公眾號:FPGA之家】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

淺談Verilog和VHDL的區別

Verilog 與 ASIC 設計的關系 Verilog 代碼優化技巧

Verilog 測試平臺設計方法 Verilog FPGA開發指南

Verilog與VHDL的比較 Verilog HDL編程技巧

Verilog vhdl fpga

Verilog硬件描述語言參考手冊

FPGA編程語言的入門教程

FPGA芯片架構和資源有深入的理解,精通Verilog HDL、VHDL

【招聘】verilog vhdl FPGA

智能防雷監控模塊的應用與技術探討

探討VHDL和Verilog模塊互相調用的問題

探討VHDL和Verilog模塊互相調用的問題

評論