FPGA(現場可編程邏輯門陣列)的編程涉及特定的硬件描述語言(HDL),其中Verilog和VHDL是最常用的兩種。以下是一個FPGA編程語言(以Verilog為例)的入門教程:

一、Verilog編程基礎

- 基本結構

Verilog程序的基本結構包括模塊(module)和端口(port)定義。每個模塊都有輸入(input)、輸出(output)和可能的雙向(inout)端口。 - 數據類型

Verilog支持多種數據類型,包括線網類型(如wire)和寄存器類型(如reg)。線網類型通常用于組合邏輯,而寄存器類型則用于時序邏輯。 - 基本運算符

Verilog中的運算符包括算術運算符、邏輯運算符、位運算符等。這些運算符用于構建復雜的邏輯表達式。 - 賦值語句

Verilog中的賦值語句有阻塞賦值(=)和非阻塞賦值(<=)兩種。阻塞賦值在賦值語句執(zhí)行完成之前不會繼續(xù)執(zhí)行下一條語句,而非阻塞賦值則允許并行執(zhí)行多個賦值語句。

二、組合邏輯與時序邏輯

- 組合邏輯

組合邏輯電路的輸出僅取決于當前輸入的值。在Verilog中,可以使用連續(xù)賦值語句(assign)來實現組合邏輯。 - 時序邏輯

時序邏輯電路的輸出不僅取決于當前輸入的值,還取決于先前的狀態(tài)。在Verilog中,時序邏輯通常使用always塊來實現,并可以結合非阻塞賦值語句來模擬時鐘邊沿觸發(fā)的行為。

三、Verilog編程實踐

- 門電路實現

通過Verilog編程,可以實現基本的門電路,如與門(AND gate)、或門(OR gate)、非門(NOT gate)等。 - 組合電路實現

可以進一步實現更復雜的組合電路,如全加器、多路選擇器等。這些電路的實現需要利用Verilog中的邏輯運算符和位運算符。 - 時序電路實現

時序電路的實現需要利用always塊和寄存器類型的數據。例如,可以實現D觸發(fā)器、計數器等時序電路。

四、使用開發(fā)環(huán)境進行仿真與驗證

- 開發(fā)環(huán)境搭建

FPGA開發(fā)需要特定的軟件和工具,如Xilinx Vivado、Quartus Prime等。這些開發(fā)環(huán)境提供了設計、實現、調試和仿真等功能。 - 仿真與驗證

在開發(fā)過程中,需要進行仿真與驗證以確保電路的正確性。可以使用開發(fā)環(huán)境提供的仿真工具來模擬電路的行為,并觀察輸出結果是否與預期一致。

五、學習資源與建議

- 在線教程與書籍

可以通過在線教程、書籍等資源來學習Verilog和FPGA編程。這些資源通常提供了詳細的語法介紹、示例代碼和練習題。 - 實踐項目

通過參與實踐項目來加深對Verilog和FPGA編程的理解。可以嘗試設計并實現一些簡單的電路,如LED閃爍電路、數碼管顯示電路等。 - 社區(qū)與論壇

可以加入相關的社區(qū)和論壇,與其他FPGA開發(fā)者交流經驗和心得。這些社區(qū)和論壇通常提供了豐富的技術資料和解決方案。

總之,FPGA編程是一項需要不斷學習和實踐的技能。通過掌握Verilog等硬件描述語言,了解組合邏輯與時序邏輯的基本原理,并利用開發(fā)環(huán)境進行仿真與驗證,可以逐步提高自己的FPGA編程能力。

聲明:本文內容及配圖由入駐作者撰寫或者入駐合作網站授權轉載。文章觀點僅代表作者本人,不代表電子發(fā)燒友網立場。文章及其配圖僅供工程師學習之用,如有內容侵權或者其他違規(guī)問題,請聯系本站處理。

舉報投訴

-

寄存器

+關注

關注

31文章

5427瀏覽量

123743 -

硬件

+關注

關注

11文章

3469瀏覽量

67295 -

編程語言

+關注

關注

10文章

1955瀏覽量

36293 -

fpga編程

+關注

關注

0文章

4瀏覽量

4697

發(fā)布評論請先 登錄

相關推薦

熱點推薦

Linux下C語言編程入門教程

u3000本文是Linux 下C 語言編程入門教程。主要介紹了Linux 的發(fā)展與特點、C語言的基礎知識、Linux 程序設計基礎知識及其下C 語言

發(fā)表于 09-22 06:56

PLC編程是什么?圖解PLC編程入門教程

本文開始介紹了PLC編程的概念和PLC編程的七大特點,其次闡述了PLC編程工作原理與PLC的五種標準編程語言,最后介紹了PLC

發(fā)表于 04-19 08:42

?7.2w次閱讀

Linux下C語言編程入門教程詳細說明

本文是Linux 下C 語言編程入門教程。主要介紹了Linux 的發(fā)展與特點、C語言的基礎知識、Linux 程序設計基礎知識及其下C 語言

發(fā)表于 08-25 18:05

?39次下載

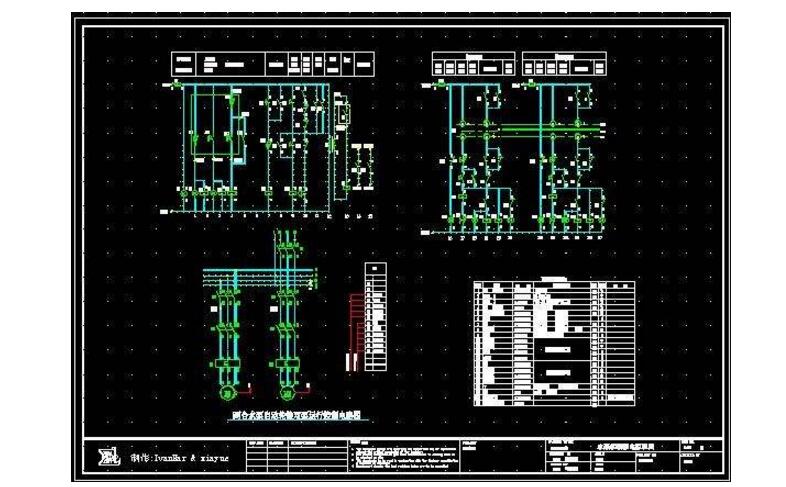

FPGA編程語言的入門教程

FPGA編程語言的入門教程

評論