模塊的調用(上層模塊對底層模塊的調用)

在做模塊劃分時,通常會出現這種情形,某個大的模塊中包含了一個或多個功能子模塊,verilog是通過模塊調用或稱為模塊實例化的方式來實現這些子模塊與高層模塊的連接的

調用模塊實例化的一般形式為:

<模塊名><參數列表><實例名>(<端口列表>);

其中參數列表是傳遞到子模塊的參數值,參數傳遞的典型應用是定義門級時延。

名稱關聯&位置關聯

定義模塊:module Design(端口1,端口2,端口3...)

位置關聯:

引用時,嚴格按照模塊定義的端口順序來連接,不用標明元模型定義時規定的端口名。

Designu1(u1的端口1,u1的端口2,u1的端口3)

名稱關聯:

引用時用“.”符號,標明原模型定義時規定的端口名:

Designu2(.端口1(u1的端口1), .端口2(u1的端口2), .端口3(u1的端口3) )

eg:

moduleand(C,A,B)input A,B;output C; 位置相關andA1(T3,A,B)名稱相關andA2( .C(T3), .A(A), .B(B))

模塊的調用---參數傳遞

//子模塊moduleDecode(A,F); parameterwidth =1,polarity=1;endmodule//頂層模塊moudle top; wire[3:0] A4; wire[4:0] A5; wire[15:0] F16; wire[31:0] F32; Decode#(4,0) D1(A4,F16);endmodule

ps:在top模塊中引用Decode實例時,可通過參數的傳遞來改變定義時已規定的參數值,即通過

#(4,0),實例D1實際引用的是參數width和polarity分別為4與0時的Decode模塊

傳遞參數的另一種方法

module_name#(.parametername(para_value),.parametername(para_value))inst_name(port_map) 實際就為: Decode#(.width(4),.polarity(0))D1(A4,F16)

注意事項

位選擇,如.C(D[0]),C端口接到了D信號的第0bit位;

部分選擇,如.Bus(Din[5:4])

上述類型的合并,如.Addr({A1,A2[1:0]})

懸空端口的處理:

在實例化中,可能有些管腳沒用到,可在映射中留白處理

DFF d1(.Q(QS),.Qbar(),.Data(D),.Preset(),//該管腳懸空.clock(CK); )

PS:輸入管腳懸空,該管腳輸入為高阻Z,輸出管腳懸空,該管腳廢棄不用

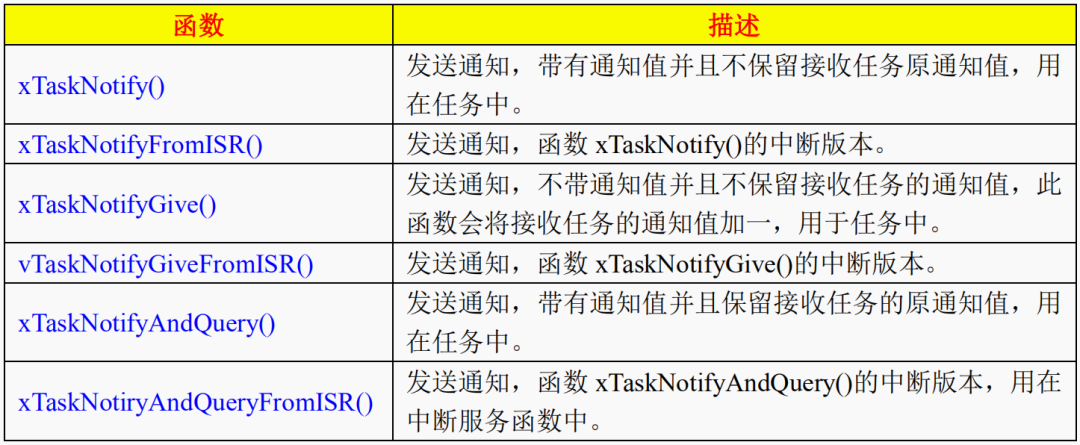

任務和函數

task和function語句分別用來由用戶定義任務和函數;

任務和函數往往時大的程序模塊中在不同地點多次用到的相同的程序段

利用任務和函數可將一個很大的程序模塊分解為許多較小的任務和函數,便于理解和調試

任務定義

task<任務名>; 端口及數據類型聲明語句; 其他語句;endtask

任務調用

<任務名>(端口1,端口2,......);

task語句

任務的定義與調用必須在一個module模塊內

任務被調用時,需列出端口名列表,且必須與任務定義中的I/0變量一一對應

一個任務可以調用其他任務和函數

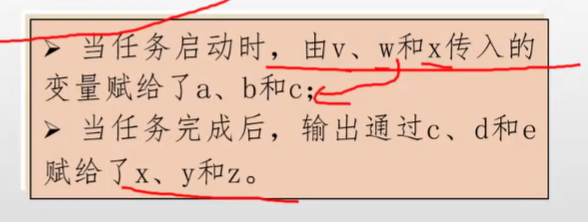

//任務定義task my_task; input a,b; inoutc;//一個三態門,由一個開關控制這個門是輸入還是輸出 output d,e; ...... <語句>//執行任務工作相應的語句 ..... c = foo1; d = foo2; e = foo3;//對任務變量進行賦值endtask//任務調用my_task(v,w,x,y,z)//為位置關聯,v對應a,w對應b,c對應x,y對應d,z對應e

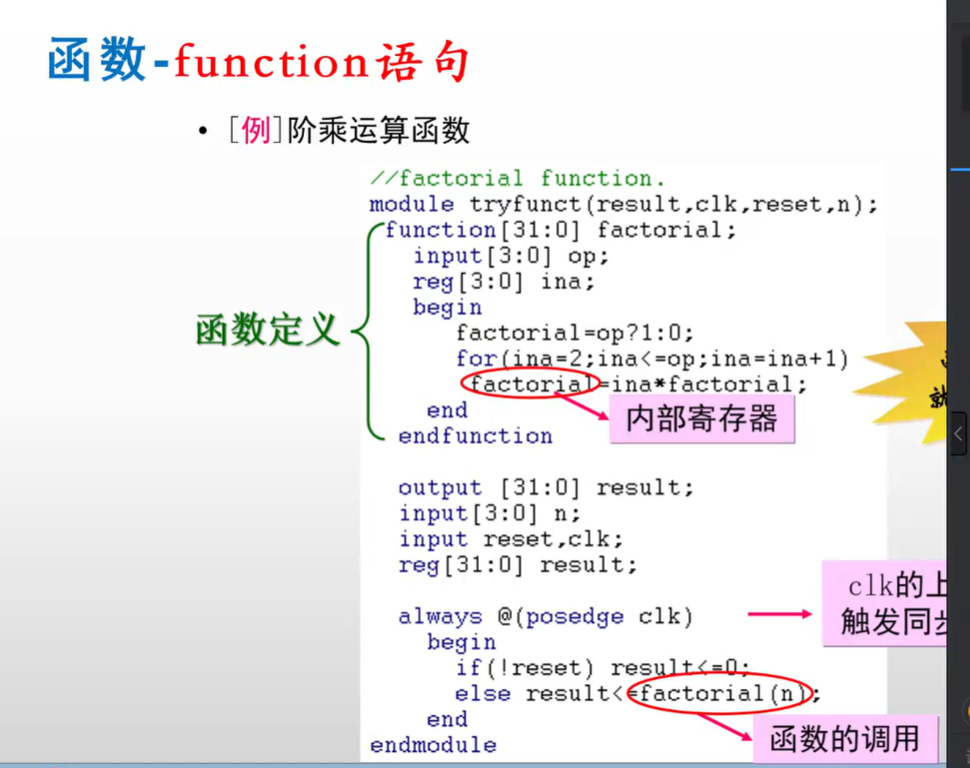

函數function(可以綜合)

函數的目的是通過返回一個用于某表達式的值,來響應輸入信號(適于對不同變量采取同一運算的操作)

函數在模塊內部定義,通常在本模塊中調用,也能根據按模塊層次分級命名的函數名從其他模塊調用。而任務只能在同一模塊內定義與調用

function<返回值位寬或類型說明>函數名;//如缺少位寬定義,則默認為一 端口聲明; 局部變量定義; 其他語句;endfunction

函數的調用 <函數名>(<表達式><表達式>)

注:函數的調用是通過將函數作為調用函數的表達式中的操作數來實現的

函數規則

函數不能包含任何時間控制的語句,如#,@,wait,poesdge,negedege

函數不能調用任務,因為任務可以包含時間控制語句,但是可以調用其他函數

函數應該至少有一個輸入

函數不能有非阻塞性的賦值或force....release或assign...deassign

函數不能有任何觸發器

函數不能有output或inout

函數的聲明:

function[7:0] sum; input[7:0] a, b; begin sum = a + b; endendfunctionfunction[7:0] sum (input[7:0] a, b); begin sum = a + b; endendfunction———————————————— 版權聲明:本文為CSDN博主「李銳博恩」的原創文章,遵循CC4.0BY-SA版權協議,轉載請附上原文出處鏈接及本聲明。 原文鏈接:https://blog.csdn.net/Reborn_Lee/article/details/107447734

函數的調用:

reg [7:0]result; reg [7:0] a, b;initialbegin a=4; b=5; #10result=sum(a, b);end

利用一個函數對一個8位二進制數中為0的位進行計數

//count the numbers of 0 in rega[7:0]modulecount_0 (numbers,rega); output[7:0] numbers; input[7:0] rega; function[7:0] get_n_of_0;//define a function input[7:0] x; reg[7:0] count; integeri; begin count =0; for(i=0;i<=7;i++) ? ? ? ? ? ? ? ? ? ??if(x[i] ==?1'b0) ? ? ? ? ? ? ? ? ? ? ? ? ?count = count +1; ? ? ? ? ? ? ? ? ? ? get_n_of_0 = count;?//函數名就相當于輸出變量;? ? ? ? ? ? ? ??end; ? ??endfunctionassign?number = get_n_of_0(rega);endmodule

ps:函數名就相當于輸出變量

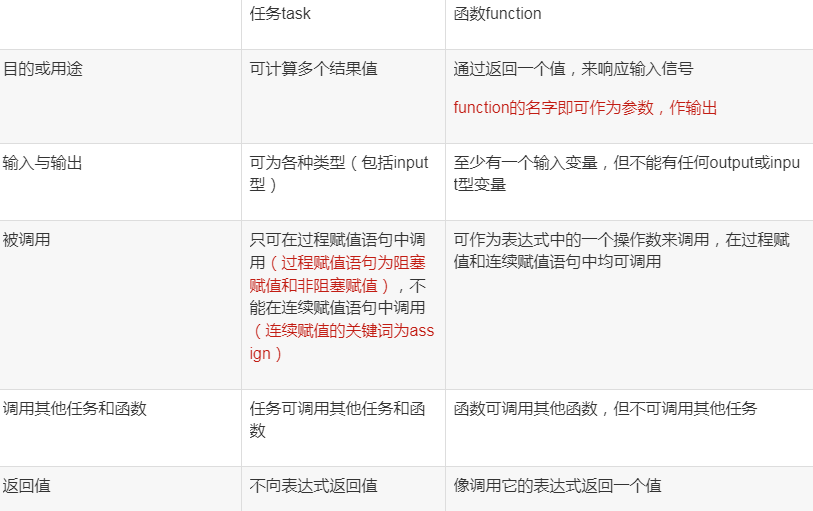

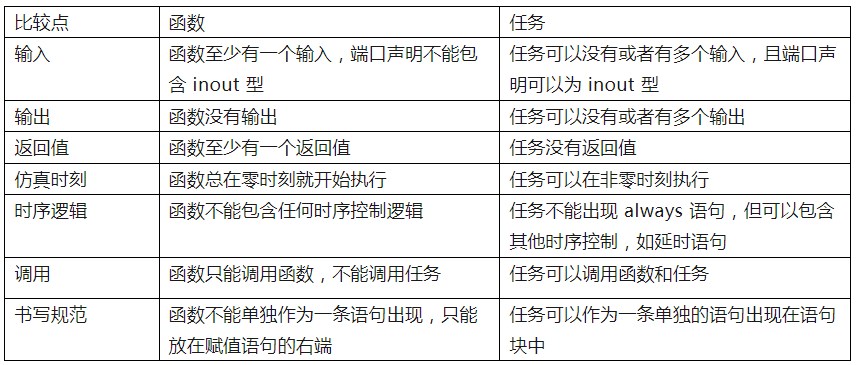

函數和任務

-

模塊

+關注

關注

7文章

2785瀏覽量

49842 -

Verilog

+關注

關注

29文章

1366瀏覽量

111978 -

函數

+關注

關注

3文章

4374瀏覽量

64385

原文標題:verilog---模塊的調用,任務和函數

文章出處:【微信號:gh_9d70b445f494,微信公眾號:FPGA設計論壇】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

如何查看及更改函數/函數塊的調用環境

如何從任務內部調用的函數調用osDelay?

verilog實現定時器函數

Verilog HDL語言中任務與函數的比較

Verilog數字系統設計——任務和函數二(系統任務readmemb或readmemh)

verilog模塊的調用、任務和函數

verilog模塊的調用、任務和函數

評論