同步技術在數字通信系統中是非常重要的技術,一般有位(碼元)同步、字(碼組)同步、載波同步和幀同步,對于網絡系統來說還有網同步。現代SDH數字傳輸網是全網同步的數字傳送網絡,對于接收端的數據處理,首先要從同步數據流中提取幀同步信息,幀同步提取性能的優劣直接影響整個數據的處理質量與整個系統的性能。使用FPGA技術可以實現同步系統的模塊化、小型化和芯片化,得到穩定可靠的幀同步器。

1 并行幀同步系統

SDH中的基本傳輸模塊為STM-1,傳輸速率為155.52Mbps。如果采用傳統的串行幀同步電路,電路需監測接收信號是否與幀同步信號一致,如果不一致則漂移1比特后再次監測是否和幀同步信號一致,如此反復。一邊1比特1比特地漂移,一邊搜索和幀同步信號一致的地方。所以整個邏輯電路要求工作在155.52MHz時鐘頻率,目前的FPGA器件工藝條件下很難得到穩定的工作性能。

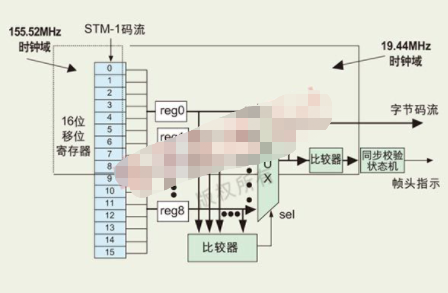

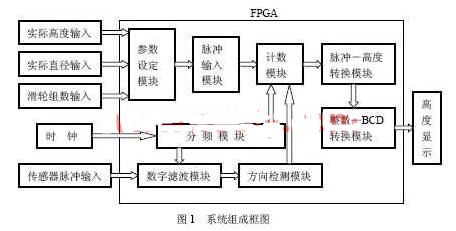

針對這一問題,本文采用并行幀同步法實現STM-1碼流幀同步信息的提取,系統功能框圖如圖1所示。在系統中,只有16比特移位寄存器工作在155.52MHz時鐘頻率,其余模塊工作頻率為STM-1碼流的字節時鐘19.44MHz,從而大大降低了電路時序設計難度,提高了系統的穩定性與可靠性,同時顯著降低了功耗。

圖1:采用并行幀同步法實現STM-1碼流幀同步信息提取的系統功能框圖。

根據ITU-T G.707建議的規定,SDH中采用以字節為基礎的集中插入的幀同步碼組,STM-1幀結構中有6個字節,即48個比特作為幀同步碼組,排列為:第一行的第1列到第六列為A1A1A1A2A2A2(A1=11110110B,A2=00101000B)。為避免使幀同步電路復雜化,沒有必要使用A1、A2的所有字節。根據最壞幀恢復時間參數,這里選取STM-1幀第一行的第3列與第4列16個比特,即相鄰的A1A2字節作為幀同步碼組。

STM-1比特碼流在155.52MHz時鐘控制下串行移入16比特移位寄存器。為了確定輸入串行比特碼流的字節邊界,通過9個并行置數的字節寄存器(reg0~reg8)在19.44MHz時鐘控制下對輸入碼流緩存,其中reg0緩存16比特移位寄存器的第0 比特到第7比特,reg1緩存16比特移位寄存器的第1比特到第8比特,依此類推。緩存后的字節數據經一個9選1的多路選擇器(MUX)構成系統內部的8比特寬數據總線,再由比較器和同步校驗狀態機判斷幀同步情況,產生幀頭指示信號。同時內部數據總線的內容輸出產生時鐘周期為19.44MHz 的STM-1字節碼流,完成對STM-1碼流的串并轉換。

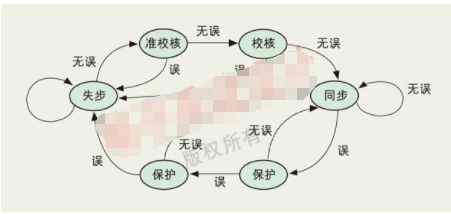

在幀同步方式中定義了失步狀態、準校核狀態、校核狀態、同步狀態和保護狀態五種狀態。狀態轉移圖如圖2所示。

圖2:幀同步系統工作狀態轉移圖

在失步狀態下,系統監測9個緩沖寄存器中的內容是否與A1字節(11110110B)一致。如果一致則進入準校核狀態,表示已找到STM-1碼流的字節邊界,令多路選擇器的輸出(即系統內部數據總線)鎖定為檢測到與A1字節一致的緩沖寄存器的輸出;如果不一致則維持失步狀態。在準校核狀態,如果內部數據總線為A2字節(00101000B)則進入校核狀態,表示已發現一次幀同步碼組;如果內部數據總線為A1字節則維持準校核狀態;否則返回失步狀態。在校核狀態,漂移1個幀長(125μs)再次檢測是否為A1A2字節,如果一致就轉入同步狀態,輸出幀頭指示信號;如果不一致就返回失步狀態。

在同步狀態下,要不斷地漂移1個幀長,檢查是否和幀同步碼組一致。這時,由于誤比特的存在,會發生接收信號和幀同步碼組不一致的情況。因某1次的不一致就由同步狀態轉換為失步狀態的話將會引起偽失步,應避免這種情況的發生。本同步系統在發生1次接收信號和幀同步碼組不一致時,進入保護狀態,只有連續3次不一致才轉換到失步狀態。在保護狀態,如果漂移一個幀長后監測到幀同步碼組,就返回同步狀態;同時在保護狀態也要產生幀頭指示信號。

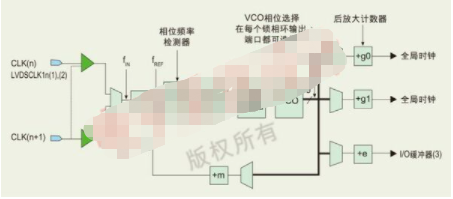

圖3:Cyclone器件內置鎖相環原理框圖。

由于FPGA中寄存器資源豐富,所以狀態機狀態編碼采用獨熱(one-hot)編碼,減少狀態譯碼電路中組合電路的復雜度,便于滿足時序要求和布局布線。在狀態機Verilog代碼編寫時,將狀態轉移單獨寫成一個always模塊,將狀態的操作和判斷寫到另一個always模塊中。與將狀態機的所有邏輯用一個always語句塊描述相比,本設計所采用的代碼風格不僅便于代碼的閱讀、理解、維護,更重要的是利于綜合器優化代碼,利于用戶添加合適的時序約束條件,利于布局布線器實現設計。

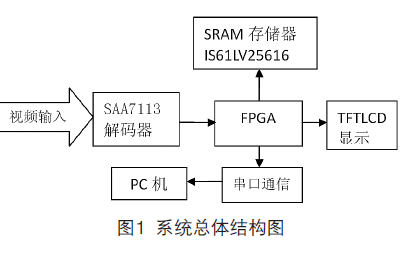

在Altera的低成本的Cyclone系列器件中,有一種經過簡化的快速鎖相環(Fast PLL),可完成時鐘的倍頻、分頻、相移、占空比調整和外部時鐘輸出,能夠利用FPGA內部的全局時鐘網絡進行系統級時鐘管理和時鐘偏移(clock skew)控制,同步內部系統時鐘與片外時鐘,最小化時鐘延遲和時鐘偏移,調整tco(時鐘到輸出時間)和tsu(建立時間)。鎖相環的原理框圖如圖3所示。在Altera公司的QuartusII集成開發平臺中,通過調用可參數化的宏模塊altpll,設置其基本參數就可以得到所需的鎖相環性能,產生系統時鐘信號。

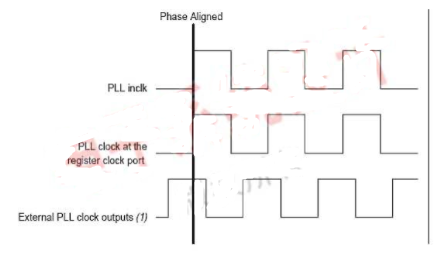

本電路中需要兩個時鐘信號,一個是155.52MHz的STM-1比特時鐘,一個是19.44MHz的STM-1字節時鐘。除16比特移位寄存器工作在155.52MHz時鐘頻率外,整個系統都使用19.44MHz時鐘。所以這里由外部晶振提供19.44MHz高穩定性的全局時鐘信號,由器件內置鎖相環產生8倍頻時鐘信號。這里設置鎖相環工作在Normal模式,反饋路徑補償了輸入晶振時鐘與器件內到達寄存器的時鐘信號之間的布線與邏輯延遲,減小時鐘偏移,保證輸入時鐘與倍頻產生的時鐘之間的穩定相位關系。Normal模式下鎖相環輸入標準時鐘與產生時鐘之間的相位關系如圖4所示。

圖4:Normal模式鎖相環時鐘相位關系圖

2 綜合與驗證

首先使用Altera公司的QuartusII集成開發平臺進行邏輯綜合與靜態時序分析(Static Timing Analysis)。選擇器件型號為Cyclone系列的EP1C6T144C8。由于16比特移位寄存器工作在155.52MHz時鐘頻率下,為了使這部分電路能穩定可靠地工作,在綜合器的設置中必須選擇速度優先的優化技術,并對相關路徑設計嚴格的時序約束條件,同時在布局布線器的設置中選擇物理綜合(Physical Synthesis)優化技術,否則移位寄存器將不能正確地緩存每比特碼流數據。

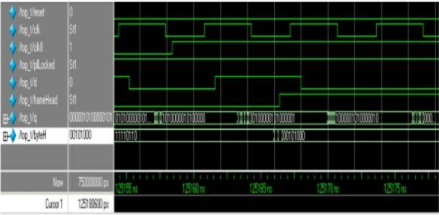

由于QuartusII工具通過NativeLink技術無縫地支持第三方仿真工具,這里采用Mentor Graphics公司的ModelSim工具提取QuartusII產生的Verilog輸出網表文件和標準延時格式(Standard Delay Format)文件,進行RTL級功能仿真與門級時序仿真。由于QuartusII支持的仿真測試向量文件為圖形格式的VWF(Vector Waveform File)文件,不支持Verilog文本測試向量,在測試大型設計項目時,圖形格式測試向量的編寫效率低、可讀性差、不易于修改和維護。而ModelSim作為業界標準的硬件描述語言仿真平臺,支持高效簡潔的Verilog文本測試向量輸入,大大提高了測試向量編寫的有效性和準確性。同時ModelSim的仿真運算速度也遠高于QuartusII集成的仿真工具,可大大縮短系統開發周期,加快設計進程。門級時序仿真得到的波形如圖5所示。

圖5:系統門級仿真波形

圖5中clk8為晶振產生的19.44MHz時鐘,clk為FPGA內置鎖相環8倍頻產生的155.52MHz時鐘,d為輸入的STM-1比特碼流,frameHead信號為產生的幀頭指示信號,byteH為串并轉換后得到的STM-1字節碼流。由圖可知,在連續接收到兩次正確的幀同步碼組后,系統進入同步狀態,輸出幀頭指示信號。

3 本文小結

本文提出了高速率STM-1碼流并行幀同步系統的設計方案,并在實際FPGA器件中實現了物理驗證,得到了穩定可靠的工作電路。這里采用的是將1個串行碼流轉換為8個并行碼流的并行計算技術,對于STM-4、STM-16等更高速率的碼流,可以將串行碼流轉換為更多的并行碼流,系統設計方案無需作大的調整,就可以實現高速碼流的幀同步系統。

責任編輯:gt

-

FPGA

+關注

關注

1646文章

22069瀏覽量

619678 -

寄存器

+關注

關注

31文章

5439瀏覽量

124926 -

通信系統

+關注

關注

6文章

1228瀏覽量

54247

發布評論請先 登錄

基于EP1C6Q240C8的FPGA芯片實現電子測試系統的設計

EP1C3T144 FPGA develop board manual_開發板手冊含原理圖

EP1C3T144_FPGA_develop_board_manual

EP2C5T144C8、EP2C8T144C8、EP2C8Q208C8這三種芯片的區別

EP2C5T144C8、EP2C8T144C8、EP2C8Q208C8這三種芯片的區別

如何采用EP1C3T144實現語音密碼鎖系統的設計

基FPGA Cyclone II_EP2C5 EP2C8的頻

EP2C5T144開發板原理圖

如何使用EP1C6T144C8設計進行FPGA的視頻圖像處理系統詳細資料概述

深入淺出玩轉FPGA視頻:SF-EP1C開發板介紹

基于EP1C6T144C8 FPGA實現STM-1同步系統的應用方案

基于EP1C6T144C8 FPGA實現STM-1同步系統的應用方案

評論