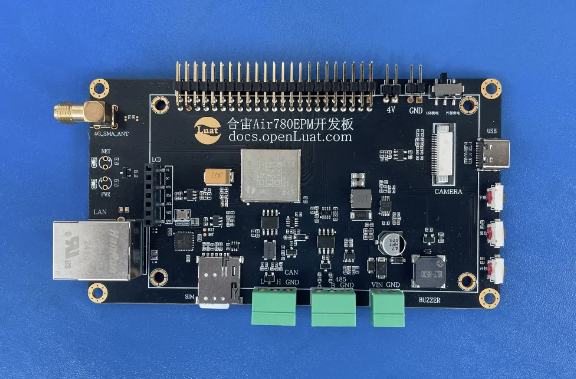

以太網數據傳輸硬件設計實現

系統方案設計

1.1 設計思想

本文研究的是基于FPGA的以太網的MAC層數據處理,目的是能廣泛應用于多種嵌入式網絡設備的前端設計,如網絡視頻監控設備、IP數字電視設備、家庭智能設備等。根據FPGA的可重復擦寫編程的特點,采用FPGA可以方便對設備的升級和維護。本文為了設計能滿足于各種不同的以太網網絡環境,和增強系統的可移植性,采取了一系列的措施。

首先,考慮到以太網高速而又龐大的數據量,尤其是載有音視頻流的1000M網絡,以及開發的成本問題,我們引入了一種針對普通產品開發的Xilinx芯片——Spartan系列。FPGA具有并行執行的特點,相對于其他器件在數據處理上具有明顯的速度上的優勢,同時Spartan系列FPGA擁有幾百Kb甚至幾千Kb的塊RAM資源,可用于數據的緩存,完全可以滿足于1000M以太網數據量的要求。在FPGA的系統設計開發中,常常會采用某些具有特定功能的IP核以提高系統開發的效率,減少成本。考慮到開發周期和設計要求,本系統設計方案采用Xilinx公司的Tri Mode Ethernet MAC IP核實現對MAC數據的主要處理工作,該IP核支持多種工作模式,同時用戶可以根據要求實現自定義配置。其次,為了實現網絡的IP地址和MAC地址的自動映射,本系統還增加了對ARP數據包的解析和ARP應答功能的設計。除此之外,為了提高系統的通用性,物理芯片需能夠支持1000/100/10M以太網、雙工/半雙工工作模式以及1000M光纖的接入。

1.2 系統功能

根據以述的設計思想,為了滿足大部分設備對以太網的MAC數據處理的需求,確定了本系統設計的功能如下:

(1)支持10M/100M/1000M以太網;

(2)支持雙工/半雙工;

(3)CRC校驗和幀長度校驗;

(4)MAC地址濾波;

(5)支持ARP解析;

1.3 系統總體結構設計

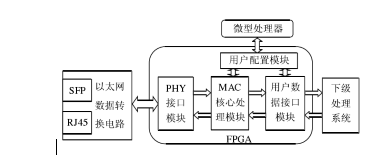

根據上述技術指標及設計思想,圖3-1給出了本系統的總體結構框圖。本系統可分為五大模塊:以太網數據轉換電路、PHY接口模塊、MAC核心處理模塊、用戶配置模塊和用戶數據接口模塊。

圖3-1系統總體結構框圖

(1)以太網數據交換電路

以太網數據交換電路,主要功能是實現雙絞線或光纖電纜的以太網物理層數據與MAC層數據的轉換,為FPGA提供處理的MAC數據源和送出FPGA的上傳MAC數據,是傳輸介質和FPGA數據交流的橋梁。

(2)PHY接口模塊

PHY接口模塊,可分為接收PHY和發送PHY接口兩個子模塊,實現接收數據和發送數據的同步。

(3)MAC核心處理模塊

根據以上設計思想,MAC數據的核心處理模塊直接采用Xilinx的Tri Mode Ethernet MAC IP核,可以完成MAC地址濾波、數據CRC和長度校驗、封裝MAC數據幀格式等基本功能,對接受的數據進行相應的好壞標記和對上傳的數據進行封裝標記。

(4)用戶配置模塊

用戶配置模塊主要是實現主控系統正確地完成對IP核寄存器和系統地址信息(IP地址和MAC地址)的配置,同時實時地監控IP核的工作狀態。該模塊可分為I2C接口和IP核配置兩個子模塊,I2C接口子模塊采用400Kb/s的I2C總線協議,模擬從設備I2C時序;IP核配置子模塊模擬IP核HOST配置時序,以實現對IP核寄存器的配置。

(5)用戶數據接口模塊

用戶數據接口模塊涉及對通過IP核處理后的接收數據幀和待上傳的數據包兩部分數據的處理以及ARP功能的實現,可分為接收數據用戶接口、上傳數據用戶接口、ARP解析與應答三個子模塊。

芯片的選取

2.1 物理層芯片選擇

以太網物理層的處理工作大多數直接采用專業的物理層芯片來完成,完成數據的物理層編解碼和收發功能。目前,物理層芯片的生產商以國外為主,如Marvell、NS、Broadcom公司等,其主流產品為100/10M和1000M物理層芯片,隨著以太網的速率的提高,萬兆物理層芯片也被廣泛應用于光纖以太網。國內對芯片的研發起步比較晚,華為、中興、天津中晶微電子等企業近些年也推出了不少的產品,但是技術還有待發展。

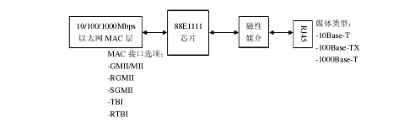

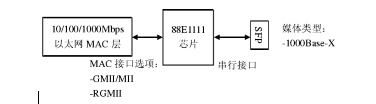

88E1111芯片是Marvell公司Alaska系列的一款千兆以太網收發器,主要應用于10Base-T、100Base-TX、1000Base-T的以太網,采用CMOS工藝,能實現基于CAT5非屏蔽雙絞線標準的以太網物理層數據的收發。88E1111支持多種MAC接口模式,有GMII/MII、RGMII、SGMII、TBI和RTBI,是一款應用廣泛的以太網物理層芯片。

88E1111芯片采用了Marvell公司的VCT(Virtual Cable Tester,虛擬電纜測試儀)功能,可以使用時域反射技術遠程測試電纜故障,減少了設備應答和服務請求的次數,同時還能通過VCT檢測線纜潛在的問題和線纜的開路、短路或阻抗不匹配問題,準確度能達到一米。另外,88E1111芯片具有先進的混合信號處理能力,可以以1Gbps的速率完成自適應均衡、消除反射或串擾、數據恢復、誤碼糾正等功能,是一款抗噪聲能力強的低功耗以太網物理層芯片。

88E1111芯片中嵌入了一個可選的1.25GHzSERDES(并串轉換/串并轉換器),可以直接與光纖收發器連接,實現1000Base-X光纖標準與1000Base-T雙絞線標準傳輸媒體的轉換。通過選擇,88E1111可以通過RJ45接口接入1000Base-T雙絞線網絡或SFP(小型可插拔)模塊接入光纖網絡,分別如圖3-2和3-3所示。

圖3-2 88E1111接入雙絞線網絡

圖3-3 88E1111接入光纖網絡

除了以上所述,88E1111芯片還支持光纖與銅線自動檢測、網絡連接的自動協商、可編程的LED驅動等功能,方便了用戶對以太網接入的開發。

根據本文系統設計的功能的要求,以太網物理層芯片需滿足同時支持RJ45和SFP兩種接口,10Base-T、100Base-TX、1000Base-T標準雙絞線和千兆光纖介質的傳輸,半雙工和雙工切換的工作模式。Marvell公司的以太網物理層芯片88E1111,采用0.13μm的CMOS工藝,是一款低成本、低功耗的千兆以太網物理層芯片,足以滿足系統設計的要求

2.2 FPGA主芯片選擇

在FPGA的開發設計中,FPGA芯片的選取非常重要,不合理的選取會導致一系列的后續設計問題,甚至會失敗;合理的選取不僅避免設計問題,而且可以提高系統的性價比,延長產品的生命周期。通常,FPGA芯片選取需從芯片的供貨商和開發工具的支持、電氣接口標準、硬件資源、速度等級、溫度等級、封裝形式、價格七個方面入手。

(1)供貨商和開發工具的支持

目前,主要的FPGA供應商有Xilinx公司、Altera公司、Lattice公司和Actel公司等,FPGA的發展迅速,器件的淘汰率隨之提高,為了延長產品的生命周期,最好選擇貨源比較足的主流器件。

從開發工具來看,Xilinx公司的ISE和Altera公司的QuartusⅡ,更新及時、功能強大、界面友好,支持本公司所有器件的設計開發和很多第三方軟件的應用,如Synplify Pro、ModleSim等,能將器件的性能發揮到最佳。因此,一般在沒有特殊要求情況下,器件從這兩家公司中選取。

雖然Altera公司的開發智能程度相對Xilinx公司要高一些,但Xilinx公司具有更強的硬件功能,通過IP核的使用可以達到更高的效率。目前,Xllinx公司的主流器件有Spartan-3、Spartan-3A/3ADSP/3AN、Virtex-4LX、Virtex-4SX、Virtex-4FX、Virtex-5LX、Virtex-5SX、Virtex-5FX、Spartan-6和Virtex-6等系列,其中Spartan-3系列主要應用于邏輯設計;Spartan-3A/3ADSP/3AN主要應用于簡單數字信號處理,Virtex-4LX和Virtex-5LX系列主要應用于高速邏輯設計,Virtex-4SX和Virtex-5SX系列主要應用于高速復雜數字信號處理,Virtex-4FX和Virtex-5FX系列主要應用于嵌入式系統。本設計只需要對MAC數據幀做簡單的邏輯處理和緩存等等,Spartan-3系列器件足以滿足這一需求。

(2)芯片的電氣接口標準

目前,數字電路的電氣接口標準非常多,在某些大型的系統設計中常常需要同時支持多種電氣接口標準。本設計中的FPGA的接口電氣標準只采用了LVCMOS2.5V和LVCMOS3.3V,Xilinx公司的絕大部分器件均能夠滿足。

(3)硬件資源

硬件資源是FPGA芯片選取的重要指標,包括邏輯資源、I/O資源、布線資源、存儲器資源和某些底層內嵌功能單元和內嵌專用硬核等。在FPGA設計中,I/O資源和邏輯資源的需求是最需要重點考慮的問題。邏輯資源一般要求消耗的資源不超過70%,主流FPGA器件中,邏輯資源都比較豐富,比較容易選擇。I/O資源需要注意的是避免過度的消耗,因為過度的消耗可能會導致FPGA負荷過重,器件發熱量過大,以影響器件的速度性能、工作穩定性和壽命,設計中也要充分考慮器件的散熱問題。另外,局部布線資源也要充足,以免影響電路的運行速度。在一些特殊場合,特別是數據量比較大的情況下,還得考慮存儲器資源,如BRAM或LUT資源。還有鎖相環、DSP等底層內嵌功能單元或內嵌專用硬核可以根據具體的設計作為參考需求。

(4)速度等級

對于芯片速度等級的選取,有一個基本原則:在滿足應用需求的情況下,盡量選擇速度等級低的芯片。因為速度等級高的芯片更容易產生信號反射,增加價格成本,延長開發周期。本設計的主時鐘最高位125M,XC3S400芯片具有-4和-5兩個速度等級,-4等級的最高可以達到250M,為節約成本,選取的芯片采用-4等級。

硬件電路設計

3.1 以太網變換電路設計

以太網數據變換電路,實現的是以太網傳輸媒介上的物理層數據與MAC層數據的轉換,為FPGA提供待處理的MAC數據源和輸出待上傳的MAC數據,本設計主要是選擇物理層專業芯片88E1111完成這一功能,其電路設計包括以下幾個方面:

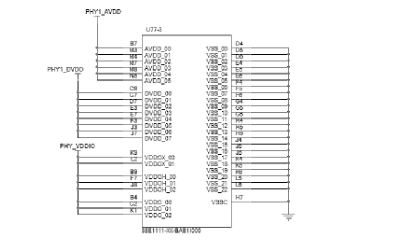

88E1111芯片支持兩種電平:2.5V和1.0V,有時也可用1.2V代替1.0V。如圖3-4所示為芯片的電源電路圖,PHY_VDDIO采用2.5V,為芯片I/O引腳供電,與芯片引腳VDDO、VDDOH、VDDOX相連;PHY1_AVDD提供內部模擬邏輯電平,為2.5V,與AVDD引腳相連;PHY1_DVDD提供內部數字邏輯電平

圖3-488E1111芯片電源電路

為1.0V,與DVDD引腳相連。為了提高電源的穩定性,電源PHY_VDDIO、

PHY1_AVDD、PHY1_DVDD需接入一些濾波電容,以減少電源噪聲。

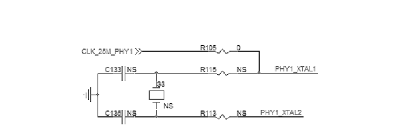

88E1111芯片對數據的處理需要有一個參考時鐘,一般通過XAT1引腳輸入25M或125M的參考時鐘,或通過XAT1和XAT2直接接一個晶振。本設計采用XAT1引腳輸入25M的時鐘,以減少晶振的使用數量,如圖3-5所示,CLK_25M_PHY1與XAT1引腳相連,提供25M的時鐘;為了保證電路的可調性,同時在XAT1和XAT2的兩端添加一個晶振,作為參考時鐘的備用方案。

圖3-588E1111芯片時鐘電路

(2)配置電路設計

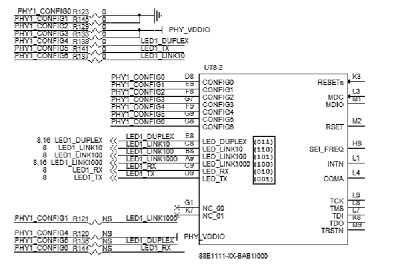

在88E1111的芯片設計中,器件物理地址、PHY操作模式、自動協商模式、MDI(Media Dependent Interface,媒介相關接口)交叉功能、PHY接口模式等的配置需通過芯片CONFIG0~CONFIG6引腳硬件配置來實現,CONFIG0~CONFIG6引腳配置位映射關系表和各配置寄存器的定義描述分別如表3-3和表3-4所示。

在硬件電路設計中,CONFIG0~CONFIG6配置位的選擇通常是通過與LED輸出引腳、VDDO或者VSS引腳的連接來完成的,其各引腳與配置位的映射關系如表3-5所示。

為了方便開發設計,本設計將芯片地址設置為00000,屏蔽PAUSE幀,同時使能MDI交叉連接、光纖與銅線接入自動識別、能量檢測功能,其自動協商支持所有網路模式;125MHz的數據發送的參考時鐘由FPGA提供,125MHz時

表3-3CONFIG0~CONFIG6引腳配置位映射關系表

| 引腳 | Bit[2] | Bit[1] | Bit[0] |

| CONFIG0 | PHYADR[2] | PHYADR[1] | PHYADR[0] |

| CONFIG1 | ENA_PAUSE | PHYADR[4] | PHYADR[3] |

| CONFIG2 | ANEG[3] | ANEG[2] | ANEG[1] |

| CONFIG3 | ANEG[0] | ENA_XC | DIS_125 |

| CONFIG4 | HWCFG_MODE[2] | HWCFG_MODE[1] | HWCFG_MODE[0] |

| CONFIG5 | DIS_FC | DIS_SLEEP | HWCFG_MODE[3] |

| CONFIG6 | SEL_TWSI | INT_POL | 75/60OHM |

表3-4各配置寄存器定義描述

| 配置寄存器 | 定義描述 |

| PHYADR[4:0] | 器件的物理地址,在MDC/MDIO配置模式下,表示器件五位的物理件地址;在I2C配置模式下,表示器件物理地址phyaddr[4:0],phyaddr[6:5]固定為10。 |

| ENA_PAUSE | PAUSE 幀使能信號,高有效;同時影響寄存器4 的默認值 |

| ANEG[3:0] | 自動協商模式配置寄存器,10/100/1000Base-T模式下由ANEG[3:0]配置決定,而1000Base-X模式下由ANEG[3:2]配置決定,具體的配置映射關系可參考88E1111芯片手冊。 |

| ENA_XC | 交叉連接使能信號,1時MDI交叉功能有效,反之則無效。 |

| DIS_125 | 125MHz時鐘使能信號,0使能。 |

| HWCFG_MODE[3:0] | 硬件配置模式,決定了PHY接口模式,常用的有:1000Base-X模式下RGMII為0011;1000Base-X模式下GMII 為0111;10/100/1000Base-T模式下RGMII為1011;10/100/1000Base-T模式下RGMII為1111;其他的模式配置可參考88E1111芯片手冊 |

| DIS_FC | 光纖與銅線接入自動識別使能信號,0有效。 |

| DIS_SLEEP | 能量檢測使能信號,0有效。 |

| SEL_TWSI | 寄存器配置模式選擇,0表示采用MDC/MDIO配置模式,1表示采用I2C配置模式。 |

| INT_POL | 中斷電平值,0表示高電平中斷,1表示低電平中斷。 |

| 75/60 OHM | 終端電阻匹配選擇信號,主要用于光纖接入模式下,0采用50OHM,1采用75OHM。 |

表3-5各引腳與配置位的映射關系

| 引腳 | Bit[2:0] |

| VDDO | 111 |

| LED_LINK10 | 110 |

| LED_LINK100 | 101 |

| LED_LINK1000 | 100 |

| LED_DUPLEX | 011 |

| LED_RX | 010 |

| LED_TX | 001 |

| VSS | 000 |

鐘輸出設置為無效;IPQAM項目的CPU對從設備的寄存器配置采用的是I2C總線方式,因此88E1111需配置成I2C從模式;PHY接口采用GMII/MII模式,減少FPGA對時鐘的時序要求。因此,如圖3-6配置電路圖所示,默認情況下將CONFIG0~CONFIG6引腳分別配置為000、000、111、111、111、001、110。但是為了系統的升級維護,對CONFIG1、CONFIG4、CONFIG5、CONFIG6引腳設置了配置保留值,根據不同的需求本系統可以支持PAUSE幀的傳輸、RGMII的PHY 接口、MDC/MDIO寄存器配置等工作模式。

圖3-6 88E1111配置電路

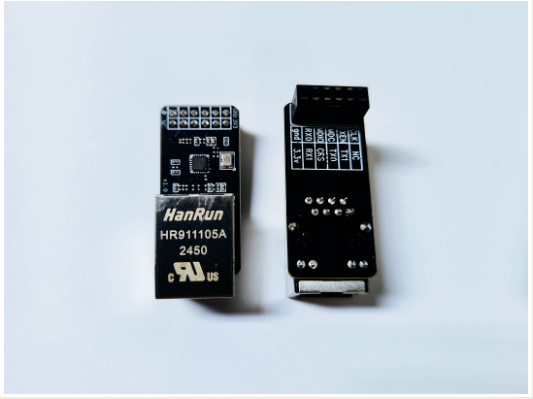

(3)RJ45接口和SFP接口電路設計

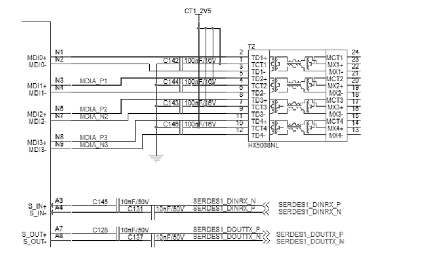

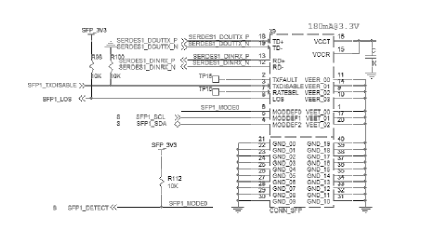

本系統支持普通雙絞線和光纖兩種媒介接入方式,雙絞線的接入采用通用的RJ45接口,其電路圖如圖3-7所示,88E1111芯片的四對MDI引腳直接與HX5008NL芯片的四對TD引腳相連,實現與RJ45接口的連接,完成雙絞線與88E1111芯片的數據交換;光纖的接入采用SFP接口,其電路圖如圖3-8所示,88E1111芯片的S_IN±引腳與SFP接口芯片的RD±引腳相連,接收光纖電纜上的數據;S_OUT±引腳與TD±引腳相連,完成本地的數據的輸出;同時SFP接口芯片采用I2C配置模式,與系統設計一致。

圖3-7 RJ45接口電路

圖3-8 SFP接口電路

責任編輯:lq6

-

FPGA

+關注

關注

1646文章

22069瀏覽量

619623 -

以太網

+關注

關注

41文章

5704瀏覽量

176408 -

數據傳輸

+關注

關注

9文章

2026瀏覽量

66172

原文標題:以太網數據傳輸硬件設計實現

文章出處:【微信號:gh_9d70b445f494,微信公眾號:FPGA設計論壇】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

釋放無限可能!支持WAN和LAN,以太網功能兩種用法隨心用!

一文讀懂~ 源碼開放:Air8101快速實現以太網功能!

怎樣去設計一種基于FPGA的以太網數據傳輸硬件?

怎樣去設計一種基于FPGA的以太網數據傳輸硬件?

評論