接上一篇......

GNN加速器頂層架構(gòu)

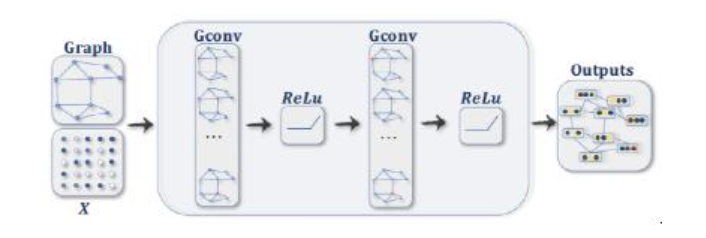

此GNN加速器是為GraphSAGE算法設(shè)計(jì)的,但是它的設(shè)計(jì)也可以應(yīng)用于其他類似的GNN算法加速。其頂層架構(gòu)如下圖所示。

該架構(gòu)由以下模塊組成:

圖中的GNN內(nèi)核是算法實(shí)現(xiàn)的核心部分(詳情如下)。

RoCE-Lite是RDMA協(xié)議的輕量級(jí)版本,用于通過(guò)高速以太網(wǎng)進(jìn)行遠(yuǎn)程存儲(chǔ)訪問,以支持海量節(jié)點(diǎn)的圖計(jì)算。

400GE以太網(wǎng)控制器用于承載RoCE-Lite協(xié)議。

GDDR6存儲(chǔ)器用于存儲(chǔ)GNN處理過(guò)程中所需的高速訪問數(shù)據(jù)(DDR4作為備用大容量存儲(chǔ)器)。該存儲(chǔ)器用于存儲(chǔ)訪問頻率相對(duì)較低的數(shù)據(jù),例如待預(yù)處理的圖形數(shù)據(jù)。

PCIeGen5 ×16 接口提供高速主機(jī)接口,用于與服務(wù)器軟件進(jìn)行數(shù)據(jù)交互。

上述所有模塊均通過(guò)具有高帶寬的NoC實(shí)現(xiàn)互連。

GNN內(nèi)核微架構(gòu)

在開始討論GNN內(nèi)核的微架構(gòu)之前,有必要先回顧一下GraphSAGE算法。其內(nèi)層循環(huán)的聚合和合并(包括卷積)占據(jù)了該算法的大部分計(jì)算和存儲(chǔ)訪問。通過(guò)研究,我們得出這兩個(gè)步驟的特點(diǎn),具體如下。

表2:GNN算法中聚合和合并操作的對(duì)比(來(lái)源:https://arxiv.org/abs/1908.10834)

| 步驟 | 聚合操作 | 合并操作 |

| 存儲(chǔ)訪問方式 | 間接訪問,不規(guī)則 | 直接訪問,規(guī)則 |

| 數(shù)據(jù)重用 | 低 | 高 |

| 計(jì)算模式 | 動(dòng)態(tài),不規(guī)則 | 靜態(tài),規(guī)則 |

| 計(jì)算量 | 低 | 高 |

| 性能瓶頸 | 存儲(chǔ) | 計(jì)算 |

可以看出,聚合操作和合并操作在計(jì)算和存儲(chǔ)訪問模式上有著完全不同的需求。聚合操作涉及相鄰節(jié)點(diǎn)的采樣。然而,圖形是一種非歐幾里得數(shù)據(jù)類型——它的大小和維度是不確定且無(wú)序,矩陣稀疏,節(jié)點(diǎn)位置隨機(jī)。因此,存儲(chǔ)訪問是不規(guī)則的,并且難以重復(fù)利用數(shù)據(jù)。

在合并操作中,輸入數(shù)據(jù)是聚合結(jié)果(節(jié)點(diǎn)的低維表示)和權(quán)重矩陣。它的大小和維度是固定的,具有線性存儲(chǔ)位置。因此對(duì)存儲(chǔ)訪問沒有挑戰(zhàn),但是矩陣的計(jì)算量非常大。 基于上述分析,我們決定在GNN內(nèi)核加速器設(shè)計(jì)中選擇使用兩種不同的硬件結(jié)構(gòu)來(lái)分別處理聚合和合并操作(如下圖示):

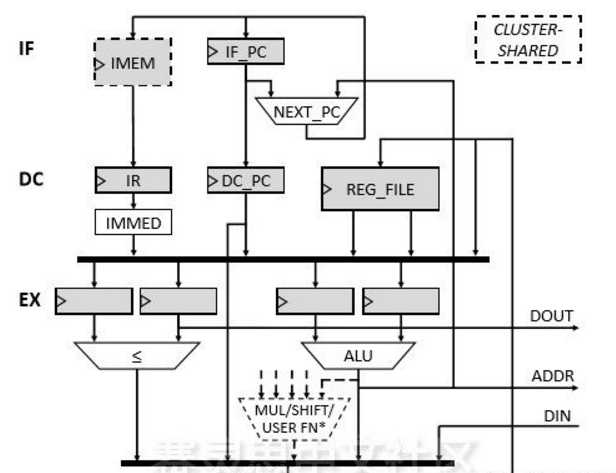

聚合器——通過(guò)單指令多數(shù)據(jù)(SIMD)處理器陣列,對(duì)圖形相鄰節(jié)點(diǎn)進(jìn)行采樣和聚合。單指令可以預(yù)定義為mean()平均值計(jì)算,或其他適用的聚合函數(shù);多數(shù)據(jù)是指單次mean()均值計(jì)算中需要多個(gè)相鄰節(jié)點(diǎn)的特征數(shù)據(jù)作為輸入,這些數(shù)據(jù)來(lái)自子圖采樣器。SIMD處理器陣列通過(guò)調(diào)度器Agg Scheduler進(jìn)行負(fù)載平衡。子圖采樣器通過(guò)NoC從GDDR6或DDR4讀回的鄰接矩陣和節(jié)點(diǎn)特征數(shù)據(jù)h0v分別緩存在鄰接列表緩沖區(qū)(Adjacent ListBuffer)和節(jié)點(diǎn)特征緩沖區(qū)(Node Feature Buffer)。聚合的結(jié)果hkN(v)存儲(chǔ)在聚合緩沖區(qū)(Aggregation Buffer)中。

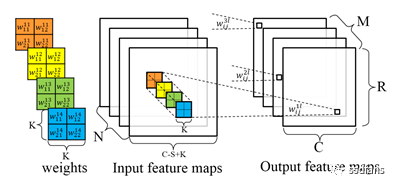

合并器——通過(guò)脈動(dòng)矩陣PE對(duì)聚合結(jié)果進(jìn)行卷積運(yùn)算。卷積核是Wk權(quán)重矩陣。卷積結(jié)果由ReLU激活函數(shù)進(jìn)行非線性處理,同時(shí)也存儲(chǔ)在PartialSum Buffer中,以用于下一輪迭代。

合并結(jié)果經(jīng)過(guò)L2BN標(biāo)準(zhǔn)化處理后,即為最終的節(jié)點(diǎn)表示hkv。在一個(gè)典型的節(jié)點(diǎn)分類預(yù)測(cè)應(yīng)用中,節(jié)點(diǎn)表示hkv可以通過(guò)一個(gè)全連接層(FC)來(lái)獲取節(jié)點(diǎn)的分類標(biāo)簽。這個(gè)過(guò)程是傳統(tǒng)的機(jī)器學(xué)習(xí)處理方法之一,在GraphSAGE文獻(xiàn)資料中沒有體現(xiàn),這個(gè)功能也沒有包含在這個(gè)架構(gòu)中。

責(zé)任編輯:haq

-

FPGA

+關(guān)注

關(guān)注

1645文章

22034瀏覽量

617848 -

加速器

+關(guān)注

關(guān)注

2文章

827瀏覽量

39085 -

GNN

+關(guān)注

關(guān)注

1文章

31瀏覽量

6551

原文標(biāo)題:白皮書:一種基于FPGA的圖神經(jīng)網(wǎng)絡(luò)加速器解決方案(WP024)(第二部分)

文章出處:【微信號(hào):Broadcom_China,微信公眾號(hào):博通Broadcom】歡迎添加關(guān)注!文章轉(zhuǎn)載請(qǐng)注明出處。

發(fā)布評(píng)論請(qǐng)先 登錄

數(shù)據(jù)中心加速器就看GRVI Phalanx FPGA加速器

機(jī)器學(xué)習(xí)實(shí)戰(zhàn):GNN(圖神經(jīng)網(wǎng)絡(luò))加速器的FPGA解決方案

機(jī)器學(xué)習(xí)實(shí)戰(zhàn):GNN加速器的FPGA解決方案

GNN(圖神經(jīng)網(wǎng)絡(luò))硬件加速的FPGA實(shí)戰(zhàn)解決方案

一種基于FPGA的圖神經(jīng)網(wǎng)絡(luò)加速器解決方案

【書籍評(píng)測(cè)活動(dòng)NO.18】 AI加速器架構(gòu)設(shè)計(jì)與實(shí)現(xiàn)

《 AI加速器架構(gòu)設(shè)計(jì)與實(shí)現(xiàn)》+第2章的閱讀概括

高級(jí)語(yǔ)言(HLL)標(biāo)準(zhǔn)擴(kuò)展大大簡(jiǎn)化基于FPGA加速器的應(yīng)用程序的開發(fā)

優(yōu)化基于FPGA的深度卷積神經(jīng)網(wǎng)絡(luò)的加速器設(shè)計(jì)

基于Xilinx FPGA的Memcached硬件加速器的介紹

基于FPGA的SIMD卷積神經(jīng)網(wǎng)絡(luò)加速器

基于FPGA的深度學(xué)習(xí)CNN加速器設(shè)計(jì)方案

Rapanda流加速器-實(shí)時(shí)流式FPGA加速器解決方案

基于FPGA的GNN加速器頂層架構(gòu)

基于FPGA的GNN加速器頂層架構(gòu)

評(píng)論