FIFO 最小深度計算

例子 - 1:f_wr 》 f_rd,連續(xù)讀寫

寫時鐘80MHz。

讀時鐘50MHz。

Burst_Len = 120,也就是要求至少安全寫入120個數(shù)據(jù)。

連續(xù)寫入和連續(xù)讀取,無空閑時間,寫入后立即開始讀取 ,讀寫寬度相同。

Sol:

寫速率 》 讀速率,F(xiàn)IFO遲早會被寫滿,但它要求至少寫入120個數(shù)據(jù)后FIFO不滿。

寫入120個數(shù)據(jù)耗時 120 * 12.5 ns = 1500 ns。

寫入開始后FIFO內數(shù)據(jù)以 30M/Date 速率增加。

數(shù)據(jù)增加持續(xù)了 1500 ns ,F(xiàn)IFO最小深度:0.0000015 * 30000000 = 45

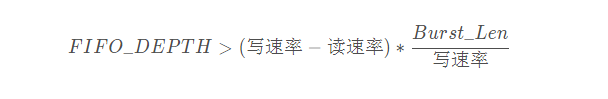

例子-1 總結公式:

例子 - 2 :f_wr 》 f_rd & 寫速率 》 讀速率,非連續(xù)讀寫

寫時鐘80MHz。

讀時鐘50MHz。

Burst_Len = 120,也就是要求至少安全寫入120個數(shù)據(jù)。

寫入后立即開始讀取 ,讀寫寬度相同。

2個時鐘中有1個數(shù)據(jù)寫入(寫速率:80M * 1/2 = 40M)。

4個時鐘中有1個數(shù)據(jù)讀出(讀速率:50M * 1/4 = 12.5M)。

Sol:

FIFO遲早會被寫滿 ,但它要求至少寫入120個數(shù)據(jù)后FIFO不滿。

寫一個數(shù)據(jù)耗時:2/80MHz = 25ns

需要至少寫入120數(shù)據(jù),耗時:25 * 120 = 3000ns

例子2只是讀寫速率和例子1不同,可以直接用的公式(1) :

FIFO_DEPTH 》 (寫速率-讀速率)* Burst_Len/寫速率 = (40M-12.5M)*120/40M = 83

例子 - 3:f_wr 《 f_rd ,連續(xù)讀寫

寫時鐘30MHz。

讀時鐘50MHz。

Burst_Len = 120,也就是要求至少安全寫入120個數(shù)據(jù)。

連續(xù)寫入和連續(xù)讀取,無空閑時間,寫入后立即開始讀取 ,讀寫寬度相同。

Sol:

FIFO_DEPTH 》 1 即可。讀速率比寫速率快,數(shù)據(jù)不會滯留。

例子 -4:f_wr 《 f_rd & 寫速率 》 讀速率,非連續(xù)讀寫

寫時鐘30MHz。

讀時鐘50MHz。

Burst_Len = 120,也就是要求至少安全寫入120個數(shù)據(jù)。

2個時鐘中有1個數(shù)據(jù)寫入(寫速率:30M * 1/2 = 15M)。

4個時鐘中有1個數(shù)據(jù)讀出(讀速率:50M * 1/4 = 12.5M)。

Sol:

雖然寫時鐘小于讀時鐘頻率,但是,宏觀上寫速率大于讀速率。可以直接用的公式(1) :

FIFO_DEPTH 》 (寫速率-讀速率)* Burst_Len/寫速率 = (15M-12.5M)*120/15M = 20

例子 1-4總結

當滿足以下所有條件時,就可使用公式(1):

寫速率 》 讀速率時。

讀寫有效數(shù)據(jù)占比 《= 0.5,且 有效數(shù)據(jù)均勻分布在所有時間上。或者說,無論微觀時間、還是宏觀時間上,讀寫速率近似于 時鐘頻率 * 有效數(shù)據(jù)占比時。

當每100個時鐘寫80個數(shù)據(jù)時,微觀時間上的寫速率與數(shù)據(jù)排列有關,不能將宏觀寫速率帶入式子(1)

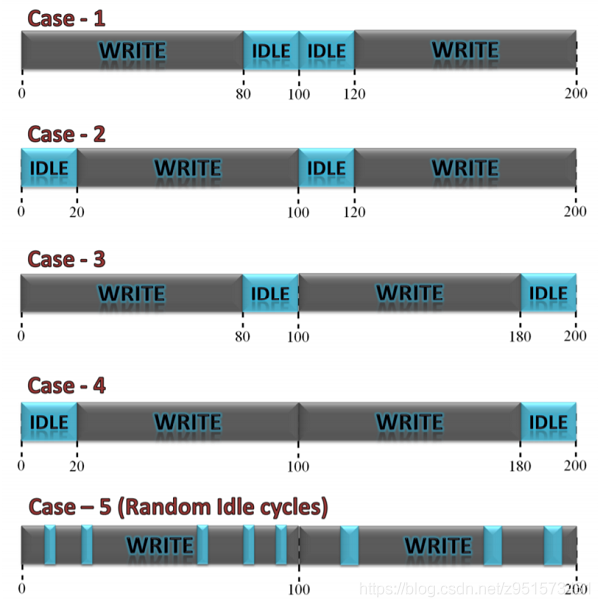

例子 - 5

讀寫時鐘頻率相同。

100個時鐘有80個數(shù)據(jù)寫入。

10個時鐘有8個數(shù)據(jù)讀出。

Burst_Len = 160,也就是要求至少安全寫入160個數(shù)據(jù) 。

Sol:

宏觀上,讀寫速率相同;當FIFO足夠深時,F(xiàn)IFO不會溢出。

微觀上,寫速率有多種情況:

為了求出安全的最小FIFO深度,我們需要考慮最差的情況。

最差的情況下,寫入和讀出速度應該相差最大。寫入要最快,讀出要最慢。FIFO內的數(shù)據(jù)增加最快。

從上表中可得出:最大寫入速率是case 4(back to back write,中間沒有空閑,速率為時鐘頻率 f,寫入了160個 )。

讀出要最慢,在寫160個數(shù)據(jù)期間,讀相比于寫端可以認為是速率均勻的,速率為 f*8/10,讀出了160 * 8 /10 = 128個。

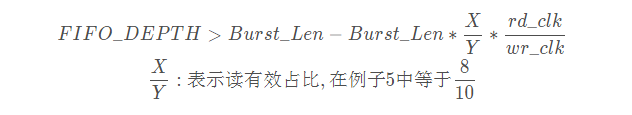

因此 FIFO_DEPTH 》 160 - 128 = 32。用公式(1)也可以得到這個結果,寫速率帶入f而不是f*8/10。

總結:求解步驟

考慮最差的情況下,寫入和讀出速度應該相差最大。寫入要最快,讀出要最慢。FIFO內的數(shù)據(jù)增加最快。

只考慮宏觀上寫入速率 》= 讀出速率的情況。

確定寫入Burst_Len大小。Burst_Len指的是一段連續(xù)寫入?yún)^(qū)間,由于沒有空隙這段時間寫入速率最大最多。一定要對具體的數(shù)據(jù)分布情況具體分析,Burst_Len一定是最長的一段連續(xù)寫入?yún)^(qū)間。

在微觀上,確定最大寫入速率。Burst_Len足夠長時,寫入速率 = 寫時鐘頻率(back to back write)。而在例子 - 2中,Burst_Len很短,沒有back to back write,寫入速率 = 寫時鐘頻率 * 寫有效占比。

在微觀上,確定最小讀出速率。一般認為讀出速率是均勻的,讀出速率 = 讀時鐘頻率 * 讀有效占比。

帶入公式(1)計算。

Burst_Len足夠長時,將上面讀出寫入速率帶入公式(1),可得到網(wǎng)上討論最多的FIFO深度求解公式:

不建議直接用公式(2)無腦計算,上式只有Burst_Len足夠長,發(fā)生back to back write時才適用。建議根據(jù)1~6步驟,判斷微觀寫速率是否均勻,帶入式子(1)計算。

編輯:jq

-

數(shù)據(jù)

+關注

關注

8文章

7242瀏覽量

91039 -

fifo

+關注

關注

3文章

400瀏覽量

44625 -

計算

+關注

關注

2文章

453瀏覽量

39217

原文標題:FIFO 最小深度計算

文章出處:【微信號:gh_9d70b445f494,微信公眾號:FPGA設計論壇】歡迎添加關注!文章轉載請注明出處。

發(fā)布評論請先 登錄

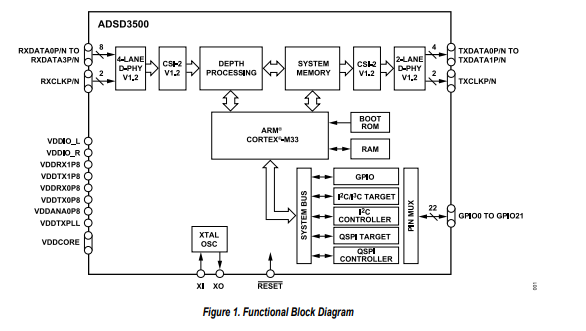

ADSD3500飛行時間深度成像信號處理器技術手冊

智多晶FIFO_Generator IP介紹

AXI接口FIFO簡介

解鎖TSMaster fifo函數(shù):報文讀取的高效方法

RMSL201-1301:高性能刷臉支付解決方案

海光信息技術團隊完成模型與DCU國產(chǎn)化適配

ADS1274最小噪聲電壓為多少啊?

FIFO IP核的使用教程

請問DAC5682z內部FIFO深度為多少,8SAMPLE具體怎么理解?

DAC3482在按字寬度輸入模式下,為啥SYNC信號每16*n個FIFO采樣重復一次?

FIFO的深度應該怎么計算

Efinity FIFO IP仿真問題 -v1

你們知道FIFO最小深度計算嗎

你們知道FIFO最小深度計算嗎

評論