優秀的 Verilog/FPGA開源項目介紹(一)-PCIe通信

今天開始會陸續介紹一些優秀的開源項目,項目基本都是和FPGA或HDL相關的。對于一些找工作或者急需項目經驗的人來說,這些項目都有一定的參考價值。

這里再介紹一下開源協議的區別,方便大家在閱讀使用這些開源項目時尊重規則。

詳情查看:https://suisuisi.blog.csdn.net/article/details/120660472

RIFFA項目

RIFFA(FPGA 加速器的可重用集成框架)是一個簡單的框架,用于通過 PCI Express 總線將數據從主機 CPU 傳送到 FPGA。該框架需要支持 PCIe 的工作站和帶有 PCIe 連接器的板上的 FPGA。RIFFA 支持 Windows 和 Linux、Altera 和 Xilinx,具有 C/C++、Python、MATLAB 和 Java 的綁定。適配Xilinx和Intel的FPGA,支持PCIe 2.0設計中對底層硬件進行了抽象,用戶使用的過程中無需關注底層的硬件,同時上層軟件將PCIe的操作抽象為讀和寫操作,用戶直接調用函數即可。公眾號:OpenFPGA

方便軟件工程師使用:

在軟件方面有兩個主要功能:數據發送和數據接收。這些函數通過 C/C++、Python、MATLAB 和 Java 中的用戶庫公開。該驅動程序支持一個系統中最多5個 FPGA。軟件適用于 Linux 和 Windows 操作系統。用戶只需編寫幾行代碼即可與 FPGA IP 核進行通信。

方便硬件工程師使用:

在硬件方面,用戶訪問一個獨立的發送和接收信號的接口。這些信號提供事務握手和通過 FIFO 接口讀取/寫入數據。不需要了解總線地址、緩沖區大小或 PCIe 數據包格式。只需在 FIFO 接口上發送數據并在 FIFO 接口上接收數據。

RIFFA 不依賴于 PCIe 橋接器,因此不受橋接器實現的限制。相反,RIFFA 直接與 PCIe 端點配合使用,運行速度足以使 PCIe 鏈路飽和。軟件和硬件接口都得到了極大的簡化。詳細信息可以在硬件接口頁面上找到。公眾號:OpenFPGA

RIFFA 使用直接內存訪問 (DMA) 傳輸和中斷信號傳輸數據。這實現了 PCIe 鏈路上的高帶寬。在我們的測試中,我們能夠使所有測試中的鏈路飽和(或接近飽和)。我們已經在 AVNet Spartan LX150T、Xilinx ML605 和 Xilinx VC707 以及 Altera DE5-Net、DE4 和 DE2i 板上實現了 RIFFA。RIFFA 發行版包含在上面列出的三個開發板上設置設計的示例和指南。

此外,該網站還提供了如何從所有軟件綁定訪問您的設計的示例。RIFFA 已經在 Fedora 13 和 17(32/64 位版本)和 Ubuntu Desktop 10.04 LTS 和 12.04 LTS(32/64 位版本)上進行了測試。RIFFA 依賴于 Linux 內核 2.6.27+(在 2.6.32 - 3.3.0 之間的版本上測試)支持的自定義 Linux 內核驅動程序。公眾號:OpenFPGA

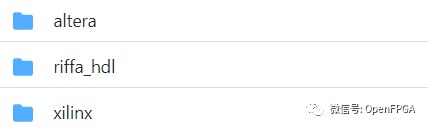

其中FPGA文件夾是我們關心的部分,里面包含了ALtera和XIlinx兩大主流FPGA廠家的幾款主要板卡的DEMO,如下:

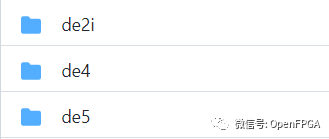

Altera文件夾下:

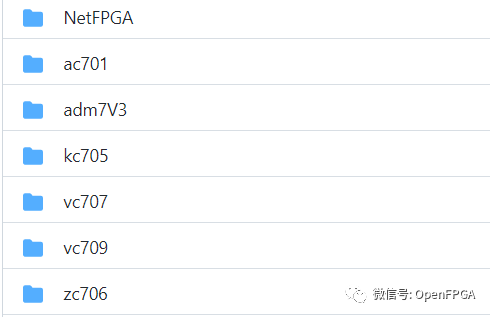

Xilinx文件夾下:

有興趣的可以自己查看使用,項目地址:

https://github.com/KastnerRG/riffa

Alex的眾多項目

Alex的項目可以用驚艷來形容,絕大部分都是個人開發的,都是非常專業的代碼,非常敬佩其專業能力和分享精神,或許這才是真正的詩和遠方。公眾號:OpenFPGA

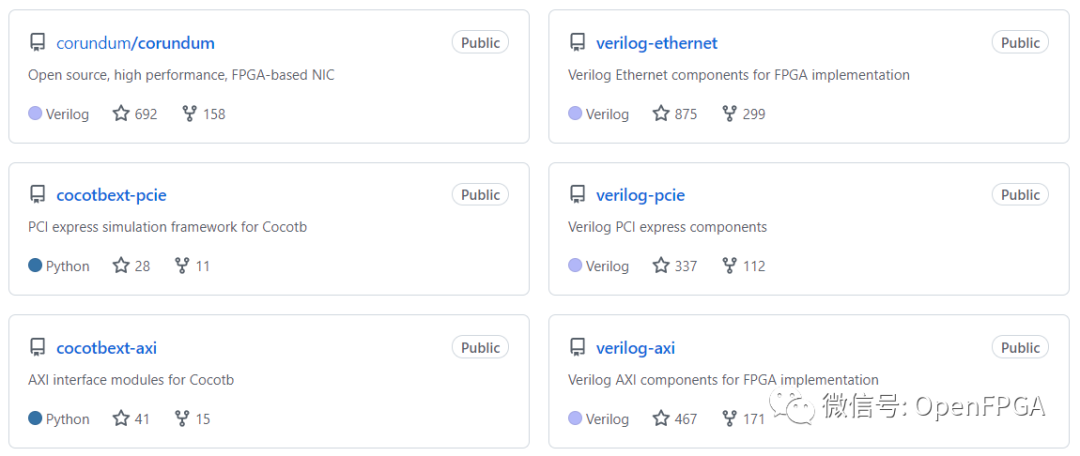

Alex Forencich主要項目

包含網絡和PCIe相關,其中cocotbext-xxx是仿真測試模型(cocotb is a coroutine based cosimulation library for writing VHDL and Verilog testbenches in Python.cocotb是一套基于python的用于構建仿真及測試用例的lib庫)。

其中cocotbext-axi也是一個非常出名的項目。

有興趣的可以自己查看使用,項目地址:

https://github.com/alexforencich

個人感覺Alex Forencich的PCIe項目完成度不如RIFFA,前者目前僅支持與 Xilinx UltraScale 和 UltraScale+ PCIe 硬核 IP 核配合使用,接口介于 64 位和 512 位之間。而后者在Altera及Xilinx很多主要平臺經過驗證,同時配備上位機驅動,方便使用。但是后者的仿真理論(包括使用cocotbext-pcie和 cocotbext- axi 的完整 cocotb 測試平臺 。)更加充實,適合研究總線接口。以上僅代表個人愚見,我讀書少,噴我你就是對的!

本文為OpenFPGA作者原創,未經本人授權禁止轉載!

編輯:jq

-

FPGA

+關注

關注

1646文章

22054瀏覽量

618820 -

PCIe

+關注

關注

16文章

1342瀏覽量

85213 -

C++

+關注

關注

22文章

2119瀏覽量

75363 -

代碼

+關注

關注

30文章

4900瀏覽量

70802 -

python

+關注

關注

56文章

4827瀏覽量

86830

原文標題:Alex的眾多項目

文章出處:【微信號:Open_FPGA,微信公眾號:OpenFPGA】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

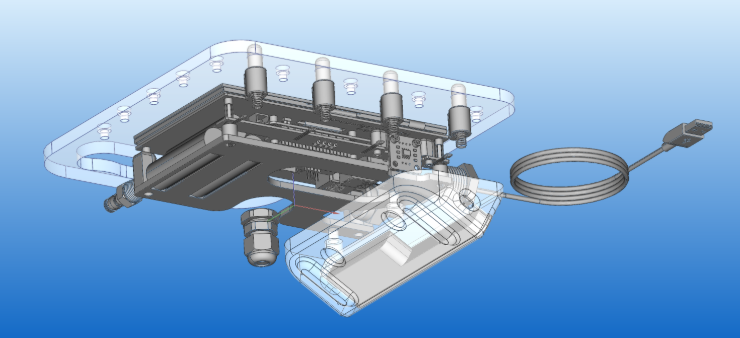

火爆開發中 | 開源FPGA硬件板卡,硬件第一期發布

【開源分享】:開源小巧的FPGA開發板——Icepi Zero

擁抱開源!一起來做FPGA開發板啦!

Open Echo:一個開源的聲納項目

使用IP核和開源庫減少FPGA設計周期

Verilog 測試平臺設計方法 Verilog FPGA開發指南

Verilog vhdl fpga

FPGA加速深度學習模型的案例

ElfBoard開源項目|“智慧光伏”開源項目技術文檔

優秀的 Verilog/FPGA開源項目介紹(一)

優秀的 Verilog/FPGA開源項目介紹(一)

評論