串行總線技術(二)-串行總線中的先進設計理念及SerDes/PMA介紹字節分割/鏈路聚合下面以PCIe為例對字節分割加以討論,如圖所示。

PCIe使用鏈路和線路來發送串行數據。鏈路是一個邏輯實體,能夠具有單個線路或多個線路。當邏輯鏈路包括一個線路時,TLP和DLLP通過單一的線路發送,每次發送一字節。

當鏈路包括多個線路時,TLP和DLLP分布在多個線路中,此時不是在不同的線路中發送不同的TLP而是所有的線路共同發送TLP在一個x4 PCIe鏈路(擁有4條線路)中,第一字節通過線路0、第二字節通過線路1、第三字節通過線路2、第四字節通過線路3、第五字節又回到線路0進行傳輸。這種傳輸機制被稱為字節分割,字節分割在連續的線路上持續進行,直到最后一字節被發送。

正如我們所注意到的,可以通過使用更寬的鏈路來增加帶寬。一個X4鏈路發送數據的帶寬是xl鏈路的4倍。雖然線路是并行使用的,寬鏈路需要更多的引腳,其與并行總線結構也是有本質不同的。

寬鏈路中每個獨立的線路仍然是以串行方式工作的。每個線路都有自己的差分傳輸信號線和獨立的數據恢復電路,都具有串行傳輸所具有的優點。它們是獨立的串行傳輸通道,通過使用字節分割機制合并起來作為一個邏輯實休使用。字節分割是MAC的功能。但是并不是所有的串行協議都使用字節分割,SATA和USB沒有使用字節分割技術。

如果希望增加SATA硬盤的傳輸帶寬,需要使用多個相互獨立的SATA驅動器,使用不同的事務層包 (FIS ) 進行通信,如圖所示。USB也是采用類似的機制,每個USB設備采用單線路連接。

通道綁定與去偏移前而我們討論了字節分割技術,它將一個TLP分布到多個線路中進行傳輸。當接收電路從不同的線路收到這些分布傳輸的數據后,對其正確合路處理會遇到一些實際閑難,在電路板上,不同的傳輸路徑會帶來不同的傳輸延遲。

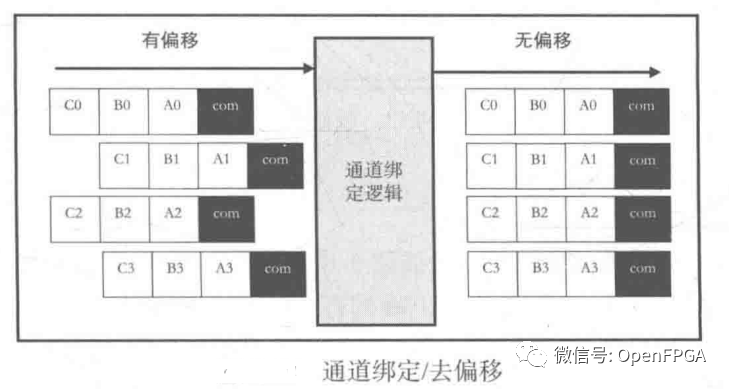

當接收電路收到來自不同線路的數據時,它們經過的延遲存在差異并且處于不同的時鐘域。接收電路需要將不同線路上收到的數據進行級聯,合并得到原始的TLP,此時所接收的數據之間已經失去了發送時相互之間的字節同步關系,需要使用通道綁定技術在接收端重新恢復不同線路之間的字節對準關系,如圖所示。

在所有的線路上傳輸的數據流中有一種特殊的COMMA字符。在鏈路訓練階段,在所打線路上都會發送包含COMMA字符的用于訓練的有序字符集合。與TLP和DLLP不同,訓練字符集合不是以字節分割方式發送的。通道綁定邏輯在1個線路(例如,線路0)中査找COMMA,接著它在其他線路中定位COMMA字符并記錄它們的相對位置。

一旦它鎖定了COMMA字符出現的位置,它就停止搜索COMMA字符并記錄下這些相對位置信息。通道綁定邏輯使用這些相對位置信息來對準存在偏移的接收數據字節流。通道綁定邏輯會始終保持基線路(線路0)字節位置不變。

對于其他線路,它會根據所檢測到的COMMA的相對位置寫入或讀出數據,在此期間這些相對位置信息會保持不變。即使輸入數據相對于通道綁定邏輯發生了延遲偏移,從通道綁定邏輯輸出的數據仍然是對準的,TLP和DLLP能夠被正確處理。

通道綁定也被稱為去延遲偏移操作。通道綁定邏輯通常屬于MAC層功能,只應用于包含多個線路、采用字節分割技術的鏈路中。

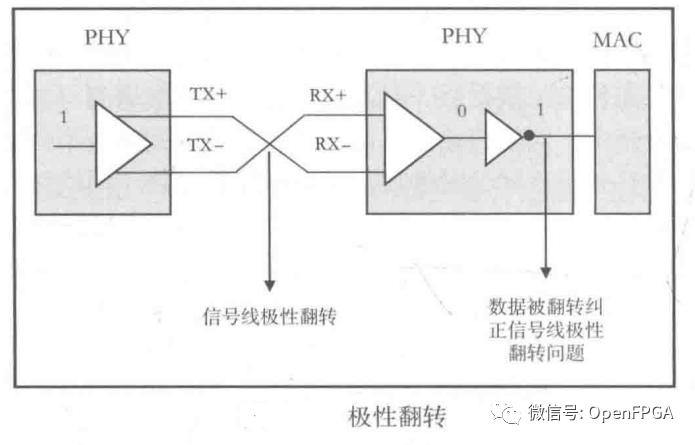

極性翻轉串行數據比特通過TX+和TX-信號線發送。信號線在印制電路板(PCB)上布線時,TX+應該連接收端的RX+,TX-應該連接收端的RX-。但隨著PCB板的層數不斷增加,布線密度不斷增大,走線距離可能較長,有時還可能要通過連接器,所以經常因為疏忽而發生TX+連接收端的RX-、TX-連接收端的RX+的情況。發生這種情況后,有時可以通過重新布線加以解決,但有時重新布線的代價會比較高。

在PCIe中,使用了一種機制來解決極性連接錯誤問題。在鏈路訓練階段,接收端查找常規的訓練練字符集合或者反相的訓練字符集合。如果發生了極性翻轉,那么接收的串行比特會發生逐比特翻轉(1變為0,0變為1)。

如果鏈路訓練邏輯檢測到了逐比特翻轉的訓練字符,那說明出現連線錯誤。發送電路無法獲知是否發生了連接極性錯誤,接收電路檢測到這一錯誤并通過逐比特取反在不進行硬件重新設計和PCB重新加工的情況下解決了這一問題,如圖所示。

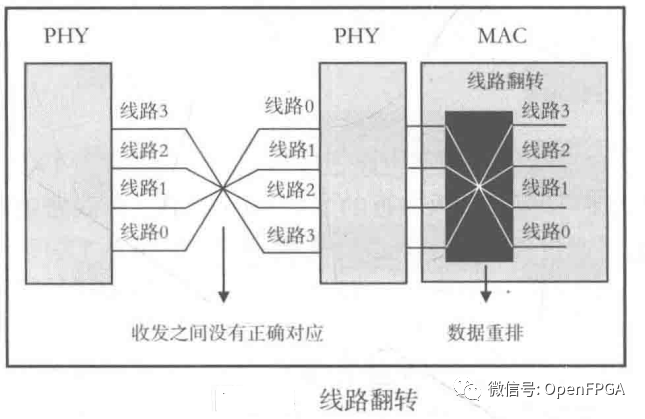

線路翻轉在多線路鏈路(例如,x8 PCIe有8條線路)中,數據包按照字節分割方式進行傳輸。所有的線路通過電路板連接到接收設備。正確的連接方式是TX線路0連接到RX線路0,TX線路1連接到RX線路1,以此類推。

在實際設計和布線時,可能會因為疏忽造成收發之間沒有正確對應的情況。這些線路在多層PCB上布線時,會在不同層次之間穿過,會進行90°彎曲,這些都可能導致連接失誤。在某些情況下,常規連接會導致布線閑難,此時也會有意識地希望能夠進行錯序連接。PCIe采用了一種名為線路切換的技術來解決這種無意或有意的板級錯序連接。

如圖所示,其基本思路是在鏈路訓練過程中發現錯序連接并進行數據重排。

屬于一個鏈路的多個線路被編號為0、1、2、3、4、5、6、7等。當信號線兩端試圖發現線路編號時(在訓練字符集中的特定區域內寫入了所屬線路的編號),它們各自都有期望的編號值。線路0希望收到的訓練字符集合中的編號為0,線路7希望收到的編號為7。

如果接收電路收到的編號與期望值不同,它會記錄下來其實際連接的對端發送電路的編號。信號線兩端的電路都可以根據實際連接的通道編號調整本端的實際編號,但需要注意的是,只能有一端可以進行調整,不能兩端同時進行,否則會繼續出錯。

雙方選擇的用于解決錯序問題的一端在發送數據之前先要切換發送數據的通路(例如,線路0的數據切換到線路7上,線路7的數據切換到線路0上)。同時它還要切換接收通路RX通路0上的數據與通路7連接,通路7與通路0連接,剩余的通路依次切換)。正如我們所能看到的,這里沒有邏輯修改,通過內部的連接重定位解決了板級連接存在的問題。

鎖相環 PLLPLL在數字系統中有很多應用,常見的典型重要應用如下:

數據時鐘恢復(Clock Data Recovery,CDR)

去除時鐘偏移

作為倍頻器使用

CDR

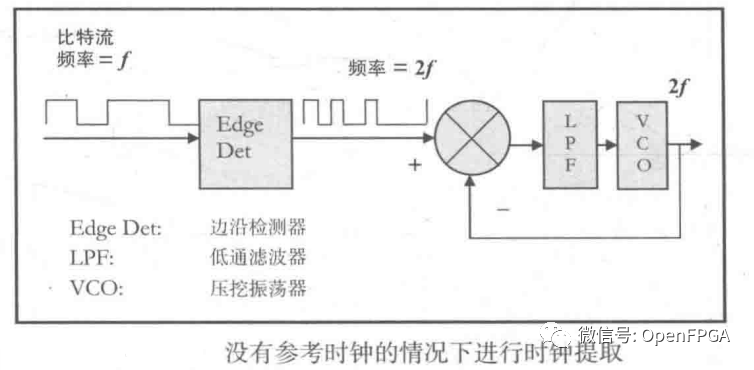

在很多高速串行數據傳輸應用中,數據在傳輸過程中沒有伴隨著時鐘的傳輸。然而,在數據流中存在著足夠的數據跳變(0到1和1到0的跳變),接收端電路可以據此提取與數據同步的時鐘。在接收端,可以使用參考時鐘為時鐘提取提供幫助。在沒有參考時鐘的情況下也可以提取接收時鐘的。下面我們將針對這兩種情況對PLL電路加以討論。

不帶參考時鐘的CDR(見下圖)

如果接收端接收的比特流速率為f,那么接收端的邊沿檢測器檢測到的數據跳變頻率為2f,VCO產生的自由震蕩時鐘頻率為2f。

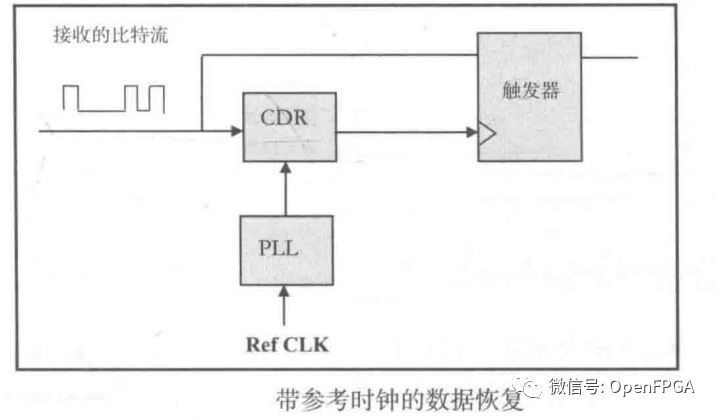

帶參考時鐘的CDR (見下圖)

這種方式就不需要過多介紹,常見的傳輸方式。

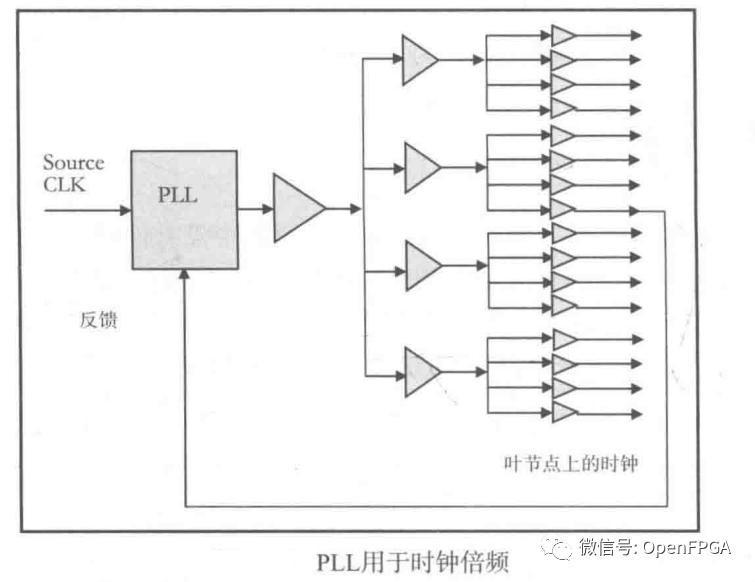

使用PLL去除時鐘偏移

在SoC中,時鐘樹被用于將時鐘信號分配給物理上分布在芯片各個區域的觸發器。在時鐘樹的通路上,分布著帶有延遲的驅動器。由于時鐘分布路徑上存在延遲,葉節點上的時鐘與根節點上的時鐘相比,存在相移(相位滯后)。此時,可以使用PLL消除葉節點上時鐘的相移使之和根節點上的時鐘相位對準,如圖所示。

PLL還可用于產生與輸人時鐘存在指定相移的輸出時鐘,例如,產生和輸入時鐘存在90°相移的輸出時鐘。

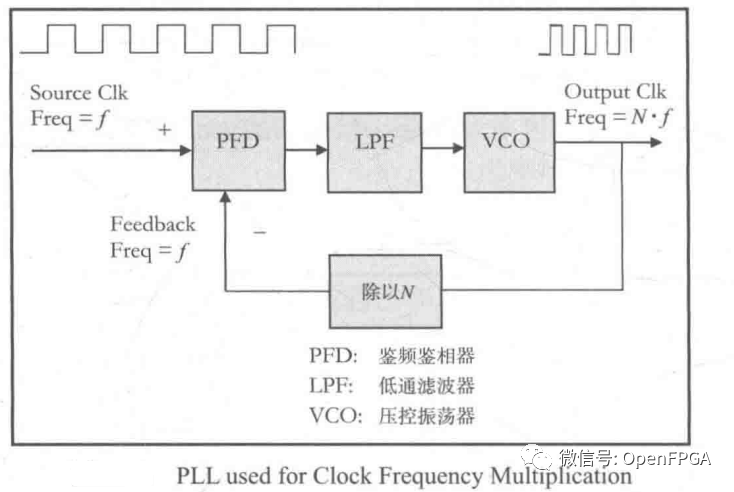

使用PLL實現倍頻器

PLL可用于根據時鐘源產生更高頻率的時鐘信號。將輸岀時鐘信號除以N作為PLL的反饋信號與時鐘源相比較,可以得到N倍于時鐘源的輸出時鐘信號,同時二者具有相同的相位。

串行總線的PMA層功能PMA層主要實現模擬電路功能。PMA層電路也被稱為SerDes(Serializer & Deserializer),是一個非常特殊的電路。我們的目標是從電路的系統設計層面對其加以介紹,以便對串行總線技術形成完整的理解。

發送均衡

采用串行傳輸機制時,數據以比特流的方式在差分對(TX+ TX-)上傳輸。在線路上傳輸的數據波形可以看成是大量不同頻率、不同幅度的正弦波疊加作用的結果。

當數據速率很高時,存在一個占主導地位的高頻正弦波分量。在高速傳輸時,差分傳輸線路的通路特性與低通濾波器(RC濾波器)接近,但相對于低頻成分,高頻成分的衰減更大一些。這意味著在接收端,接收信號中的不同的頻率成分所占的比例與發送時不同。接收到的信號與發送端信號相比會發生畸變,造成ISI(碼間串擾),這會使得CDR恢復的數據中存在誤碼。

什么是碼間串擾?

如果我們發送一個階躍函數波形(在一個時鐘周期內為1的脈沖信號),在接收端波形會發生變化。接收脈沖會展寬并進入相鄰時鐘周期中。從第N個時鐘周期展寬到第N+1個時鐘周期的信號與第N+1個時鐘周期的信號波形疊加,使得第N+1個周期內的波形發生畸變,這種畸變可能會造成對該時鐘周期邏輯值的判決發生錯誤,這被稱為符號間的串擾,即碼間串擾(IS1)。

前有很多種技術可以解決傳輸線頻率響應的問題。可以通過采用發送端均衡技術,或采用接收端均衡技術加以解決。

發送端預加重技術

發送驅動時,對高頻成分的增益大于低頻成分,頻率越高增益越大。信號到達接收端時,所有的頻率成分得到的總體增益相同。

發送端后加重技術

另一種技術是后加重技術。采用后加重技術時,邊沿翻轉(0到1或1到0)之后的比特被正常放大,但此后的其他比特(沒有邊沿翻轉的比特)增益相對降低。由于信號的高頻成分主要出現在信號翻轉部分,這樣做等效于為高頻成分提供了更大的增益。當數據到達接收端時,所有比特位的最終等效增益是相同的。PCIe和SATA都使用了后加重傳輸技術。

接收均衡

在接收端,可以為高頻成分提供相對于低頻成分更大的增益。針對高頻成分給予補償的結果是整個傳輸系統為所有頻率成分提供了相同的增益。經過補償后,接收波形與發送波形更加相似。接收器均衡技術有利于減少1SI。

端接電阻

TX+和TX-信號是一對傳輸線,在發送端和接收端需要進行傳輸線阻抗匹配,以避免產生信號反射,使發送信號產生畸變。當信號發生反射時,它與原始的發送信號發生疊加,使發送信號增強或減弱。如果反射的信號強度較大,可能會使發送信號產生較大的畸變從而導致接收錯誤。終端匹配的目的就是減少或消除接收端對發送信號的反射。

編輯:jq

-

電阻

+關注

關注

87文章

5614瀏覽量

174495 -

pcb

+關注

關注

4358文章

23442瀏覽量

407698 -

串行數據

+關注

關注

0文章

54瀏覽量

16737 -

cdr

+關注

關注

1文章

52瀏覽量

18341

原文標題:串行總線技術(二)-串行總線中的先進設計理念及SerDes/PMA介紹

文章出處:【微信號:Open_FPGA,微信公眾號:OpenFPGA】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

車載SerDes重大突破,業內首款雙協議芯片誕生!

什么是SerDes?SerDes有哪些應用?

智多晶Serdes IP的應用領域及工作原理

使用FPGA對40G以太網接口芯片Serdes進行測試的方法

MultiGABSE-AU物理層PMA子層及PMD子層的相關機制

CAN總線通信原理介紹 CAN總線模塊選擇指南

國產車載SerDes百花齊放,12G以上已是“基本操作”

電腦通用串行總線控制器感嘆號怎么辦

通用串行總線控制器和通用串行總線設備的區別

USB是通用串行總線

ASP4644在FPGA SERDES供電中的應用

聚焦MIPI 系列之二:汽車 SerDes 發射機測試

串行總線中的先進設計理念及SerDes/PMA介紹

串行總線中的先進設計理念及SerDes/PMA介紹

評論