采用SystemVerilog進行仿真則更容易生成隨機數,而且對隨機數具有更強的可控性。對于隨機變量,在SystemVerilog中可通過rand或randc加數據類型的方式定義。rand表明該變量為隨機變量,且在指定范圍內服從均勻分布;randc是在rand的基礎上要求當生成的隨機數已經在指定范圍內完成一次遍歷之后,將重復遍歷,c為cyclic(循環)。聲明隨機變量后,需要通過constraint限定隨機數需要滿足的條件。這些都需要在class中聲明。

案例1:用小于號《 大于號 》 小于等于號 《= 大于等于號》=創建限定條件

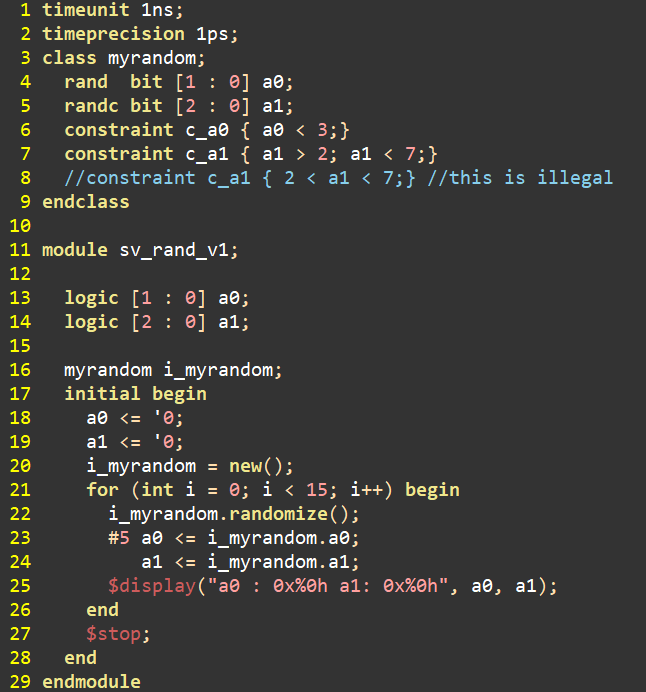

代碼如下圖所示。代碼第6行限定了a0必須小于3,第7行限定了a1必須大于2且小于7。注意,這4個關系運算符不能連寫,如代碼第8行是不合法的。代碼第16行對class實例化,代碼第20行為class對象分配內存空間并完成class對象的初始化。代碼第22行用于判定隨機數是否成功生成,若成功則返回1,否則返回0。

編輯:jq

-

仿真

+關注

關注

51文章

4245瀏覽量

135379 -

Verilog

+關注

關注

29文章

1366瀏覽量

111917 -

System

+關注

關注

0文章

166瀏覽量

37603 -

代碼

+關注

關注

30文章

4891瀏覽量

70309

原文標題:SystemVerilog仿真如何生成隨機數

文章出處:【微信號:Lauren_FPGA,微信公眾號:FPGA技術驛站】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

labview求助:想寫一個labview輸出不重復隨機數的程序,有沒有大佬幫忙看看這個假分支要怎么寫?

“Quantum Origin”成首個獲NIST驗證的軟件量子隨機數生成器

開源隨機數生成器庫OpenRNG助力實現移植到Arm平臺時的最佳性能

《DNESP32S3使用指南-IDF版_V1.6》第三十一章 RNG實驗

“安徽造”量子隨機數芯片通過國家密碼管理局檢測

問天量子和方寸微電子聯合發布量子隨機數芯片

對稱加密技術有哪些常見的安全漏洞?

藍牙AES+RNG如何保障物聯網信息安全

雅特力AT32 MCU的隨機數生成

如何利用SystemVerilog仿真生成隨機數

如何利用SystemVerilog仿真生成隨機數

評論