芯片的制程從最初的0.35微米到0.25微米,后來又到0.18微米、0.13微米、90nm、65nm、45nm、32nm和14nm。在提高芯片工藝制程的過程中,大約需要縮小十倍的幾何尺寸及功耗,才能達到10nm甚至7nm。

在工藝分類上,芯片主要分兩大類:

·HP(High Performance):主打高性能應用范疇;

·LP(Low Power):主打低功耗應用范疇。

滿足不同客戶需求,HP 內部再細分 HPL、HPC、HPC+、HP 和 HPM 五種。

HP 和 LP 之間最重要區別就在性能和漏電率上,HP 在主打性能,漏電率能夠控制在很低水平,芯片成本高;LP 則更適合中低端處理器使用,因為成本低。

所以,芯片除了在制程上尋求突破,工藝上也會逐步升級。

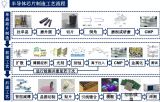

芯片制造的整個過程包括芯片設計、芯片制造、封裝制造、測試等。芯片制造過程特別復雜。

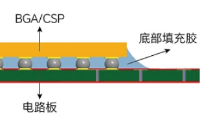

芯片制造過程有這么幾個階段:材料制備——單晶硅制造→晶圓片生成芯片前端——芯片構建(Wafer Fabrication)芯片后端——封裝(Package)→完整測試(Initial Test and Final Test)

新智造,電子產品世界網絡綜合整理

責任編輯:李倩

-

芯片

+關注

關注

456文章

51062瀏覽量

425777 -

晶圓

+關注

關注

52文章

4950瀏覽量

128165 -

芯片制造

+關注

關注

10文章

627瀏覽量

28854

發布評論請先 登錄

相關推薦

芯片制造的7個前道工藝

英特爾18A制程芯片Panther Lake處理器下半年發布

2025年半導體行業競爭白熱化:2nm制程工藝成焦點

半大馬士革工藝:利用空氣隙減少寄生電容

芯片微型化挑戰極限,成熟制程被反推向熱潮

HV-CMOS工藝制程技術簡介

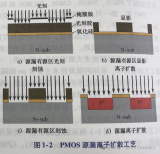

PMOS工藝制程技術簡介

引線框架貼膜工藝在QFN封裝制程中的應用

芯片工藝制程的幾個階段

芯片工藝制程的幾個階段

評論