本文的關鍵要點

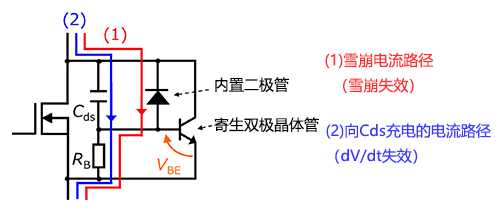

dV/dt失效是MOSFET關斷時流經寄生電容Cds的充電電流流過基極電阻RB,使寄生雙極晶體管導通而引起短路從而造成失效的現象。

dV/dt是單位時間內的電壓變化量,VDS的上升坡度越陡,越容易發生MOSFET的dV/dt失效問題。

一般來說,反向恢復特性越差,dV/dt的坡度越陡,越容易產生MOSFET的dV/dt失效。

什么是dV/dt失效

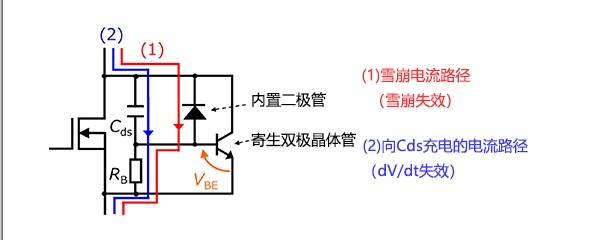

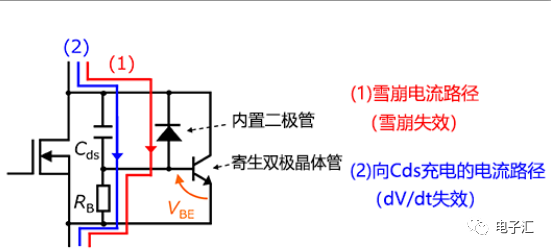

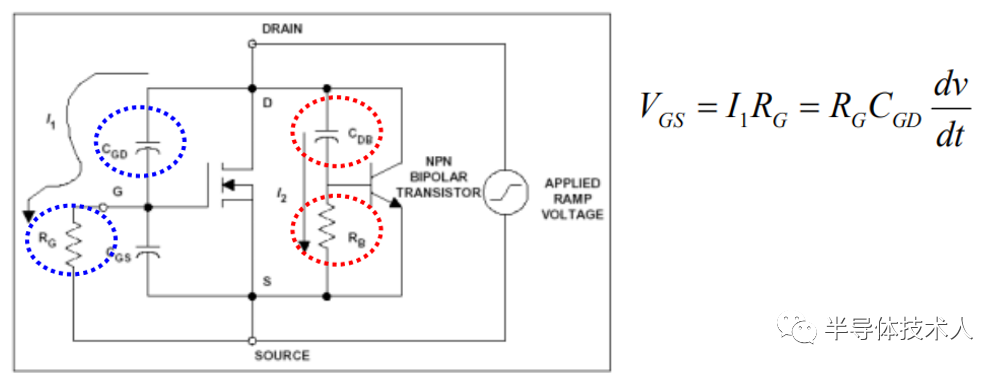

如下圖(2)所示,dV/dt失效是由于MOSFET關斷時流經寄生電容Cds的瞬態充電電流流過基極電阻RB,導致寄生雙極晶體管的基極和發射極之間產生電位差VBE,使寄生雙極晶體管導通,引起短路并造成失效的現象。通常,dV/dt越大(越陡),VBE的電位差就越大,寄生雙極晶體管越容易導通,從而越容易發生失效問題。

MOSFET的dV/dt失效電流路徑示意圖(藍色部分)

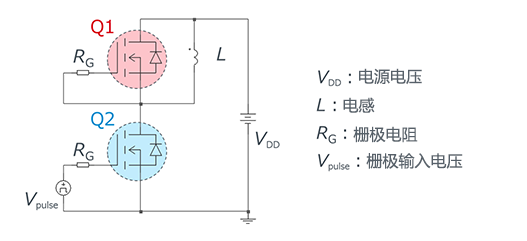

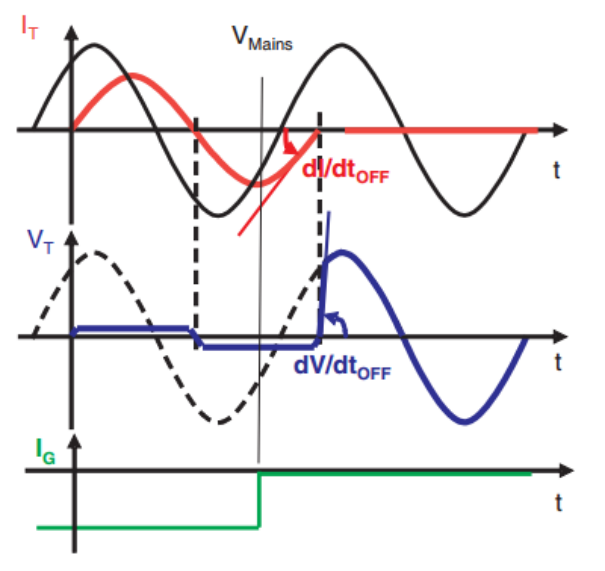

此外,在逆變器電路或Totem-PolePFC等上下橋結構的電路中,反向恢復電流Irr會流過MOSFET。受該反向恢復電流影響的dV/dt,可能會使寄生雙極晶體管誤導通,這一點需要注意。dV/dt失效與反向恢復特性之間的關系可以通過雙脈沖測試來確認。雙脈沖測試的電路簡圖如下:

雙脈沖測試的電路簡圖

關于在雙脈沖測試中的詳細情況,請參考R課堂基礎知識評估篇中的“通過雙脈沖測試評估MOSFET的反向恢復特性”。

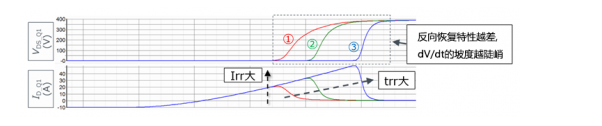

dV/dt和反向恢復電流的仿真結果如下圖所示。設MOSFET①~③的柵極電阻RG和電源電壓VDD等電路條件相同,僅反向恢復特性不同。圖中列出了Q1從續流工作轉換到反向恢復工作時的漏源電壓VDS和漏極電流(內部二極管電流)ID。

雙脈沖測試的仿真結果

一般情況下,與MOSFET①相比,MOSFET③可以說是“反向恢復特性較差(Irr和trr大)”的產品。從這個仿真結果可以看出,反向恢復特性越差,dV/dt的坡度就越陡峭。這一點通過流經電容器的瞬態電流通常用I=C×dV/dt來表示也可以理解。此外,在上述仿真中,Irr的斜率(di/dt)均設置為相同條件,但當di/dt陡峭時,dV/dt也會變陡峭。

綜上所述,可以說,在橋式電路中使用MOSFET時,反向恢復特性越差的MOSFET,發生MOSFET的dV/dt失效風險越大。

-

MOSFET

+關注

關注

150文章

8392瀏覽量

219102 -

寄生電容

+關注

關注

1文章

297瀏覽量

19693 -

橋式電路

+關注

關注

1文章

23瀏覽量

11431

發布評論請先 登錄

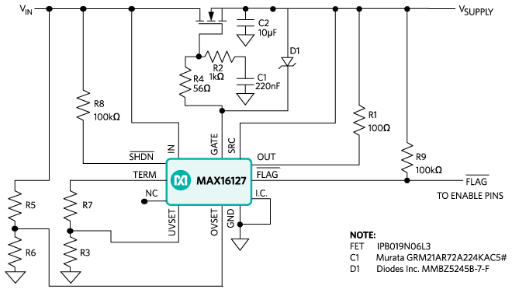

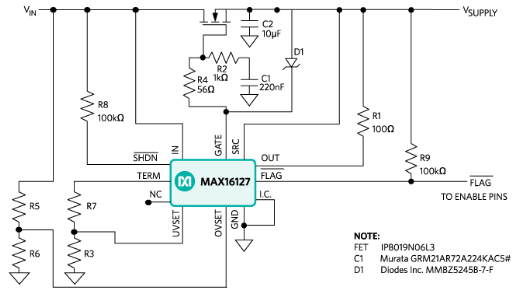

限制穩壓器啟動時dV/dt和電容的電路

請問開關的電壓變化率(dv/dt)和電磁干擾有沒有關系?

Analysis of dv/dt Induced Spur

Analysis of dv_dt Induced Spur

電壓源型驅動dv/dt的表現

混合動力系統驅動器內dV/dt噪聲的來源及解決方案

如何控制電源dV/dt上升時間同時限制通過控制FET的功率損耗

MOSFET的失效機理:什么是dV/dt失效

擺脫高dV/dt電源的優勢

“dv/dt”和“di/dt”值:這些值的水平對固態繼電器有什么影響?

dV/dt失效是什么意思

dV/dt失效是什么意思

評論