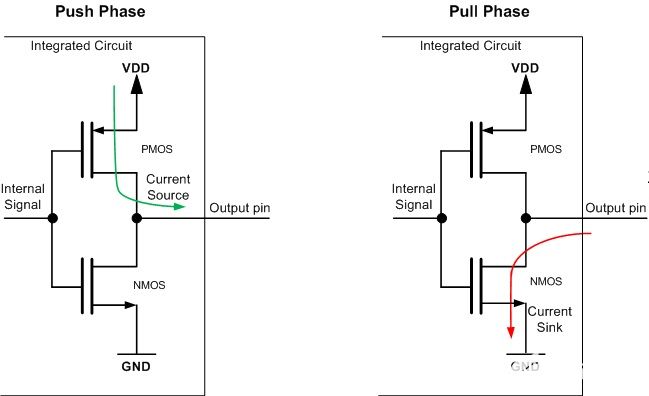

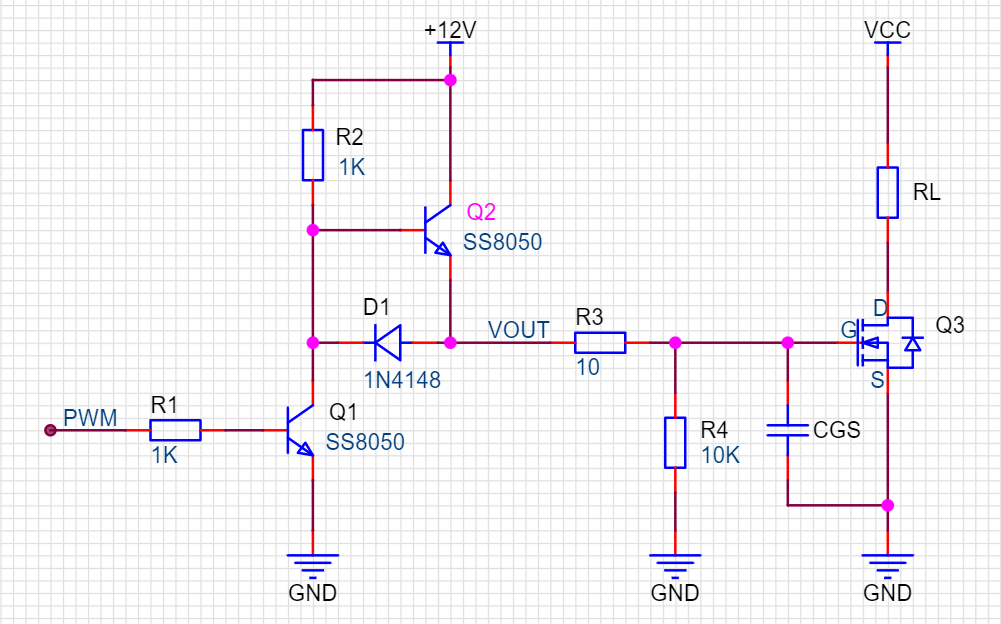

推挽輸出又叫推拉輸出,是最常見(jiàn)的輸出配置了,正如它的名字那樣,推拉輸出能夠驅(qū)動(dòng)輸出兩種電平。一種是拉接到地(從負(fù)載灌入電流),另一個(gè)被推到電源電壓(輸出電流到負(fù)載)。推挽輸出可以使用一對(duì)開(kāi)關(guān)來(lái)實(shí)現(xiàn)。在集成電路中一般使用兩個(gè)晶體管搭建。在下圖中,我們可以看到使用 PMOS 和 NMOS 晶體管構(gòu)建推挽輸出配置。左側(cè)顯示的是推階段的電路狀態(tài),右側(cè)顯示的是拉階段的電路狀態(tài)。

1.推挽電路工作原理

推動(dòng)階段——當(dāng)連接到晶體管柵極的內(nèi)部信號(hào)設(shè)置為低電平時(shí),PMOS 晶體管被激活,電流從 VDD 流經(jīng)它到輸出引腳,NMOS 晶體管處于非活動(dòng)狀態(tài)(開(kāi)路)且不導(dǎo)通。

拉動(dòng)階段——當(dāng)連接到晶體管柵極的內(nèi)部信號(hào)設(shè)置為高電平時(shí),NMOS 晶體管被激活(關(guān)閉)并且電流開(kāi)始從輸出引腳流過(guò)它到 GND。同時(shí),PMOS 晶體管處于非活動(dòng)狀態(tài)(開(kāi)路)并且不傳導(dǎo)電流。這種類型的輸出不允許在總線配置中將多個(gè)設(shè)備連接在一起,推挽配置最常用于具有單向通信線上(線路上的信號(hào)傳輸僅在單一方向,比如SPI、UART等)。

2.電路應(yīng)用注意事項(xiàng)

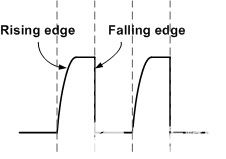

推挽輸出在生成的輸出數(shù)字信號(hào)的斜率方面提供了更好的性能,現(xiàn)在很多IC甚至可以配置信號(hào)上升或者下降的斜率,從而允許我們?cè)趥鬏斔俣群虴MI方面找到最佳的平衡點(diǎn)。上升沿斜率——上拉電阻與線路的固有電容相結(jié)合,形成一個(gè)低通濾波器。從而我們可以根據(jù)電阻器的值和線路的電容來(lái)調(diào)整上升沿斜率,上升沿的斜率與下降沿的斜率可能存在明顯差異。一般來(lái)說(shuō)下降沿更尖銳,因?yàn)樗鞘褂镁哂蟹浅5蛢?nèi)阻的晶體管實(shí)現(xiàn)的。而上升沿是由上拉電阻形成的,前面提到的低通濾波效果更加明顯。

圖 1 開(kāi)漏輸出產(chǎn)生的方波信號(hào)邊沿

功耗和噪聲干擾——在選擇上拉電阻值時(shí)我們需要權(quán)衡。當(dāng)線路上的設(shè)備驅(qū)動(dòng)輸出低電平時(shí),它會(huì)導(dǎo)致較高的電流流過(guò)較低值的上拉電阻,這會(huì)增加功耗的問(wèn)題。但是,選擇較高值的電阻器會(huì)反過(guò)來(lái)導(dǎo)致流過(guò)電阻器的電流較低,這將使線路上的外部干擾(噪聲)更容易影響信號(hào)狀態(tài)。應(yīng)該注意的是,在很多MCU中,配置為推挽的輸出引腳在大多數(shù)情況下可以動(dòng)態(tài)重新配置為輸入,這是通過(guò)關(guān)閉兩個(gè)晶體管來(lái)實(shí)現(xiàn)的,從而在線路上實(shí)現(xiàn)高阻抗?fàn)顟B(tài)。然后可以從其他外部設(shè)備采集輸入信號(hào)。

-

推挽電路

+關(guān)注

關(guān)注

18文章

115瀏覽量

38542 -

推挽輸出

+關(guān)注

關(guān)注

0文章

85瀏覽量

6659

發(fā)布評(píng)論請(qǐng)先 登錄

SiC MOSFET驅(qū)動(dòng)電路設(shè)計(jì)注意事項(xiàng)

物聯(lián)網(wǎng)中電路設(shè)計(jì)常見(jiàn)的光耦隔離器工作原理、類型、應(yīng)用場(chǎng)景及設(shè)計(jì)注意事項(xiàng)

功放電路電源設(shè)計(jì)注意事項(xiàng)

555電路調(diào)試技巧和注意事項(xiàng)

buck電路工作原理解析 buck電路設(shè)計(jì)注意事項(xiàng)

ADS855x的驅(qū)動(dòng)器電路設(shè)計(jì)注意事項(xiàng)

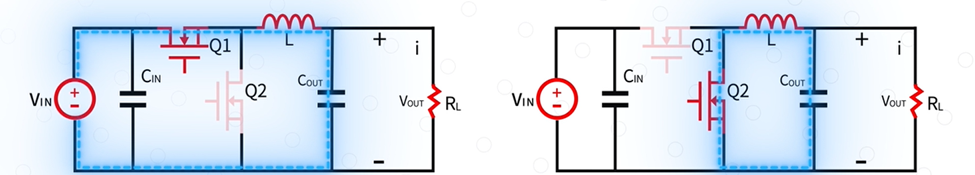

推挽輸出電路原理分析

LMK時(shí)鐘family LVDS輸出交流耦合設(shè)計(jì)注意事項(xiàng)

PNP傳感器輸出信號(hào)的特點(diǎn)和工作方式

Buck電路中PCB layout布局設(shè)計(jì)和注意事項(xiàng)

推挽輸出電路工作原理以及注意事項(xiàng)(推拉輸出電路)

推挽輸出電路工作原理以及注意事項(xiàng)(推拉輸出電路)

評(píng)論