有些應用中,需要降低Xilinx MPSoC的功耗。缺省設置中,R5/GPU都被使能。如果需要省電,可以在Vivado里關閉R5/GPU。步驟如下:

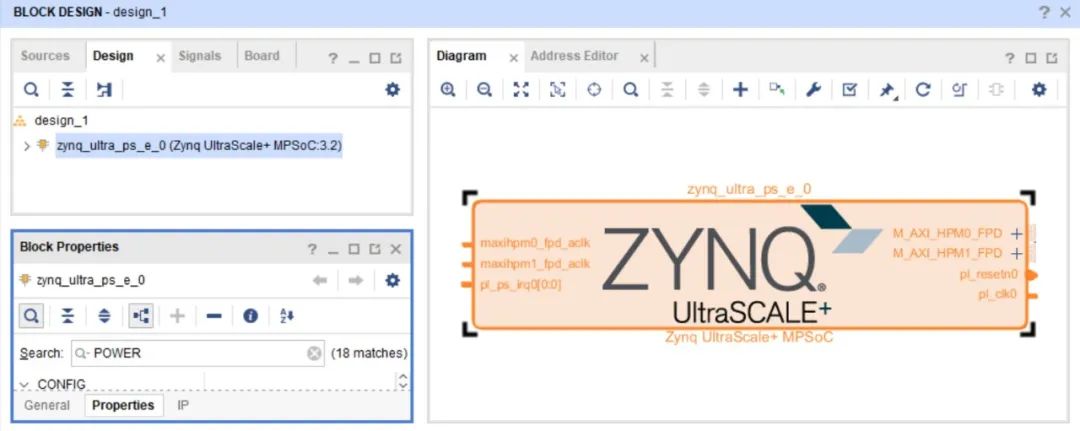

1.選中 MPSoC IP,在右鍵菜單中選擇Block Properties.

2.在窗口Block Properties中,選擇Properties.

3. 在窗口中,展開 “Config”.

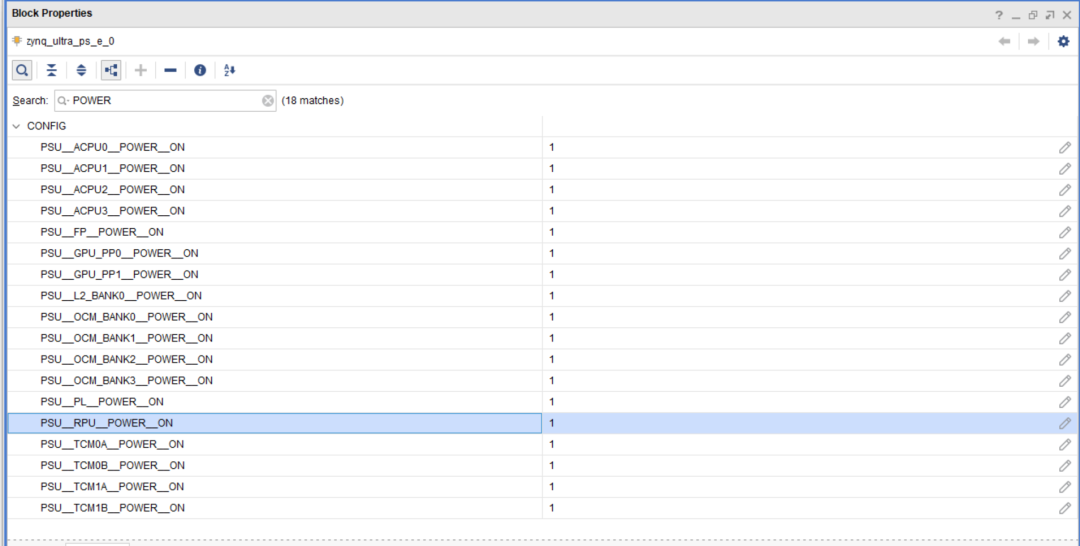

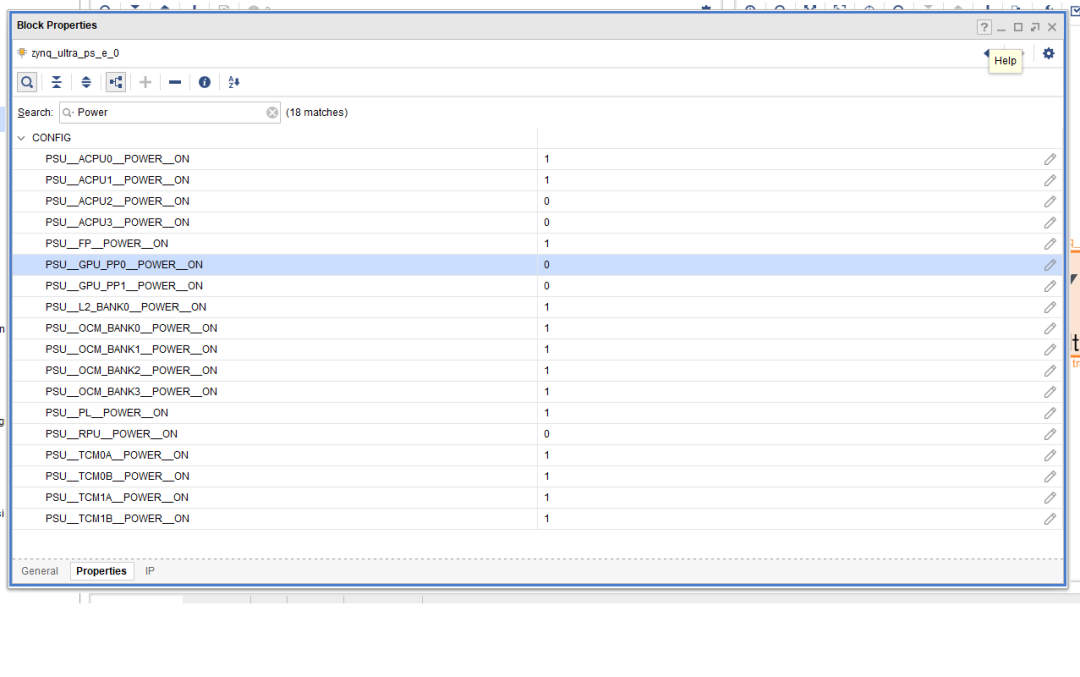

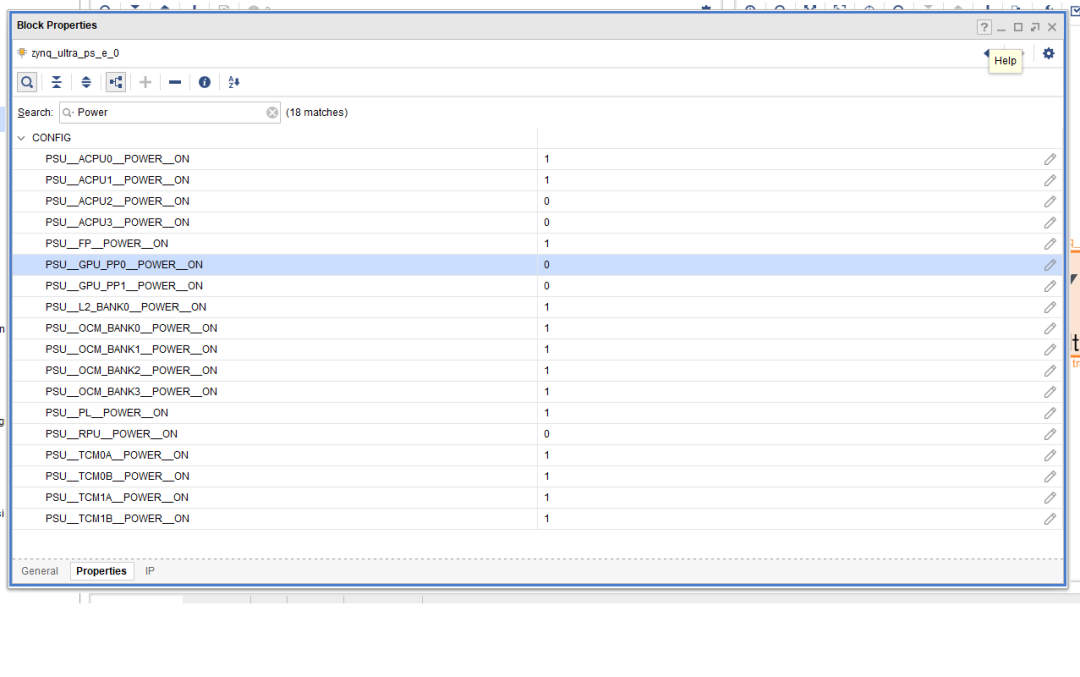

4. 在搜索框中輸入 “Power”, 出現PSU_RPU_POWER_ON等選項。如果值是1,表示被使能;如果值是0,表示被關閉。如果要關閉,點擊最左邊的編輯圖標,輸入0。

編輯前Power選項

編輯后Power選項

在Vivado里編輯完成后,執行“Generate Output Products”, 在導出Hardware的HDF/XSA文件。

2. JTAG檢查R5/A53狀態

2. JTAG檢查R5/A53狀態

在SDK/Vitis里創建FSBL和Standalone程序,啟動后,在XSCT命令后窗口下,檢查R5/A53狀態,可以看到設置為0的R5/A53的狀態是No Power。

xsct% connect

tcfchan#2

xsct% target

1 PS TAP

2 PMU

3 PL

4 PSU

5 RPU (Reset)

6 Cortex-R5 #0 (No Power)

7 Cortex-R5 #1 (No Power)

8 APU

9 Cortex-A53 #0 (Running)

10 Cortex-A53 #1 (Power On Reset)

11 Cortex-A53 #2 (No Power)

12 Cortex-A53 #3 (No Power)

3. 代碼

代碼在psu_init.c里的函數psu_peripherals_powerdwn_data( )里。

/*

POWER DOWN REQUEST INTERRUPT ENABLE

/

/

Register : REQ_PWRDWN_INT_EN @ 0XFFD80218

Power-down Request Interrupt Enable for Dual_R5

PSU_PMU_GLOBAL_REQ_PWRDWN_INT_EN_RPU 1

Power-down Request Interrupt Enable for GPU PP0

PSU_PMU_GLOBAL_REQ_PWRDWN_INT_EN_PP0 1

Power-down Request Interrupt Enable for GPU PP1

PSU_PMU_GLOBAL_REQ_PWRDWN_INT_EN_PP1 1

Power-down Request Interrupt Enable for ACPU2

PSU_PMU_GLOBAL_REQ_PWRDWN_INT_EN_ACPU2 1

Power-down Request Interrupt Enable for ACPU3

PSU_PMU_GLOBAL_REQ_PWRDWN_INT_EN_ACPU3 1

Power-down Request Interrupt Enable Register. Writing a 1 to this locati

on will unmask the Interrupt.

(OFFSET, MASK, VALUE) (0XFFD80218, 0x0000043CU ,0x0000043CU)

/

PSU_Mask_Write(PMU_GLOBAL_REQ_PWRDWN_INT_EN_OFFSET,

0x0000043CU, 0x0000043CU);

/##################################################################### */

/*

POWER DOWN TRIGGER

/

/

Register : REQ_PWRDWN_TRIG @ 0XFFD80220

Power-down Request Trigger for Dual_R5

PSU_PMU_GLOBAL_REQ_PWRDWN_TRIG_RPU 1

Power-down Request Trigger for GPU PP0

PSU_PMU_GLOBAL_REQ_PWRDWN_TRIG_PP0 1

Power-down Request Trigger for GPU PP1

PSU_PMU_GLOBAL_REQ_PWRDWN_TRIG_PP1 1

Power-down Request Trigger for ACPU2

PSU_PMU_GLOBAL_REQ_PWRDWN_TRIG_ACPU2 1

Power-down Request Trigger for ACPU3

PSU_PMU_GLOBAL_REQ_PWRDWN_TRIG_ACPU3 1

Power-down Request Trigger Register. Writing a 1 to this location will t

rigger a power-down request to the PMU.

(OFFSET, MASK, VALUE) (0XFFD80220, 0x0000043CU ,0x0000043CU)

/

PSU_Mask_Write(PMU_GLOBAL_REQ_PWRDWN_TRIG_OFFSET,

0x0000043CU, 0x0000043CU);

/##################################################################### */

審核編輯 :李倩

-

gpu

+關注

關注

28文章

4937瀏覽量

131180 -

Vivado

+關注

關注

19文章

834瀏覽量

68698

原文標題:【干貨分享】 在Vivado里關閉R5/GPU,降低Xilinx MPSoC的功耗

文章出處:【微信號:zhuyandz,微信公眾號:FPGA之家】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

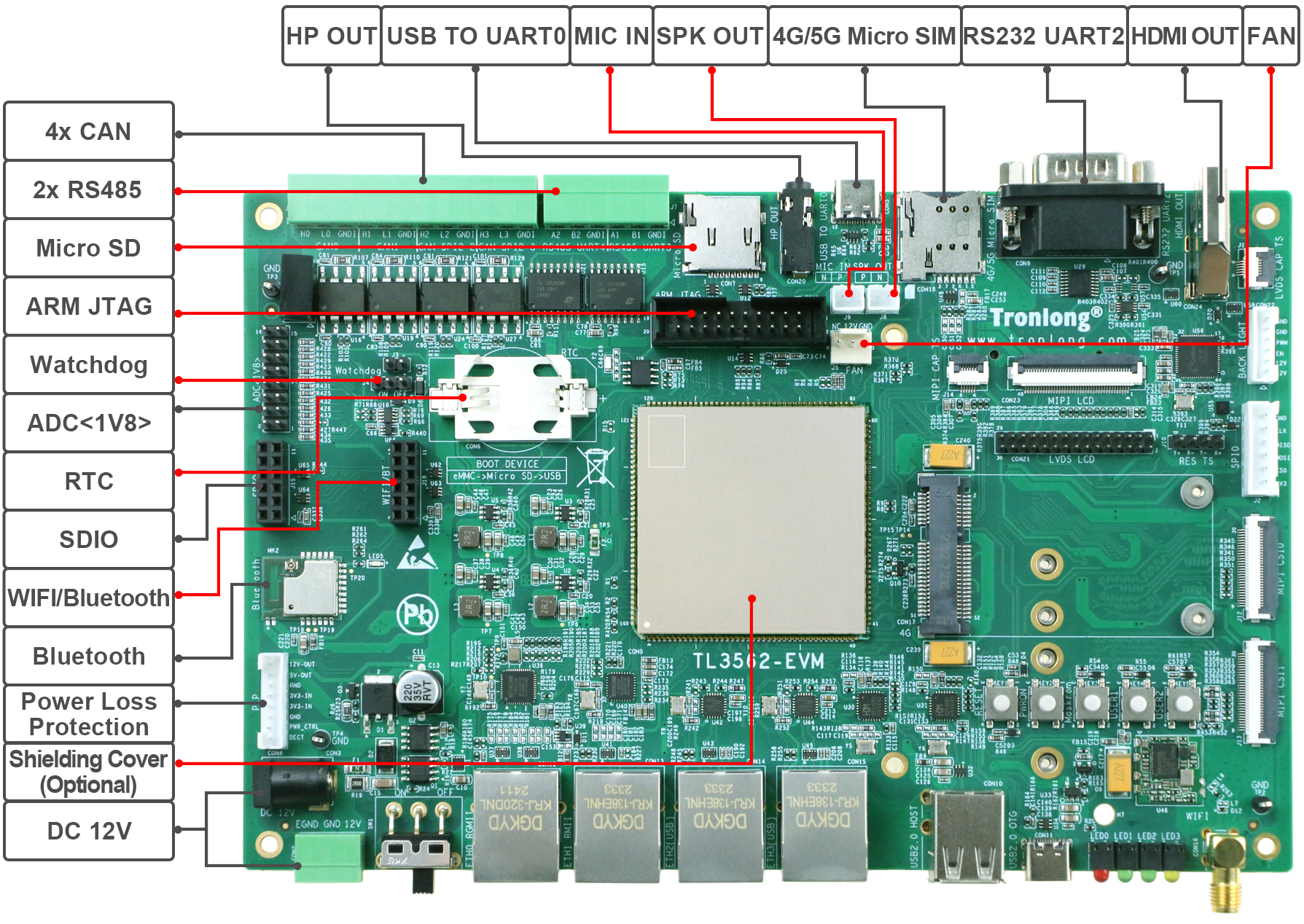

創龍瑞芯微 RK3562 國產 2GHz 四核A53 工業開發板—調試工具安裝

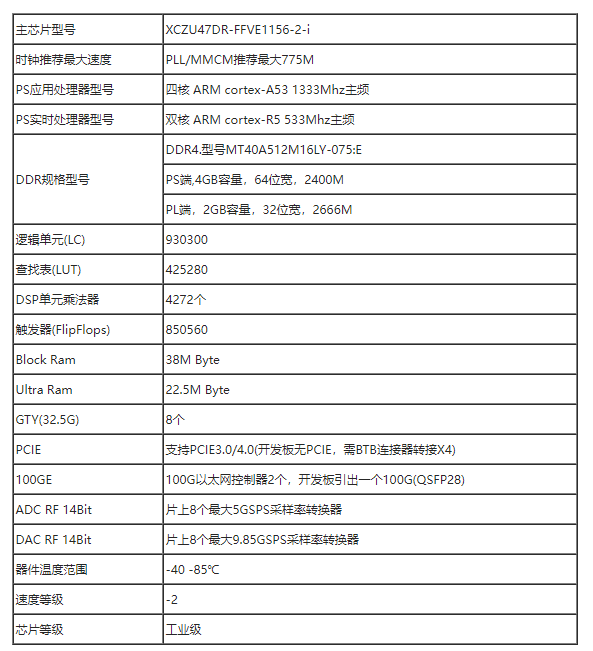

高速數據采集卡設計:887-基于 RFSoC 47DR的8T8R 100Gbps 軟件無線電光纖前端卡

高性能+長續航!基于RK3576的電池管理系統(3.7V/7000mAh)開源方案發布

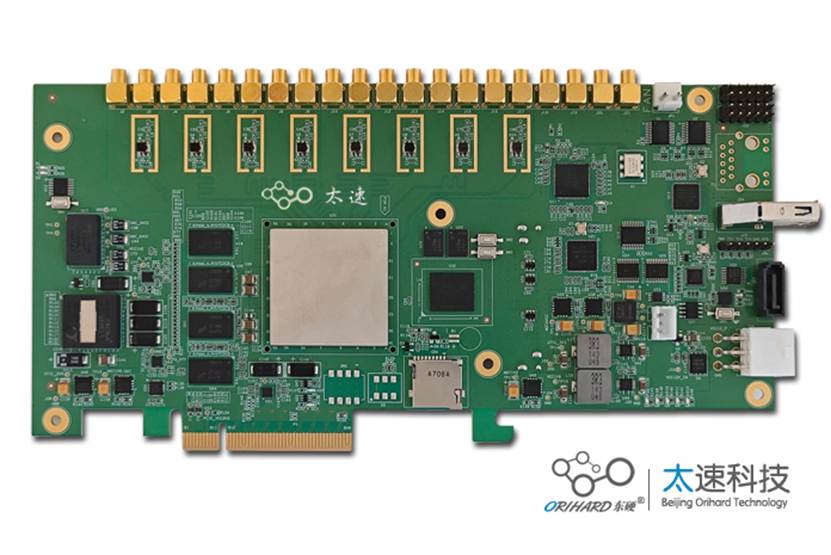

基于RFSOC的8路5G ADC和8路9G的DAC PCIe卡

Imagination GPU為瑞薩R-Car Gen 5系列SoC提供強大高效的算力

e203在vivado硬件里自定義指令識別為非法指令怎么解決?

Xilinx_Vivado_SDK的安裝教程

TAS5710的PLL_FLTP和電源VR_ANA的電阻和電容的C9,R5,C10的值是怎么算出來的?

Vivado使用小技巧

運放電路的反饋回路中的R4和R5是什么意思?

OPA1632負載接在了R3和R5中間,如何計算其傳遞函數?

采用OPA2377設計跨阻放大器,其中R5,R4,R6構成T型反饋回路,請問電容C4的作用是什么?

安卓主板_ 執法記錄儀 手持終端PDA 安卓手機主板_聯發科PCBA定制開發

Vivado里關閉R5/A53/GPU

Vivado里關閉R5/A53/GPU

評論