一、查找表

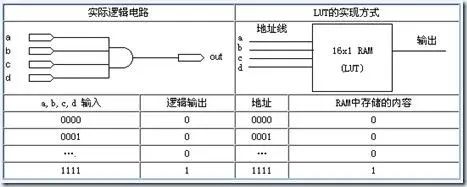

LUT就是查找表,對于4輸入的LUT而言,實際上就是4位地址位,一位數(shù)據(jù)位的存儲器,能夠存儲16位數(shù)據(jù),所以我們在FPGA設計中可以用LUT組建分布式的RAM。

這樣也可以解釋我們在設計中為什么要采用流水線的實現(xiàn)方法

因為當輸入數(shù)據(jù)的位數(shù)遠大于一個LUT的輸入時,就需要用多個LUT級聯(lián)來實現(xiàn)邏輯,那么級聯(lián)產(chǎn)生的延時也就不可避免了,這樣就會制約系統(tǒng)的運行頻率。那么為了避免級聯(lián)數(shù)過于多,就采用插入寄存器的方法來實現(xiàn)。

舉一個簡單的例子,如果要實現(xiàn)一個6*1的mux可以用一個6輸入的LUT或者是2個4輸入的LUT來實現(xiàn),6輸入的LUT相當于是6位地址線一位數(shù)據(jù)位,能夠存儲64bit的數(shù)據(jù),而采用兩個4輸入的LUT的話,它的總?cè)萘看笮?2位數(shù)據(jù)。

如果用6輸入的LUT實現(xiàn)4輸入LUT的功能,那么就浪費了1-16/64=75%的資源,所以采用少輸入的LUT可以更好的節(jié)省面積和資源,但是呢如果LUT采用的是2輸入的呢,那樣豈不是更好嗎,不是的,因為對于多輸入的信號處理的時候,就需要有多個LUT的級聯(lián)來實現(xiàn),而級聯(lián)有不可避免的會導致延時過分,導致時序不滿足。因此在實際的FPGA產(chǎn)品中多采用的是4輸入或者6輸入的LUT。

圖 4輸入的LUT

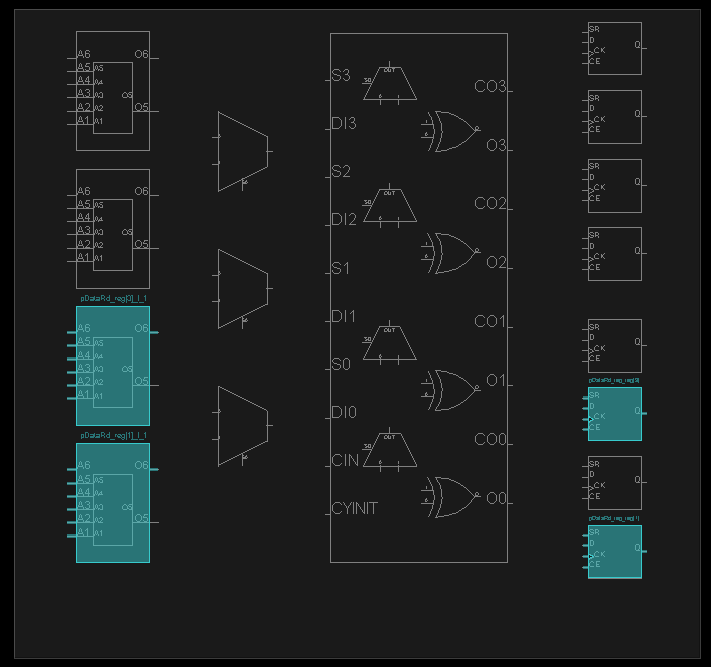

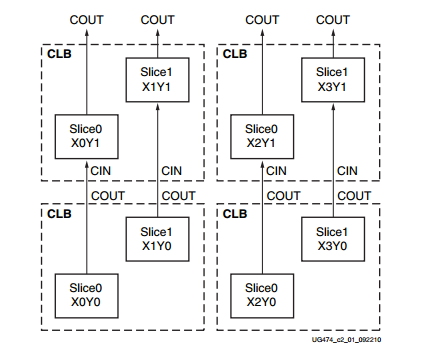

CLB是xilinx基本邏輯單元,每個CLB包含兩個slices,每個slices由4個(A,B,C,D)6輸入LUT和8個寄存器組成(中間應該還有一些選擇器、與非門、或非門之類的東西)。放一個slices的內(nèi)部圖

同一CLB中的兩片slices沒有直接的線路連接,分屬于兩個不同的列。每列擁有獨立的快速進位鏈資源。

slice分為兩種類型 SLICEL, SLICEM

(1)SLICEL可用于產(chǎn)生邏輯,算術(shù),ROM。

(2)SLICEM除以上作用外還可配置成分布式RAM或32位的移位寄存器。每個CLB可包含兩個SLICEL或者一個SLICEL與一個SLICEM.

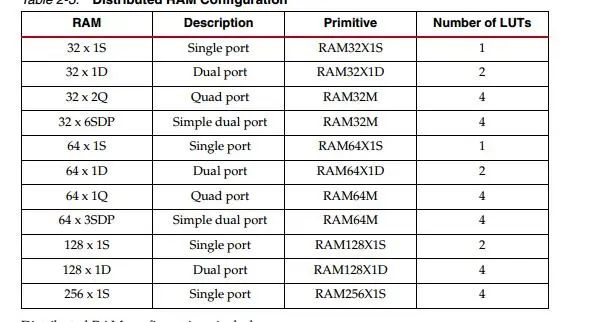

分布式RAM

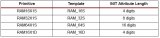

SLICEM可以配置成分布式RAM,一個SLICEM可以配置成以下容量的RAM

多bit的情況需要增加相應倍數(shù)的LUT進行并聯(lián)。

分布式RAM和 BLOCK RAM的選擇遵循以下方法:

1. 小于或等于64bit容量的的都用分布式實現(xiàn)

2. 深度在64~128之間的,若無額外的block可用分布式RAM。要求異步讀取就使用分布式RAM。數(shù)據(jù)寬度大于16時用block ram.

3. 分布式RAM有比block ram更好的時序性能。分布式RAM在邏輯資源CLB中。而BLOCK RAM則在專門的存儲器列中,會產(chǎn)生較大的布線延遲,布局也受制約。

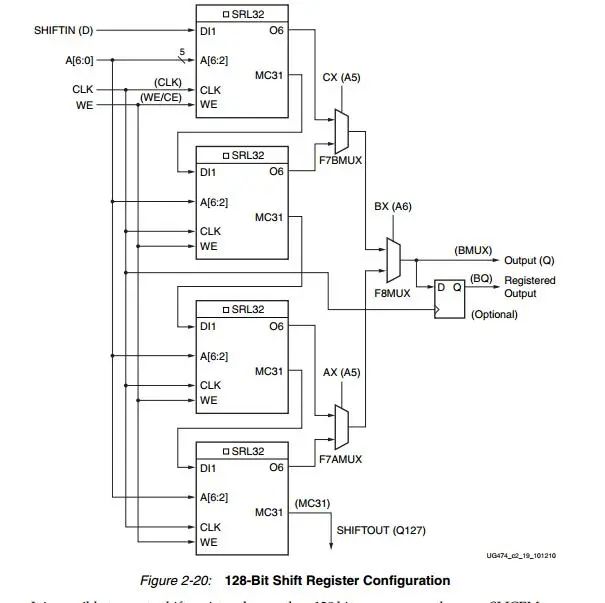

移位寄存器(SLICEM)

SLICEM中的LUT能在不使用觸發(fā)器的情況下設置成32bit的移位寄存器, 4個LUT可級聯(lián)成128bit的移位寄存器。并且能夠進行SLICEM間的級聯(lián)形成更大規(guī)模的移位寄存器。

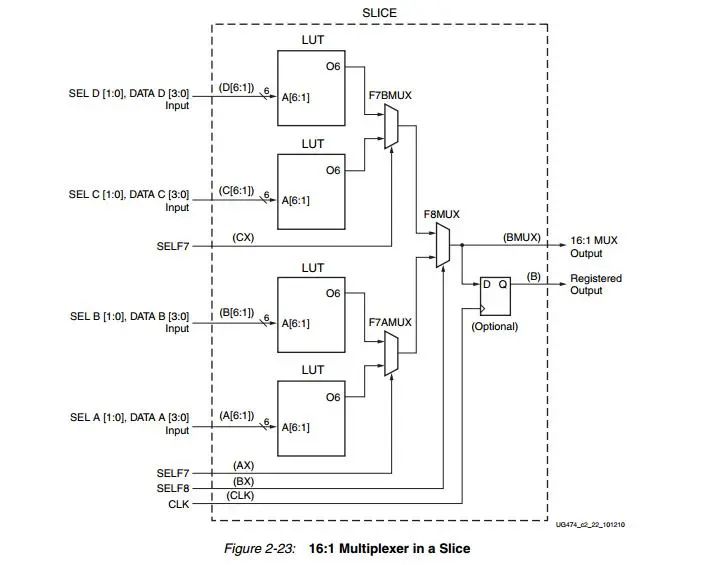

MUX

一個LUT可配置成4:1MUX.

兩個LUT可配置成最多8:1 MUX

四個LUT可配置成16個MUX

同樣可以通過連接多個SLICES達成更大規(guī)模設計,但是由于SLICE沒有直接連線,需要使用布線資源,會增加較大延遲。

進位鏈

每個SLICE有4bit的進位鏈。每bit都由一個進位MUX(MUXCY)和一個異或門組成,可在實現(xiàn)加法/減法器時生成進位邏輯。該MUXCY與XOR也可用于產(chǎn)生一般邏輯。

設計中我們可以用vivado查看設計底層的LUT實現(xiàn)圖,具體的差看方法https://blog.csdn.net/qijitao/article/details/51371434

二、LUT實現(xiàn)原理

LUT中文名字叫查找表。以7系列的FPGA為例,每一個Slice里面有四個LUT。FPGA就是通過LUT實現(xiàn)大量的組合邏輯,以及SLICEM里面的LUT還可以構(gòu)成RAM,Shift Register,以及Multiplexers。這篇文章我們一起來學習LUT如何構(gòu)成組合邏輯。

LUT,中文名字叫做查找表,其原理其實也就是一個一個查找表,根據(jù)輸入去找到相應位置的信號,然后做輸出。說白了就好像一個小容量的ROM,把輸入當作地址信號,對LUT里面預存的內(nèi)容進行尋址。

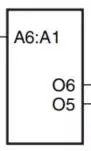

7系列的FPGA的LUT有6個輸入端口(A1-6),然后有兩個輸出端口(O5,O6)。下圖是SLICEL里面的LUT。

其可以實現(xiàn)6輸入的布爾組合邏輯函數(shù),輸入信號為A1,A2,A3,A4,A5,A6,輸出端口為O6。如下

O6=f(A1,A2,A3,A4,A5,A6)

其實現(xiàn)方式就是將輸入(A1,A2…A6)對應的輸出在LUT里面預存好(這一步在我們用bit文件配置FPGA時實現(xiàn)),然后把輸入信號當作地址信號去把對應的輸出信號調(diào)出來。

同樣其還可以構(gòu)成兩個5輸入的布爾組合邏輯函數(shù),其中這兩個函數(shù)共用5個輸入信號(A1,A2,A3,A4,A5),A6被拉高,O5,O6分別是兩個布爾邏輯的輸出。

O5=f(A1,A2,A3,A4,A5)

O6=f(A1,A2,A3,A4,A5)

故這也相當于實現(xiàn)的是一個5輸入2輸出的邏輯函數(shù)。

[O5,O6]=f(A1,A2,A3,A4,A5)

二、LUT提升

總結(jié)一下,就好比單個LUT里面可以預存 2^6=64個結(jié)果。那么單個LUT可以實現(xiàn)

(1)輸入信號最多為6bit,輸出信號為1bit的的布爾邏輯函數(shù);

(2)輸入信號最多為5bit,輸出信號為2bit的邏輯。

一個SLICE里面有四個LUT故最多可以預存的輸出信號個數(shù)為 26*4=28。

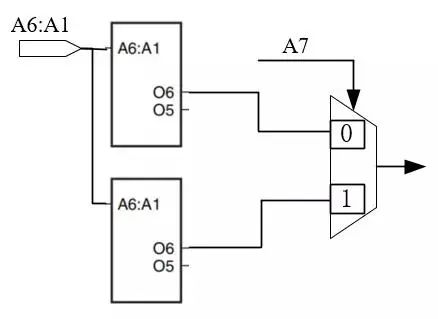

因此在一個SLICE里面,借助選擇器將多個LUT進行互連,可以實現(xiàn)輸入數(shù),輸出數(shù)最多為如下所示的邏輯。

(1)2個LUT通過互連可以構(gòu)成7bit輸入,單bit輸出的邏輯。實現(xiàn)方式為兩個LUT的輸入信號A1,A2,A3,A4,A5,A6接到一起,輸出信號經(jīng)過選擇器選擇輸出,選擇器的選擇信號也是邏輯函數(shù)的一個輸入信號。

將邏輯函數(shù)的輸出送到Storage Element便可以形成同步時序邏輯。

(2)4個LUT通過互連可以構(gòu)成8bit輸入,單bit輸出的邏輯。實現(xiàn)方式大家可以根據(jù)上面的實現(xiàn)方式自行推理。

(3)2個LUT通過互連可以構(gòu)成6bit輸入,2bit輸出的邏輯。實現(xiàn)方式自行推理。

(4)4個LUT通過互連可以構(gòu)成7bit輸入,2bit輸出的邏輯。實現(xiàn)方式自行推理。

審核編輯 :李倩

-

FPGA設計

+關(guān)注

關(guān)注

9文章

428瀏覽量

26642 -

RAM

+關(guān)注

關(guān)注

8文章

1369瀏覽量

115065 -

分布式

+關(guān)注

關(guān)注

1文章

925瀏覽量

74624

原文標題:FPGA學習- LUT查找表原理和編程方式

文章出處:【微信號:gh_9d70b445f494,微信公眾號:FPGA設計論壇】歡迎添加關(guān)注!文章轉(zhuǎn)載請注明出處。

發(fā)布評論請先 登錄

相關(guān)推薦

分布式軟件系統(tǒng)

FPGA中LUT設計

在FPGA中的RAM有與其他產(chǎn)品有什么不同?

分布式RAM中怎么異步讀取

分布式RAM綜合問題

如何利用FPGA設計無線分布式采集系統(tǒng)?

請問分布式RAM和Block RAM的芯片中有menexternalmemory或內(nèi)存嗎?

分布式RAM和Block RAM之間究竟有什么區(qū)別?

在FPGA設計中如何用LUT組建分布式的RAM

3系列FPGA中使用LUT構(gòu)建分布式RAM(2)

3系列FPGA中使用LUT構(gòu)建分布式RAM(3)

在FPGA設計中可以用LUT組建分布式的RAM

在FPGA設計中可以用LUT組建分布式的RAM

評論