基于SelectIO的高速ADC時序實現

引言

??本文通過以高速ADS42LB69芯片為例進行實戰,利用SelectIO IP快速快速高效完成驅動的生成。關于SelectIO IP的使用,可以參考。

ADS42LB69

芯片簡介

??ADS42LB49和ADS42LB69是高線性度、雙通道、14 和 16 位 250MSPS 模式轉換器 (ADC) 系列,支持 DDR 和 QDR LVDS 輸出接口。已緩沖模擬輸入在大大減少采樣保持毛刺脈沖能量的同時,在寬頻率范圍內提供統一的輸入阻抗。采樣時鐘分頻器可實現更靈活的系統時鐘 架構設計。ADS42LBx9 以低功耗在寬輸入頻率范圍內 提供出色的無雜散動態范圍 (SFDR)。

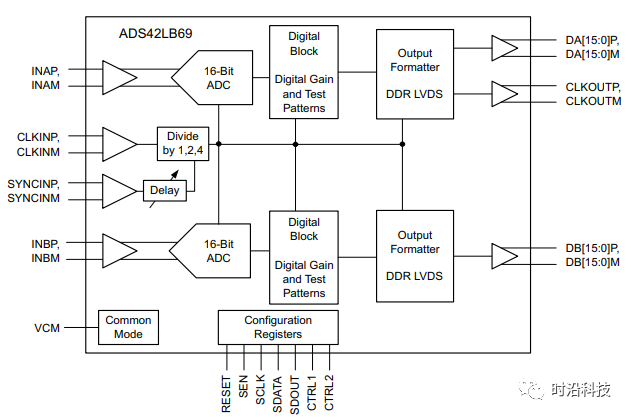

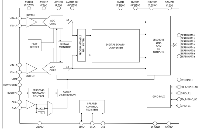

ADS42LB69功能框圖

ADS42LB69功能框圖

雙通道

14和16位分辨率

最大時鐘速率:250MSPS

支持高阻抗輸入的模擬輸入緩沖器

支持1分頻,2分頻和4分頻的靈活輸入時鐘緩沖器

2VPP和2.5VPP差分滿量程輸入(SPI可編程)

雙倍數據速率(DDR)或四倍數據速率(QDR)低壓差分信令(LVDS)接口

功耗:820mW/通道

間隙抖動:85 fs

通道隔離:100dB

參數配置

??用戶可以根據自己的需求將數據接口通過SPI配置成QDR或DDR接口。在進行數據驗證時,也可以使用測試模式,對收發數據進行驗證以保證系統的正確性。另外,還可以對輸入時鐘進行延時調節或者通過SelectIO的delay、delayctrl功能對時鐘信號進行微調,以滿足時序要求。此方面不是本文重點,不做展開,更多內容參考官方data sheet。

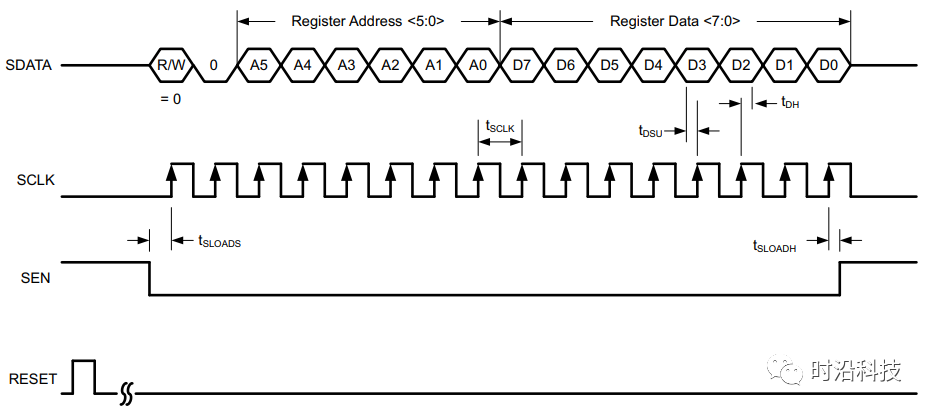

SPI時序

SPI時序引腳

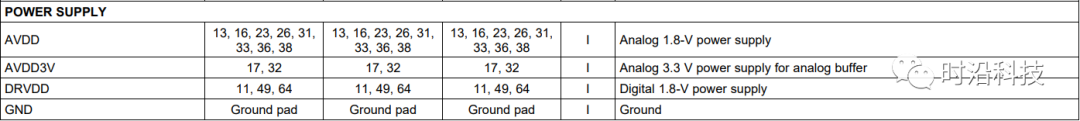

??從下圖可以看到,數據接口引腳采用1.8V供電,故數據接口為差分1.8V。

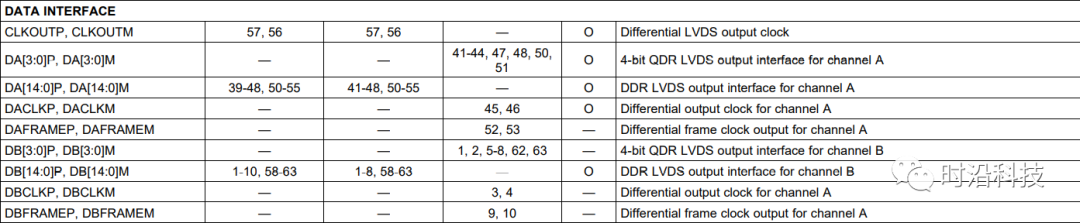

數據端口信號

數據端口信號接口時序

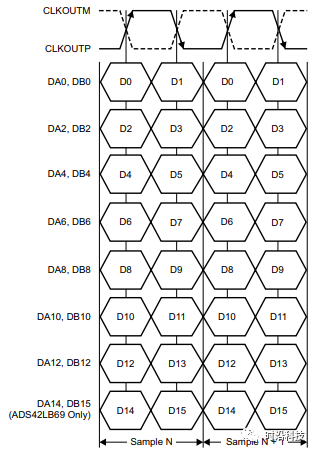

??下圖為ADS42LB69的DDR模式時序圖,從圖中可以看出有1對時鐘接口,兩個8對數據接口(DA與DB),每對數據接口分別在時鐘的上升沿與下降沿采樣,經過一個時鐘周期可以捕獲16位數據。

ADS42LB69的DDR模式時序圖

ADS42LB69的DDR模式時序圖SelectIO GUI配置

??根據以上對ads42lb69的了解,就可以輕松的配置SelectIO IP的GUI界面了。

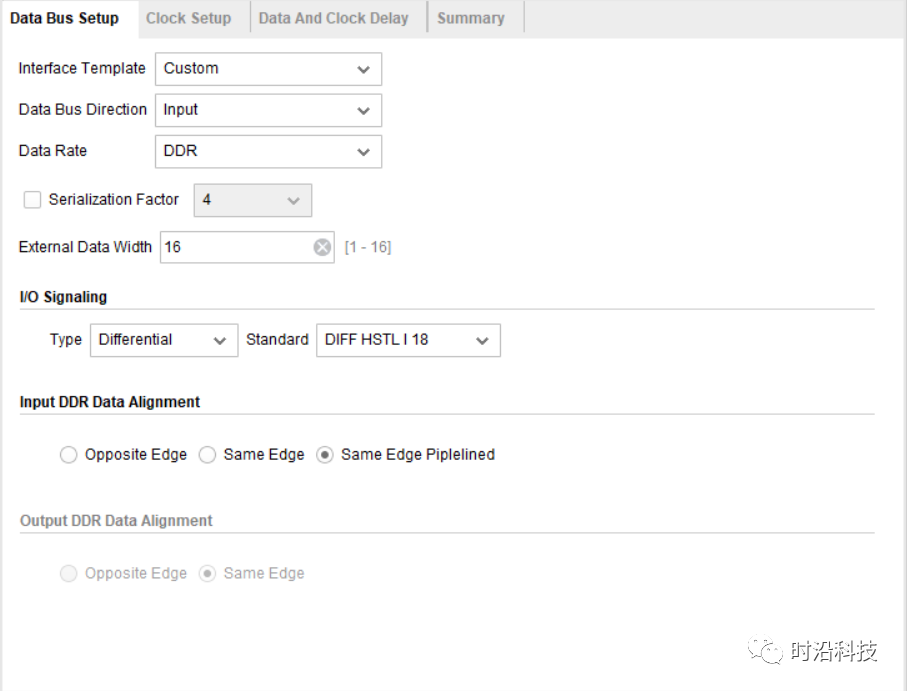

首先時鐘接口與數據接口都是input,該時鐘信號與RF模塊時鐘必須保持同源,以保證系統的相參性。由于ads42lb69采用DDR模式,且所有數據引腳都是并行,所以不選擇串并轉換器SERDES。

Data Bus Setup界面

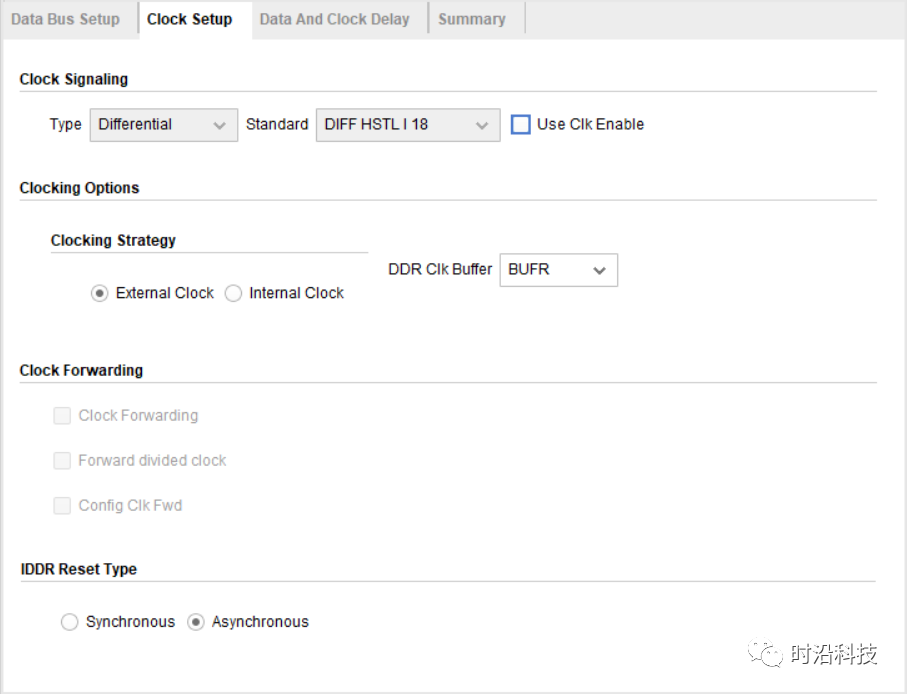

Data Bus Setup界面??由于數據時鐘來源于ads42lb69引腳,故選擇外部時鐘,而非FPGA內部時鐘。

Clock Setup界面

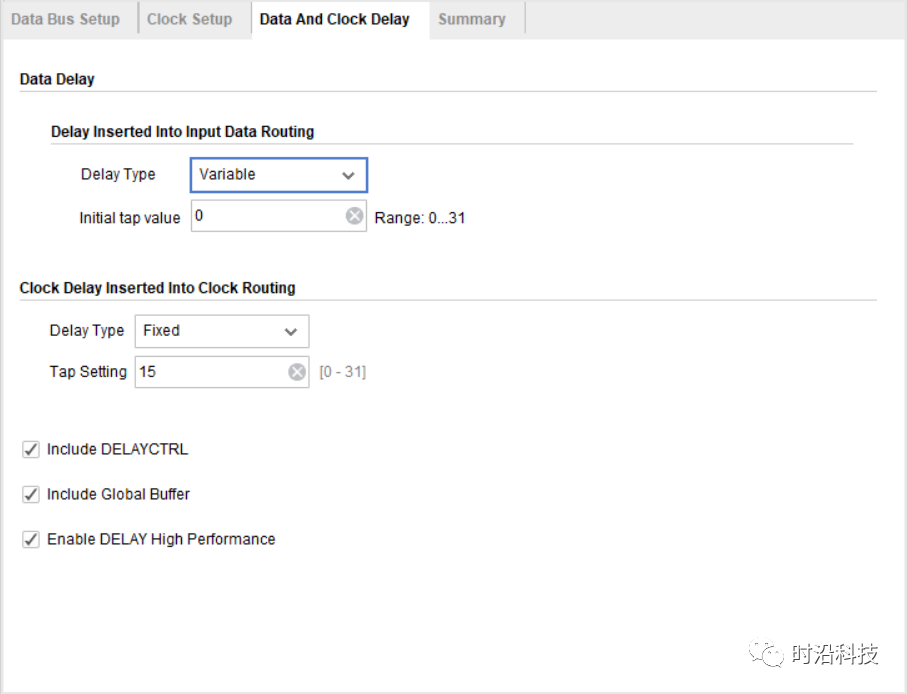

Clock Setup界面??在實際處理高速數據時,往往存在由于布局布線導致的數據引腳之間的延時不相同,可以通過在每個數據引腳添加idelay、delayctrl模塊對齊進行微調。或者,存在數據引腳與時鐘引腳之間不對齊,通常對時鐘引腳添加idelay、delayctrl模塊對其進行微調。

Data And Clock Delay界面

Data And Clock Delay界面??IP生成之后,通過右擊選擇Open IP Example Design進行仿真以加強理解,在線DEBUG調試延時模塊,以達到設計要求。

-

芯片

+關注

關注

459文章

52306瀏覽量

437765 -

adc

+關注

關注

99文章

6659瀏覽量

548532 -

時序

+關注

關注

5文章

397瀏覽量

37835

原文標題:基于SelectIO的高速ADC時序實現

文章出處:【微信號:zhuyandz,微信公眾號:FPGA之家】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

AN-1267: 使用ADSP-CM408F ADC控制器的電機控制反饋采樣時序

高速adc與低功耗adc的區別

問能否通過GUI軟件使得ADC3664EVM在每一個FCLK期間都重復輸出同樣的值呢?

高速ADC設計中采樣時鐘影響的考量

高速ADC與FPGA的LVDS數據接口中避免時序誤差的設計考慮

ADC12D1800 12位、單通道3.6 GSPS超高速ADC數據表

輕松實現復雜的電源時序控制

基于SelectIO的高速ADC時序實現

基于SelectIO的高速ADC時序實現

評論