對(duì)于實(shí)時(shí)系統(tǒng),尤其是對(duì)安全至關(guān)重要的系統(tǒng),多核處理器由于對(duì)處理器內(nèi)核之間共享資源的爭(zhēng)用,對(duì)嚴(yán)格的確定性提出了重大挑戰(zhàn)。

嵌入式系統(tǒng)在更高的吞吐量和更好的尺寸、重量和功率 (SWaP) 方面受益于多核處理器的使用。具有異構(gòu)處理器內(nèi)核的處理器增加了將應(yīng)用程序與每種內(nèi)核類型的功能相匹配的能力,進(jìn)一步提高了吞吐量和 SWaP。多核處理器的優(yōu)勢(shì)在于軟件架構(gòu)的復(fù)雜性增加,以最大限度地利用處理器內(nèi)核。對(duì)于實(shí)時(shí)系統(tǒng),尤其是對(duì)安全至關(guān)重要的系統(tǒng),多核處理器由于對(duì)處理器內(nèi)核之間共享資源的爭(zhēng)用,對(duì)嚴(yán)格的確定性提出了重大挑戰(zhàn)。這一挑戰(zhàn)隨著異構(gòu)內(nèi)核的增加而增加,因?yàn)樽顗那闆r下的執(zhí)行時(shí)間可能會(huì)因應(yīng)用程序執(zhí)行的內(nèi)核而異。

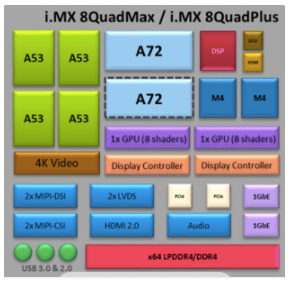

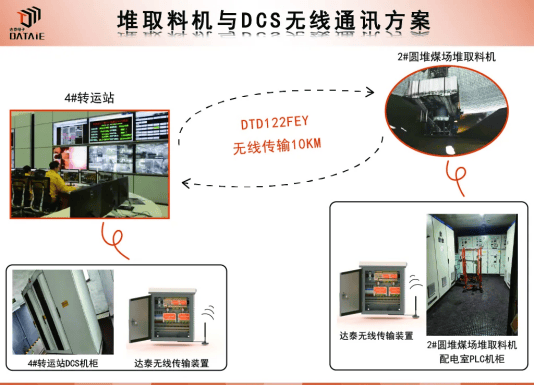

要更詳細(xì)地探索這種權(quán)衡,請(qǐng)考慮 NXP? i.MX 8QuadMax 應(yīng)用處理器中的異構(gòu)內(nèi)核(圖 1)。i.MX 8QuadMax 具有四個(gè) Arm? Cortex?-A53 內(nèi)核和兩個(gè) Cortex-A72 內(nèi)核,可通過(guò)將每個(gè)應(yīng)用任務(wù)的性能要求與不同內(nèi)核的性能容量相匹配來(lái)實(shí)現(xiàn)功耗優(yōu)化。與 A53 核心相比,A72 核心提供大約兩倍的性能,但功耗更高。

圖 1:NXP i.MX 8 架構(gòu)

為了實(shí)現(xiàn)多核解決方案的吞吐量和 SWaP 優(yōu)勢(shì),軟件架構(gòu)需要支持可用處理器內(nèi)核的高利用率。必須支持所有多核功能,從啟用內(nèi)核的并發(fā)操作(相對(duì)于可用內(nèi)核被強(qiáng)制進(jìn)入空閑狀態(tài)或在啟動(dòng)時(shí)保持重置)到提供確定性負(fù)載平衡機(jī)制。軟件多處理架構(gòu)越靈活,系統(tǒng)架構(gòu)師實(shí)現(xiàn)高利用率所需的工具就越多。

軟件多處理架構(gòu)

與多處理器系統(tǒng)一樣,多核處理器上的軟件架構(gòu)可以根據(jù)內(nèi)核之間共享和協(xié)調(diào)的數(shù)量進(jìn)行分類。基于多核的系統(tǒng)最簡(jiǎn)單的軟件架構(gòu)是非對(duì)稱多處理 (AMP),其中每個(gè)內(nèi)核獨(dú)立運(yùn)行,每個(gè)內(nèi)核都有自己的操作系統(tǒng)或管理程序/客戶操作系統(tǒng)對(duì)。每個(gè)核心運(yùn)行不同的應(yīng)用程序,核心之間在調(diào)度方面很少或沒(méi)有有意義的協(xié)調(diào)。由于缺乏負(fù)載平衡、難以緩解共享資源爭(zhēng)用以及無(wú)法跨核心執(zhí)行協(xié)調(diào)活動(dòng)(例如綜合內(nèi)置測(cè)試所需的),這種解耦可能導(dǎo)致利用率不足。

AMP 的現(xiàn)代替代方案是對(duì)稱多處理 (SMP),其中單個(gè)操作系統(tǒng)控制所有資源,包括哪些應(yīng)用程序線程在哪些內(nèi)核上運(yùn)行。這種架構(gòu)易于編程,因?yàn)樗袃?nèi)核都“對(duì)稱”地訪問(wèn)資源,從而使操作系統(tǒng)可以將任何線程分配給任何內(nèi)核。對(duì)于具有異構(gòu)內(nèi)核的處理器,例如 i.MX 8QuadMax,不知道應(yīng)用程序?qū)⒃谀姆N類型的內(nèi)核上運(yùn)行可能會(huì)導(dǎo)致執(zhí)行時(shí)間范圍廣泛,從而顯著影響確定性性能。

綁定多處理 (BMP) 直接解決了這個(gè)問(wèn)題,它是一種增強(qiáng)型和受限形式的 SMP,它將應(yīng)用程序的任務(wù)/線程靜態(tài)綁定到特定內(nèi)核。這種靜態(tài)綁定允許系統(tǒng)架構(gòu)師嚴(yán)格控制多個(gè)內(nèi)核的并發(fā)操作。

確保確定性行為

除了實(shí)現(xiàn)多核處理器的吞吐量和 SWaP 目標(biāo)外,安全關(guān)鍵系統(tǒng)還需要為每個(gè)應(yīng)用程序保持可預(yù)測(cè)的最壞情況執(zhí)行時(shí)間 (WCET)。使用 BMP 限制與應(yīng)用程序配對(duì)的內(nèi)核類型是確保異構(gòu)系統(tǒng)中確定性行為的重要組成部分。確保確定性的其他技術(shù)是時(shí)間和空間分區(qū)以及管理共享資源的爭(zhēng)用。

在單核處理器中,多個(gè)安全關(guān)鍵應(yīng)用程序可以通過(guò)在托管應(yīng)用程序之間穩(wěn)健地劃分內(nèi)存空間來(lái)在同一處理器上執(zhí)行。內(nèi)存空間分區(qū)將內(nèi)存的非重疊部分專用于在給定時(shí)間運(yùn)行的每個(gè)應(yīng)用程序,由處理器的內(nèi)存管理單元 (MMU) 強(qiáng)制執(zhí)行。確定性可以通過(guò)使用時(shí)間劃分來(lái)進(jìn)一步增強(qiáng),時(shí)間劃分將一個(gè)固定的時(shí)間間隔(稱為主幀)劃分為一系列固定的子間隔,稱為劃分時(shí)間窗口。每個(gè)應(yīng)用程序都分配有一個(gè)或多個(gè)分區(qū)時(shí)間窗口,窗口的長(zhǎng)度和數(shù)量由應(yīng)用程序的 WCET 和所需的重復(fù)率決定。

多核干擾挑戰(zhàn)確定性

在多核環(huán)境中,可以有多個(gè)應(yīng)用程序在不同的內(nèi)核上同時(shí)運(yùn)行。這些并發(fā)應(yīng)用程序每個(gè)都需要訪問(wèn)處理器的資源。每個(gè)處理核心都有一些專用資源,但大多數(shù)資源在處理器核心之間共享,包括內(nèi)存控制器、I/O、共享緩存以及連接它們的內(nèi)部結(jié)構(gòu)。當(dāng)多個(gè)處理器內(nèi)核嘗試同時(shí)訪問(wèn)同一資源時(shí),會(huì)導(dǎo)致這些共享資源的爭(zhēng)用。在航空電子設(shè)備等安全關(guān)鍵型應(yīng)用程序中,主要問(wèn)題是這種共享資源爭(zhēng)用如何導(dǎo)致運(yùn)行在一個(gè)內(nèi)核上的應(yīng)用程序干擾運(yùn)行在另一個(gè)內(nèi)核上的應(yīng)用程序,從而對(duì)確定性、服務(wù)質(zhì)量以及最終的安全性產(chǎn)生負(fù)面影響。

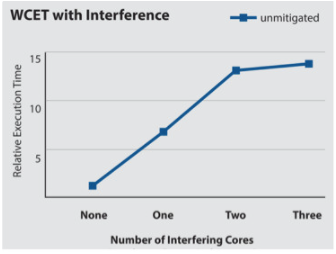

如果不加以緩解,共享資源爭(zhēng)用的影響可能會(huì)很大。僅檢查其中一種共享資源 DDR 內(nèi)存,人們可能會(huì)猜測(cè),當(dāng)另一個(gè)內(nèi)核嘗試訪問(wèn)同一內(nèi)存并且兩個(gè)內(nèi)核都運(yùn)行內(nèi)存受限的應(yīng)用程序時(shí),WCET 可能會(huì)翻倍。實(shí)際上,由于共享資源仲裁和調(diào)度算法中的非線性行為,WCET 可以增加 8 倍而不是 2 倍。嘗試訪問(wèn) DDR 內(nèi)存或爭(zhēng)奪其他資源(例如片上互連)的其他內(nèi)核可能會(huì)導(dǎo)致 WCET 增長(zhǎng)得更加顯著(圖 2)。

圖 2:多核干擾的增加速度快于核心數(shù)量。

多核干擾緩解

減輕多核干擾的一種方法是手動(dòng)調(diào)度應(yīng)用程序以最小化資源爭(zhēng)用。這種方法不會(huì)消除所有干擾,并且任何時(shí)候修改任何單個(gè)應(yīng)用程序或添加新應(yīng)用程序都需要重新測(cè)試和驗(yàn)證所有應(yīng)用程序。另一種方法是安排一次只運(yùn)行一個(gè)多任務(wù)應(yīng)用程序。任務(wù)之間仍然會(huì)發(fā)生干擾,但不會(huì)對(duì)其他應(yīng)用程序產(chǎn)生干擾。這種方法在具有異構(gòu)內(nèi)核的處理器上尤其無(wú)效,因?yàn)椴煌瑑?nèi)核類型的執(zhí)行時(shí)間不同。

更通用的方法是讓操作系統(tǒng)管理共享資源爭(zhēng)用。與操作系統(tǒng)使用硬件 MMU 通過(guò)將不同的內(nèi)存區(qū)域分配給不同的應(yīng)用程序來(lái)實(shí)現(xiàn)空間分區(qū)的方式相同,操作系統(tǒng)可以按內(nèi)核為共享資源分配帶寬。解決操作系統(tǒng)中的多核干擾為系統(tǒng)集成商提供了有效、靈活和敏捷的解決方案。它還簡(jiǎn)化了新應(yīng)用程序的添加,而無(wú)需對(duì)系統(tǒng)架構(gòu)進(jìn)行重大更改,并減少了重新驗(yàn)證活動(dòng)。

航空電子設(shè)備中異構(gòu)核心的示例解決方案

NXP i.MX 8QuadMax 應(yīng)用處理器包括四個(gè)共享 1MB L2 緩存的 Arm Cortex-A53 內(nèi)核和兩個(gè)共享另一個(gè) 1MB L2 緩存的 Arm Cortex-A72 內(nèi)核。該處理器還包括兩個(gè)用于卸載系統(tǒng)功能的 Cortex-M4F 內(nèi)核和兩個(gè)能夠運(yùn)行 OpenCL、Vulkan 和 OpenVX 視覺(jué)加速的 GPU。i.MX 8 的一項(xiàng)獨(dú)特功能是硬件資源分區(qū),其中系統(tǒng)控制器將外圍設(shè)備和內(nèi)存區(qū)域提交到特定的客戶定義域中。域之間的任何通信都被迫使用通過(guò)硬件消息單元運(yùn)行的消息協(xié)議。i.MX8QuadMax 面向廣泛的應(yīng)用,包括工業(yè) HMI(人機(jī)界面)和控制、電子駕駛艙 (eCockpit)、平視顯示器、樓宇自動(dòng)化和單板計(jì)算機(jī)。

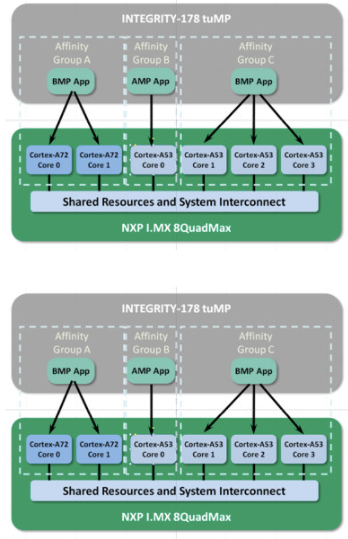

綠山的誠(chéng)信?-178 tuMP? 多核 RTOS 是一個(gè)統(tǒng)一的操作系統(tǒng),可在 i.MX 8 中的所有 64 位處理器內(nèi)核上運(yùn)行,并支持 AMP、SMP 和 BMP 的同時(shí)組合。RTOS 的時(shí)變統(tǒng)一多處理 (tuMP) 方法為將安全關(guān)鍵型和安全關(guān)鍵型應(yīng)用程序移植、擴(kuò)展和優(yōu)化到多核架構(gòu)提供了最大的靈活性。INTEGRITY-178 tuMP 使用跨所有內(nèi)核運(yùn)行的時(shí)間分區(qū)內(nèi)核,允許應(yīng)用程序綁定到一個(gè)內(nèi)核或稱為關(guān)聯(lián)組的內(nèi)核組。如果需要,可以進(jìn)一步限制關(guān)聯(lián)組中應(yīng)用程序的每個(gè)任務(wù)以在特定核心上運(yùn)行。對(duì)于 i.MX 8QuadMax 處理器,

圖 3:使用 Affinity Groups,一個(gè)應(yīng)用程序綁定到兩個(gè) Cortex-A72 內(nèi)核,而另外兩個(gè)應(yīng)用程序綁定到一組 Cortex-A53 內(nèi)核。

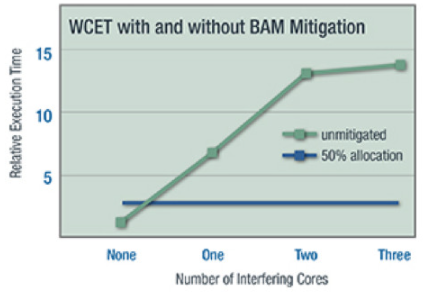

INTEGRITY-178 tuMP 直接解決多核干擾,包括開(kāi)發(fā)到最嚴(yán)格安全級(jí)別的帶寬分配和監(jiān)控 (BAM) 功能。BAM 功能監(jiān)控并強(qiáng)制分配來(lái)自每個(gè)處理器內(nèi)核的共享資源的帶寬。BAM 模擬一種基于硬件的高速方法,以確保對(duì)每個(gè)核心對(duì)共享資源的使用進(jìn)行連續(xù)分配強(qiáng)制。BAM 在整個(gè)應(yīng)用程序的執(zhí)行時(shí)間窗口中平滑地調(diào)節(jié)帶寬,從而允許同一執(zhí)行時(shí)間窗口中的其他應(yīng)用程序獲取它們分配的共享資源部分。使用前面的內(nèi)存訪問(wèn)干擾示例,將 50% 的內(nèi)存帶寬分配給高關(guān)鍵應(yīng)用程序會(huì)導(dǎo)致幾乎恒定的 WCET,即使干擾內(nèi)核的數(shù)量增加,而當(dāng)存在多個(gè)干擾內(nèi)核時(shí),WCET 也會(huì)降低 8 倍(圖 4)。這種能力有效地減輕了多核干擾并大大降低了集成和認(rèn)證風(fēng)險(xiǎn),同時(shí)還使集成商能夠獲得多核處理器的最大性能優(yōu)勢(shì)。

圖 4:使用 BAM 將 50% 的共享資源帶寬分配給關(guān)鍵應(yīng)用程序后,WCET 幾乎保持不變并大大降低。

NXP i.MX 8QuadMax 為優(yōu)化航空電子設(shè)備和其他嵌入式實(shí)時(shí)系統(tǒng)中的 SWaP 提供了重要機(jī)會(huì)。Cortex-A72 和 Cortex-A53 內(nèi)核的結(jié)合使系統(tǒng)架構(gòu)師能夠強(qiáng)調(diào)性能或電源效率,從而創(chuàng)建最佳的系統(tǒng)級(jí)解決方案。相應(yīng)的軟件架構(gòu)需要具有靈活性和可控性,以充分利用這些異構(gòu)應(yīng)用內(nèi)核,同時(shí)保持嚴(yán)格的確定性。結(jié)合使用 Affinity Groups 或某種其他形式的 BMP 的能力以及多核干擾緩解解決方案(例如 BAM),可以在安全關(guān)鍵型應(yīng)用中有效使用 i.MX 8QuadMax。

審核編輯:郭婷

-

處理器

+關(guān)注

關(guān)注

68文章

19831瀏覽量

233878 -

嵌入式

+關(guān)注

關(guān)注

5143文章

19570瀏覽量

315679 -

NXP

+關(guān)注

關(guān)注

61文章

1336瀏覽量

187766

發(fā)布評(píng)論請(qǐng)先 登錄

智多晶PLL使用注意事項(xiàng)

IGBT器件的防靜電注意事項(xiàng)

BNC 接頭阻抗匹配:接線中的關(guān)鍵技術(shù)與注意事項(xiàng)

交流負(fù)載箱的安全事項(xiàng)和注意事項(xiàng)有哪些?

脈沖式充電器的使用注意事項(xiàng)

繞線電感定制的注意事項(xiàng)

漏電保護(hù)器的正確使用和注意事項(xiàng)

共模電感定制的注意事項(xiàng)

LiFePO4設(shè)計(jì)注意事項(xiàng)

光纖收發(fā)器的使用方法和注意事項(xiàng)

如何確保PLC系統(tǒng)安全的可靠性,這幾個(gè)注意事項(xiàng)你需要牢記

安全關(guān)鍵應(yīng)用中異構(gòu)臂核心的軟件注意事項(xiàng)

安全關(guān)鍵應(yīng)用中異構(gòu)臂核心的軟件注意事項(xiàng)

評(píng)論