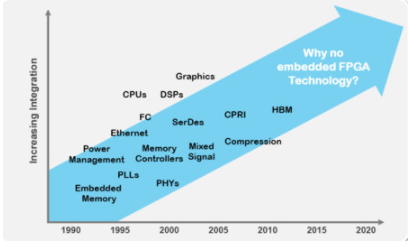

越集成越好。這在嵌入式領域比以往任何時候都更加真實。為了證明,請查看片上系統 (SoC) 格局。

在過去 20 年中,SoC 集成度穩步提高,最初包括嵌入式存儲器和電源管理模塊,現在集成了從模擬和混合信號 IP 到圖形和數字信號協處理器再到安全和連接子系統的所有內容(圖 1)。對于更高性能的應用,這一進程的下一步是啟用具有硬件加速功能的 SoC,從而引入下一代 SoC IP——嵌入式現場可編程門陣列 (eFPGA)。

【圖1 | 片上系統 (SoC) IP 集成的演進。]

加速向嵌入式 FPGA IP 發展

FPGA 于 1980 年代推出,其靈活性使其立即適用于需要晶體管-晶體管邏輯 (TTL) 集成和可編程 I/O 的設計,作為現成的特定應用標準產品 (ASSP) 和特定應用集成電路 (ASIC) 并不總是配備給定系統所需的端口。再加上隨后幾年不斷增長的連接需求,這種靈活性使 FPGA 用于連接數據中心中的處理器陣列,也被部署為單獨的協處理器,以計算各種信號處理應用程序中復雜的自定義并行工作負載。更廣泛的使用和曝光導致 FPGA 密度、性能和成本的提高,并且該技術的市場從 1987 年的 1400 萬美元激增到 2013 年的近 54 億美元。

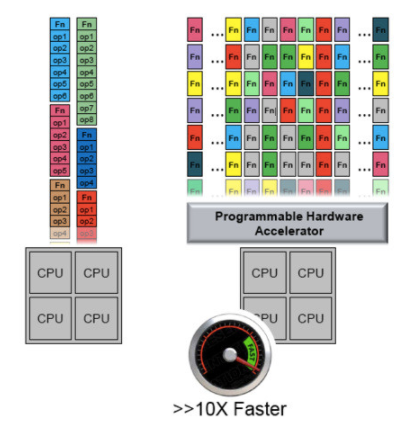

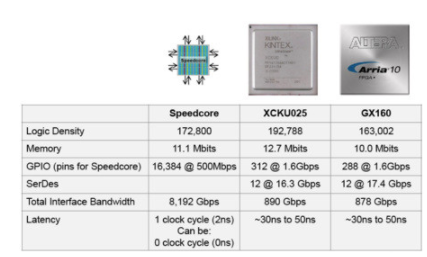

隨著當今的數據中心和網絡應用繼續推動對更低延遲和更高性能的不懈需求,芯片制造商已開始研究將 FPGA IP 直接集成到其 SoC 設計中的好處。曾經被認為過于困難和過于昂貴,將可編程硬件加速塊實現到 SoC 中的計算優勢是不可否認的,因為 FPGA 不依賴于多核 CPU 的不可擴展的順序處理范例,而是能夠在一個單一的時鐘周期(圖2)。僅英特爾就提供了這種趨勢的雙重例子,因為 2015 年該公司收購了 FPGA 巨頭 Altera 以保持其在數據中心市場的主導地位,

【圖2 | 通過 FPGA IP 將可編程硬件加速塊集成到 SoC 中,與傳統的附加 CPU 串行處理相比,處理能力提高了 10 倍。]

但為什么所有的樂趣都應該僅限于英特爾呢?它不是。最近,Achronix Semiconductor 發布了其 Speedcore eFPGA IP。

利用靈活性的力量

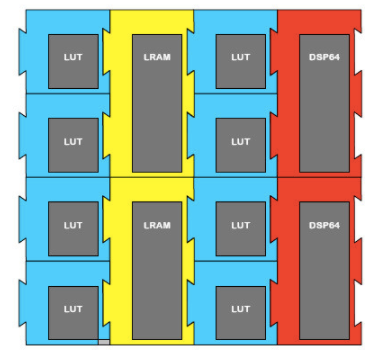

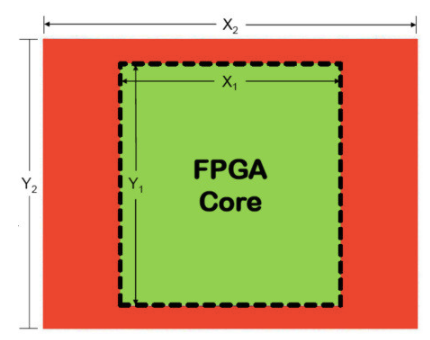

Speedcore eFPGA IP 已經醞釀了三年,其中大部分時間都在應對挑戰,即制造一種具有內在靈活性的技術,而且足夠堅固,可以在各種 SoC 設計中快速實施。為實現這一目標,Achronix 工程師采用了模塊化架構方法,允許高效開發尺寸獨特的 FPGA 內核結構,所有功能塊均采用標準接口路由和單元尺寸(圖 3)。因此,可以將 Speedcore IP 設想為支持多種時序收斂方法的“類似樂高”的 IP 組合、無需電源排序要求的共享或單獨電源選項,以及構建可變寬度數據路徑的能力。

【圖3 | Achronix Speedcore 嵌入式 FPGA IP (eFPGA) 基于“類樂高”架構,允許 SoC 設計人員自定義查找表、DSP 和內存塊、I/O 端口和電源的數量。]

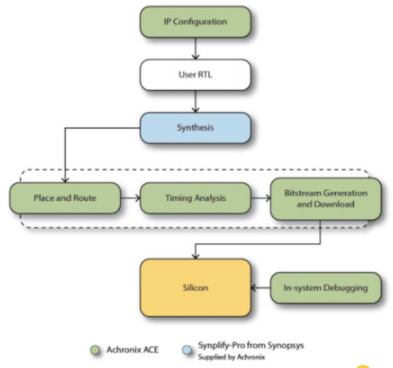

【圖4 | Speedcore eFPGA IP 可使用 Achronix 的 ACE 設計工具進行配置,該工具支持常見的電子設計自動化 (EDA) 流程。]

雖然 FPGA 架構可以為 SoC 提供強大的馬力,如前所述,但將其作為 IP 嵌入具有一些可能不會立即顯現的輔助優勢。這些都源于這樣一個事實,即 Speedcore 等技術是作為 IP 而不是分立芯片實現的,從而降低了電路板尺寸、功耗、成本和延遲。

首先,就電路板尺寸而言,大約 50% 的典型 FPGA 占位面積專用于可編程 I/O、SerDes 連接器和接口控制器,所有這些都是可有可無的,因為必要的 I/O 作為核心 FPGA 的一部分存在使用直接導線連接到 SoC 的結構(圖 5)。此外,還可以省去電源調節器、時鐘發生器和單獨的冷卻設備等外圍組件。

【圖5 | 通過消除獨立 FPGA 所需的 SerDes 連接器、接口控制器和其他組件,Speedcore eFPGA IP 可以減少電路板尺寸、延遲、功耗和成本。]

因此,印刷電路板 (PCB) 占用空間的減少、單獨芯片的缺失以及其他支持組件的移除有助于降低整體系統成本(根據 Achronix 的數據,高達 90%)。此外,更少的設備加上性能的提高可以讓處理任務更快地完成,這也有助于最大限度地降低功耗(該公司表示,功耗降低高達 50%)。

但回到性能方面,移除會增加延遲的 SerDes 連接器還允許直接從 FPGA 內核和主 CPU 構建寬寄存器接口路徑,從而最大限度地減少與獨立 FPGA 相關的通信瓶頸(圖 6)。

【圖6 | 在利用 eFPGA IP 的 SoC 設計中缺少 SerDes 連接器可以顯著降低分立 FPGA 解決方案的延遲。]

FPGA IP 能否進入您附近的 SoC?

Speedcore eFPGA IP 目前面向需要大量并行處理的應用,例如 5G 基站的數字前端 (DFE)、軟件定義網絡 (SDN) 和高性能云計算,但隨著數量的增加,我們能否期待在更深入的嵌入式應用中看到這種技術?

審核編輯:郭婷

-

FPGA

+關注

關注

1646文章

22054瀏覽量

618817 -

連接器

+關注

關注

99文章

15395瀏覽量

140647 -

soc

+關注

關注

38文章

4395瀏覽量

222871

發布評論請先 登錄

適用于Versal的AMD Vivado 加快FPGA開發完成Versal自適應SoC設計

FPGA IP是否可以用于附近的SoC

FPGA IP是否可以用于附近的SoC

評論