驗證 IP 不僅僅是功能。功能的交互、時間的可變性和測試策略都成為更廣泛的驗證策略的因素。

FPGA 在過去十年中不斷發展,變得更大、更復雜。為 FPGA 開發的知識產權 (IP) 在尺寸和復雜性方面同樣有所增加。為了應對這種日益增加的復雜性,IP 開發人員采用了一流的驗證方法。即使使用這些方法,為 FPGA 開發 IP 仍然會帶來典型 ASIC 設計人員可能不會遇到的獨特挑戰。

FPGA 開發提出了三個關鍵挑戰。一是 FPGA IP 通常是高度參數化的,這會產生大量的設計變體來進行測試。另一個問題是 FPGA IP 開發人員需要驗證一旦集成到用戶設計中就可以滿足時序要求。最后,為 FPGA 開發的 IP 比為其他平臺開發的 IP 更容易受到架構變化的影響。驗證環境以盡可能少的工作量適應這些架構更改非常重要。

參數化特征

FPGA 的每門成本高于相應的 ASIC,因此以 FPGA 為目標的設計人員有動力創建不消耗任何不必要資源的 IP。ASIC 將實現所有支持的功能,而 FPGA 可以選擇僅實現客戶需要的功能。因此,FPGA IP 可以而且應該進行參數化,以便綜合去除不需要的邏輯。例如,如果不需要以太網統計收集功能,Xilinx 10 GbE MAC 內核的大小將縮小約 25%,從而為其他邏輯釋放 FPGA 資源。

在確定將要參數化的內容時,數據總線寬度、流水線級數和可選功能等因素是很好的考慮因素,因為它們允許設計人員或客戶在性能和消耗的資源之間進行權衡。可以通過參數化特定于平臺的功能(如 Block RAM 和 DSP 塊)來進行進一步的權衡,而不是使用結構邏輯。

缺點是每個添加的參數都會創建另一個必須測試的排列。驗證工程師如何知道參數已針對所有值執行?最好的方法是收集覆蓋率統計數據并分析模擬器生成的覆蓋率報告。例如,如果設計具有控制 IP 是使用 32 位還是 64 位數據路徑的數據寬度 (DW) 參數和控制是否使用額外流水線來幫助滿足時序要求的流水線 (PL) 參數,帶有簡單覆蓋點的基本覆蓋率報告可能會顯示 DW 和 PL 的值都被執行了。但是,它不會顯示是否在沒有額外流水線的情況下測試了 64 位數據路徑。為了實現這一點,

對于大量參數,很快就會發現,如果允許隨機設置每個參數,那么命中每個排列將永遠持續下去。驗證工程師必須定義相關的參數排列子集,并且對最終客戶更有可能使用的參數排列權重很大。此外,應該選擇更好地執行設計的排列,例如那些導致完全 FIFO 條件或很少使用的狀態轉換的排列。約束隨機驗證非常適合此目的,因為它允許工具根據驗證者的約束隨機化參數值,并使用覆蓋率度量來查看是否命中了重要的排列。如果不是,則驗證者可以運行更多測試或更改約束值分布的權重。

驗證時間

FPGA IP 開發人員面臨的挑戰之一是確保 IP 一旦集成到客戶設計中就能夠滿足時序要求。由于難以對具有大參數空間的設計進行功能驗證,因此同樣難以理解參數對滿足時序能力的影響。開發人員面臨的另一個障礙是 IP 可能會與用戶設計的其他部分競爭 FPGA 架構資源,這會使滿足時序要求變得更加困難。

開發人員可以采用多種技術來幫助確保 IP 將繼續滿足時序要求,即使集成到用戶設計中也是如此。有代表性的示例設計很不錯,但不是必需的。如果示例設計不可用,請雙重注冊將進入 FPGA 架構的所有 I/O。芯片上或關閉的 I/O 應連接到適當的位置。

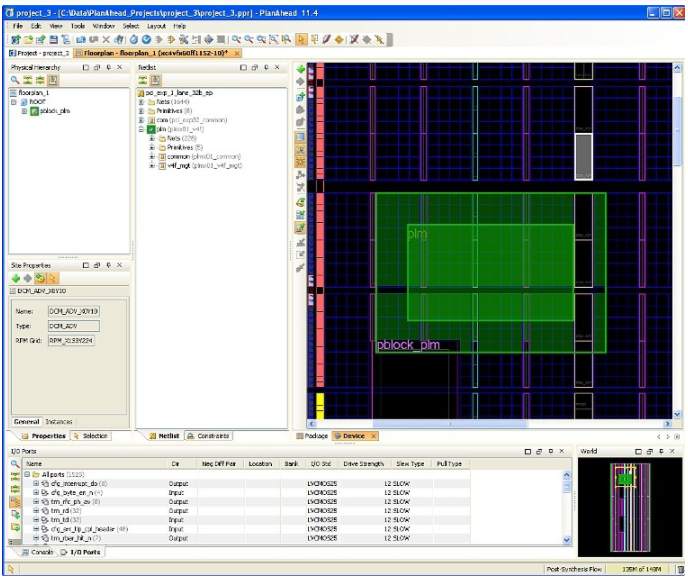

一旦設計到位,下一步就是在目標 FPGA 架構中實現設計。作為測試過程的一部分,將 IP 時鐘頻率過度約束 15%。此外,向 IP 添加一個區域約束,使其被約束到 FPGA 架構的一個區域,該區域不會比其最小布局需求大很多,如圖 1 所示。這將模擬 IP 集成到用戶設計。

圖 1: Xilinx PlanAhead 工具中的 IP 塊被限制在芯片的一個小區域內,以在將 IP 集成到設計中時模擬擁塞。

最后一步是確保不同的參數設置不會對滿足時序的能力產生不利影響。確定最有可能對時序收斂產生影響的關鍵參數。隨機化識別的參數,以區域約束和更高的時鐘頻率運行,并確保在 IP 目標的所有 FPGA 器件中仍然可以滿足時序要求。開發人員運行的參數組合越多,他們對 IP 即使在最困難的客戶環境中也能滿足時序要求的信心就越大。

將測試場景與實現分離

設計人員可能需要在設計周期后期更改內核的延遲或數據路徑寬度,作為對布局和布線的響應,表明設計將難以滿足時序要求,或者利用更快、更快速的 FPGA /或具有不同數量的資源。如果驗證工程師沒有預料到這種變化(例如,測試場景假定一個固定的延遲),那么可能需要更改大量測試來編寫新的預期。一個設計良好的驗證環境將需要很少的更改來響應這一點。

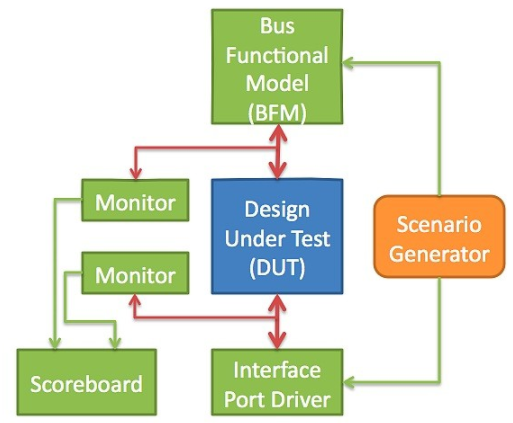

將測試臺環境與被測設備 (DUT) 實現細節分離的最佳方法之一是使用記分板,如圖 2 所示。測試場景將預期結果(例如,數據包)推送到記分板中,當 DUT 生成數據時,測試臺會自動將其與記分板版本進行比較。當 DUT 產生數據時,不需要關心測試場景,只需要關心它產生了什么數據。

圖 2:使用記分板是將測試臺環境與被測設備分離的最佳方法之一。

此外,如果數據路徑的寬度發生變化,并且 DUT 產生的數據被劃分為幾個額外的周期(或統一為更少的周期),那么記分板會在測試臺中提供一個點,其中與該預期的比較可以是改變了。在測試場景中對期望進行硬編碼的替代方法要求在 DUT 的數據寬度或數據格式發生變化時更新每個場景。

需要對端口驅動程序和監視器進行編碼以預測接口變化。當需要快速適應時,允許這些模塊連接到不同數據寬度的端口和接口的前期工作可以在設計和驗證周期的后期獲得回報。

FPGA IP,已驗證

在過去幾年中,可用于 FPGA 的 IP 數量大幅增加。為了具有競爭力,供應商必須始終如一地滿足對質量的期望。由于 FPGA IP 的上市時間需求變得越來越迫切,供應商必須盡一切可能防止交付的內核出現可能拖慢客戶速度的問題。這意味著必須采用經過深思熟慮的、能夠快速適應的驗證策略。

作者:Jason Lawley,Jeremy Goolsby

審核編輯:郭婷

-

FPGA

+關注

關注

1643文章

21983瀏覽量

614632 -

芯片

+關注

關注

459文章

52253瀏覽量

437010 -

Xilinx

+關注

關注

73文章

2183瀏覽量

124472

發布評論請先 登錄

新思科技賦能集成電路專業高質量發展

高質量 HarmonyOS 權限管控流程

廣汽集團召開高質量發展大會

使用IP核和開源庫減少FPGA設計周期

誠邁科技新質生產力高質量發展研討會活動預告

芯導科技榮獲上市公司高質量發展大會“科技創新獎”

華為臨沂攜手共筑新質生產力高質量發展

立洋光電助力城市照明高質量發展

中興通訊引領5G-A高質量發展新紀元

揭秘高質量點焊機的五大標準:打造焊接性能的基石

粵港聯動,北斗高質量國際化發展的重要機遇

生產和驗證高質量的FPGA IP

生產和驗證高質量的FPGA IP

評論