隨著仿真方法在各種不同大小的 SoC/ASIC 項(xiàng)目中變得越來(lái)越流行和負(fù)擔(dān)得起,出現(xiàn)了一個(gè)問(wèn)題,即為什么應(yīng)該在高速原型設(shè)計(jì)仍然是執(zhí)行的主要硬件驗(yàn)證技術(shù)的領(lǐng)域中使用仿真。首先要考慮的是速度。

熟悉該主題的人都知道,FPGA 原型設(shè)計(jì)可以提供最快的設(shè)計(jì)驗(yàn)證。當(dāng)然,由于較長(zhǎng)的設(shè)計(jì)設(shè)置時(shí)間和較大的工程工作量,存在成本問(wèn)題。隨著設(shè)置工具的改進(jìn)和變得更易于使用,這種情況正在發(fā)生變化。但是,達(dá)到最高速度仍然需要更多時(shí)間。一些公司甚至根據(jù)設(shè)計(jì)規(guī)范在內(nèi)部設(shè)計(jì)他們的 FPGA 板,以實(shí)現(xiàn)最高的原型制作速度。這使得該過(guò)程變得更長(zhǎng),但是,結(jié)合軟件分區(qū)工具,它肯定會(huì)提供最佳的速度結(jié)果。

事務(wù)級(jí)接口

另一個(gè)問(wèn)題是驗(yàn)證過(guò)程的接口級(jí)別。要切換到仿真,您必須從位級(jí)接口轉(zhuǎn)到事務(wù)級(jí)接口。這涉及開(kāi)發(fā)事務(wù)級(jí)測(cè)試平臺(tái)和事務(wù)到稱(chēng)為事務(wù)器的位級(jí)橋接器,需要新的工程技能(以及學(xué)習(xí)它們的時(shí)間)。

幸運(yùn)的是,仿真供應(yīng)商為最流行的接口提供了一個(gè)現(xiàn)成的事務(wù)處理程序庫(kù),并在需要時(shí)開(kāi)發(fā)自定義事務(wù)處理程序。測(cè)試臺(tái)問(wèn)題自然解決了。由于 UVM 方法已在許多 SoC 項(xiàng)目中使用,因此向仿真的轉(zhuǎn)變是無(wú)縫的。UVM 測(cè)試平臺(tái)本質(zhì)上也是基于事務(wù)的。如果有可用的交易器將其與硬件仿真的設(shè)計(jì)連接起來(lái),那么遷移到仿真幾乎是無(wú)痛的。也許更重要的是,設(shè)計(jì)本身可以以相同的方式進(jìn)行測(cè)試,使用與仿真相同的一組測(cè)試。

除了明顯的好處之外,雖然使用仿真顯著減少了驗(yàn)證過(guò)程的時(shí)間,但仿真和仿真中的測(cè)試也很容易追蹤。這有助于硬件驗(yàn)證團(tuán)隊(duì)與設(shè)計(jì)團(tuán)隊(duì)合作,到目前為止,這一過(guò)程在原型設(shè)計(jì)中被證明是困難的。

失去控制

設(shè)計(jì)設(shè)置的可控性是另一個(gè)有爭(zhēng)議的主題。原型設(shè)置要求用戶控制分區(qū)和時(shí)間約束過(guò)程,這兩者都是時(shí)間密集型的,但用戶保留對(duì)過(guò)程的控制。相反,仿真提供了自動(dòng)化所有或大部分過(guò)程的設(shè)置工具,使原型用戶失去控制和感覺(jué)。

解決方案在于為用戶提供調(diào)整設(shè)置過(guò)程的能力,即使是在仿真模式下,至少在影響測(cè)試執(zhí)行速度的領(lǐng)域。對(duì)設(shè)計(jì)的了解可能會(huì)在仿真速度方面產(chǎn)生出色的結(jié)果。當(dāng)然,這是工程師習(xí)慣的東西和仿真設(shè)置過(guò)程中可能控制的東西之間的折衷。

JTAG 調(diào)試

SoC 設(shè)計(jì)由處理器驅(qū)動(dòng),這些處理器通過(guò)基于 JTAG 的調(diào)試器進(jìn)行調(diào)試和控制,使 JTAG 接口成為原型設(shè)計(jì)的主要驗(yàn)證中心。JTAG 電纜將原型開(kāi)發(fā)板與主機(jī) PC 和處理器調(diào)試器連接起來(lái)。這需要物理布線連接,在需要時(shí)速度較慢且難以復(fù)制,但可以手動(dòng)控制接口。

這種傳統(tǒng)方法也可用于仿真,但可以進(jìn)一步擴(kuò)展。一旦虛擬 JTAG 事務(wù)器可用,電路板和主機(jī) PC 調(diào)試器之間就不需要電纜。通過(guò)這種處理器類(lèi)型,可以擁有多個(gè)調(diào)試接口,所有這些都基于仿真基礎(chǔ)設(shè)施,比 JTAG 接口快很多。這種解決方案比傳統(tǒng)的 JTAG 接口調(diào)試靈活得多。

何時(shí)選擇仿真

只有當(dāng) SoC 開(kāi)發(fā)完成并準(zhǔn)備好 RTL 代碼后,才能實(shí)現(xiàn)原型驗(yàn)證。這意味著 SoC 的硬件部分必須是完整的。不幸的是,這已經(jīng)很晚了,特別是對(duì)于等待開(kāi)發(fā)平臺(tái)的軟件團(tuán)隊(duì)或已經(jīng)在模擬中驗(yàn)證了項(xiàng)目并需要通過(guò)基于硬件的測(cè)試快速反饋的設(shè)計(jì)團(tuán)隊(duì)。顯然,在可用和需要時(shí)之間存在差距。

通過(guò)仿真,軟件開(kāi)發(fā)人員和硬件設(shè)計(jì)人員無(wú)需等待完成的設(shè)計(jì)。可以使用不同類(lèi)型的測(cè)試平臺(tái)驗(yàn)證和測(cè)試單獨(dú)的模塊和子系統(tǒng),例如 SystemC 測(cè)試平臺(tái)、虛擬平臺(tái)或流行的 UVM 事務(wù)??級(jí)測(cè)試平臺(tái)。仿真不僅使開(kāi)發(fā)團(tuán)隊(duì)能夠在流程的早期開(kāi)始他們的工作,它還允許在 SoC 級(jí)驗(yàn)證開(kāi)始之前在塊級(jí)驗(yàn)證 SoC,從而使最后一個(gè)階段更容易和更短。通過(guò)更進(jìn)一步并將軟件團(tuán)隊(duì)經(jīng)常使用的虛擬平臺(tái)與硬件模擬器集成,可以在流程的早期開(kāi)始整個(gè) SoC 驗(yàn)證,同時(shí)逐步增加在模擬器中實(shí)現(xiàn)的子系統(tǒng)的數(shù)量。

驗(yàn)證的未來(lái)

對(duì)速度、接口和調(diào)試要求的需求正在慢慢地將原型設(shè)計(jì)和仿真方法合二為一。在速度方面,沒(méi)有必要以最高速度運(yùn)行整個(gè) SoC;某些部分需要在最快的時(shí)鐘域中,而其他部分(例如需要大量調(diào)試的部分)可能會(huì)運(yùn)行得更慢。這種快速域是處理器內(nèi)置子系統(tǒng)和/或高速外部接口,例如以太網(wǎng)或 USB。這些使空間能夠?qū)⒃驮O(shè)計(jì)和仿真的兩個(gè)世界連接成一個(gè),并具有各自的優(yōu)勢(shì)。

隨著原型設(shè)計(jì)和仿真方法開(kāi)始相互滲透,它們之間的界限(以及一種方法優(yōu)于另一種方法的論點(diǎn))開(kāi)始消失。現(xiàn)代 SoC 項(xiàng)目的理想驗(yàn)證解決方案實(shí)際上是一種混合硬件-軟件驗(yàn)證環(huán)境,可在需要時(shí)提供最高速度、軟件接口靈活性以及在需要時(shí)提供調(diào)試功能。

審核編輯:郭婷

-

以太網(wǎng)

+關(guān)注

關(guān)注

40文章

5605瀏覽量

175209 -

usb

+關(guān)注

關(guān)注

60文章

8153瀏覽量

271491 -

soc

+關(guān)注

關(guān)注

38文章

4360瀏覽量

222051

發(fā)布評(píng)論請(qǐng)先 登錄

兩種驅(qū)動(dòng)方式下永磁直線開(kāi)關(guān)磁鏈電機(jī)的研究

兩種感應(yīng)電機(jī)磁鏈觀測(cè)器的參數(shù)敏感性研究

詳解ADC電路的靜態(tài)仿真和動(dòng)態(tài)仿真

TLV5616和TLV5636兩種工作模式FAST和SLOW分別有什么特點(diǎn),優(yōu)勢(shì),選擇時(shí)應(yīng)該注意什么?

AMC1204有兩種封裝,SOIC-8和SOIC-16,功能一樣嗎?為什么要推出兩種封裝?

solidworks正版軟件:永久版權(quán)和訂閱許可 兩種購(gòu)買(mǎi)方式解析和選擇

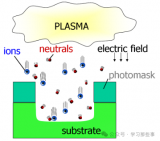

芯片制造過(guò)程中的兩種刻蝕方法

電源管理芯片U6117兩種封裝SOP-8、DIP-8,靈活滿足應(yīng)用需求

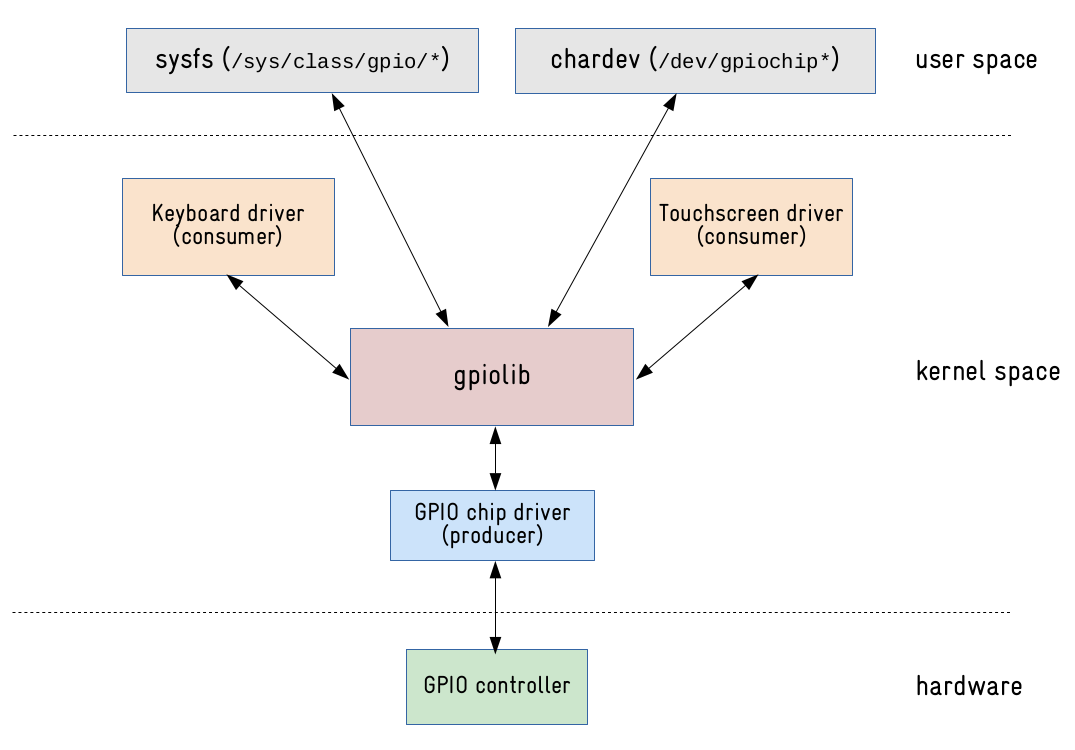

Linux應(yīng)用層控制外設(shè)的兩種不同的方式

借助技術(shù)同時(shí)擁有原型和仿真兩種選擇

借助技術(shù)同時(shí)擁有原型和仿真兩種選擇

評(píng)論