全局綜合(Global Synthesis)

全局綜合意味著整個(gè)設(shè)計(jì)在一個(gè)Synthesis Design Run流程中完成,這樣會(huì)帶來(lái)幾個(gè)好處。一是使得綜合工具能夠最大化地進(jìn)行設(shè)計(jì)優(yōu)化,尤其是層次間的優(yōu)化(這些優(yōu)化是其他綜合流程不能實(shí)現(xiàn)的)。二是對(duì)于綜合后的設(shè)計(jì)分析帶來(lái)了很大的便利。當(dāng)然,其不足之處也是很明顯的,那就是編譯時(shí)間會(huì)很長(zhǎng)。但這一不足之處可以借助增量綜合得以緩解。需要注意的是因?yàn)槭侨志C合,所以XDC中描述的約束是以頂層為基準(zhǔn)進(jìn)行索引的。

IPI綜合(Block Design Synthesis)

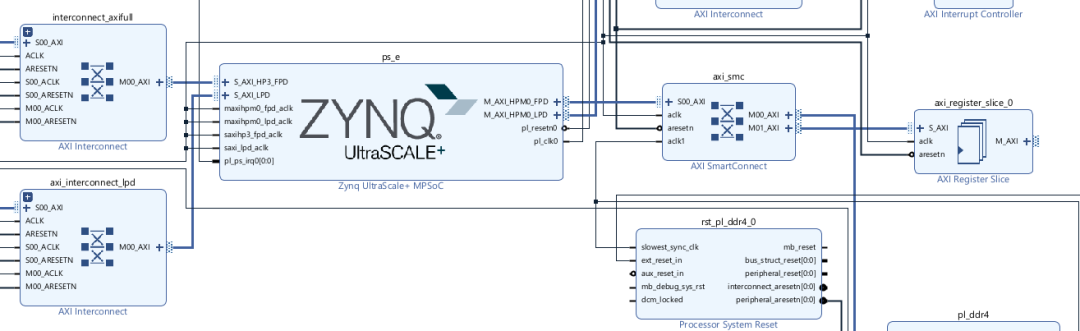

Vivado IPI (IP Integrator)提供了直觀的模塊化的設(shè)計(jì)方法。用戶可以將Vivado IP Catalog中的IP、用戶自己的RTL代碼、或者用戶已有的BD文件添加到IP Integrator中構(gòu)成Block Design,設(shè)計(jì)更復(fù)雜的系統(tǒng),如下圖所示。

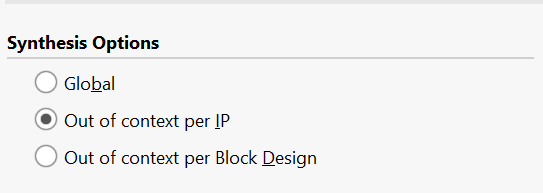

IPI使得用戶可以方便地將特定功能打包放入設(shè)計(jì)中,這樣用戶可以將焦點(diǎn)放在整個(gè)系統(tǒng)上,而非系統(tǒng)的某個(gè)部分。對(duì)于Block Design,Vivado提供了如下圖所示的三種綜合方式。其中Global為全局綜合方式,其余兩種均為OOC(Out-of-Context)綜合方式,只是OOC的粒度不同而已。OOC可以有效縮短編譯時(shí)間。

OOC綜合方式

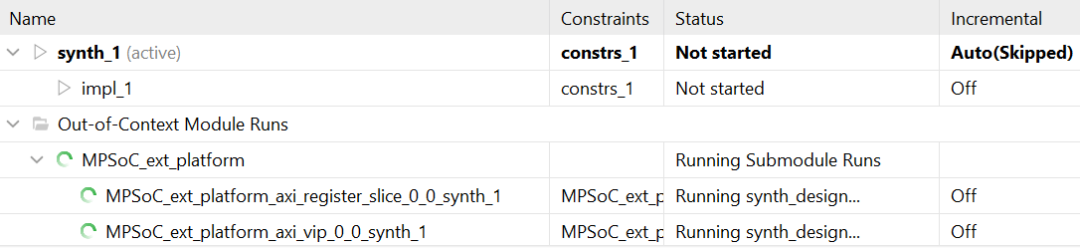

OOC綜合方式可以使用戶單獨(dú)對(duì)設(shè)計(jì)的某個(gè)層次進(jìn)行綜合,然后再對(duì)整個(gè)設(shè)計(jì)進(jìn)行綜合,此時(shí),OOC綜合的對(duì)象會(huì)被當(dāng)作黑盒子對(duì)待。通常,對(duì)于Xilinx的IP,我們建議采用OOC綜合方式。OOC可以縮短后續(xù)整個(gè)設(shè)計(jì)綜合所需時(shí)間,同時(shí),若設(shè)計(jì)發(fā)生改變,而OOC綜合對(duì)象沒有改變,那么整個(gè)設(shè)計(jì)的綜合就不需要再對(duì)OOC對(duì)象進(jìn)行綜合。一旦采用OOC綜合方式,在Design Runs窗口中就會(huì)看到相應(yīng)的OOC Module Runs,如下圖所示。

增量綜合(Incremental Synthesis)

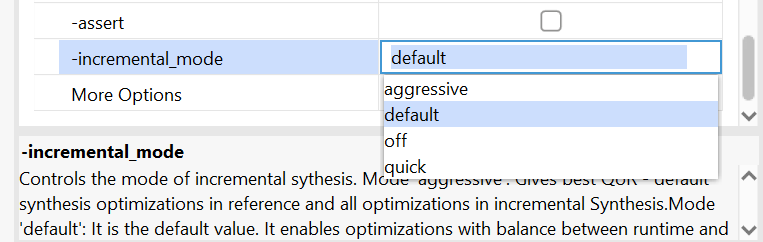

增量綜合可以使綜合工具復(fù)用之前已有的綜合結(jié)果,從而縮短編譯時(shí)間。但增量綜合是有前提條件的,即設(shè)計(jì)可以形成至少4個(gè)分割(Partitions),而每個(gè)分割至少包含25000個(gè)模塊。這里的“模塊”既包含設(shè)計(jì)層次也包含RTL原語(yǔ)。Vivado提供了四種增量綜合模式,如下圖所示。其中off表明關(guān)閉增量綜合,quick模式不會(huì)進(jìn)行邊界優(yōu)化。default模式會(huì)執(zhí)行大部分邏輯優(yōu)化包括邊界優(yōu)化,相對(duì)于非增量模式,能顯著縮短編譯時(shí)間。aggressive模式會(huì)執(zhí)行所有的邏輯優(yōu)化,編譯時(shí)間縮短程度最為明顯。對(duì)于低性能設(shè)計(jì)需求,可以使用quick模式,而對(duì)于高性能設(shè)計(jì)需求,建議采用其余三種模式。

模塊化綜合(Block-level Synthesis)

本身Vivado提供了多種綜合策略和各種綜合設(shè)置選項(xiàng),但其面向的對(duì)象是整個(gè)設(shè)計(jì),換言之,這是一種全局設(shè)置。Block-level綜合技術(shù)則打破了這一常規(guī),可以對(duì)不同層次的設(shè)計(jì)設(shè)置不同的選項(xiàng)或應(yīng)用不同的綜合策略,從而達(dá)到更好的綜合質(zhì)量。

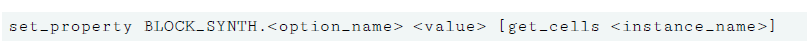

Block-level綜合技術(shù)需要通過(guò)XDC約束來(lái)實(shí)現(xiàn),如下圖所示。

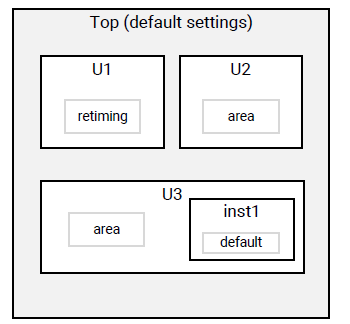

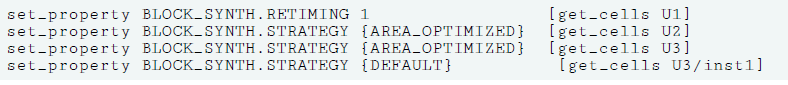

我們來(lái)看一個(gè)例子:設(shè)計(jì)中有4個(gè)模塊U1、U2、U3和inst1,而inst1又嵌入在U3里。現(xiàn)在我們需要對(duì)U1使能RETIMING,對(duì)U2和U3使用AREA_OPTIMIZED策略,對(duì)inst1使用DEFAULT綜合策略,那么我們就可以通過(guò)下圖所示約束實(shí)現(xiàn)。

審核編輯 :李倩

-

模塊化

+關(guān)注

關(guān)注

0文章

339瀏覽量

21872 -

Vivado

+關(guān)注

關(guān)注

19文章

834瀏覽量

68371

發(fā)布評(píng)論請(qǐng)先 登錄

如何使用One Spin檢查AMD Vivado Design Suite Synth的結(jié)果

適用于Versal的AMD Vivado 加快FPGA開發(fā)完成Versal自適應(yīng)SoC設(shè)計(jì)

CPU的各種指令和執(zhí)行流程

Vivado HLS設(shè)計(jì)流程

AMD Vivado Design Suite IDE中的設(shè)計(jì)分析簡(jiǎn)介

Vivado Design Suite用戶指南:邏輯仿真

使用HLS流程設(shè)計(jì)和驗(yàn)證圖像信號(hào)處理設(shè)備

Vivado之實(shí)現(xiàn)布局布線流程介紹

Xilinx_Vivado_SDK的安裝教程

U50的AMD Vivado Design Tool flow設(shè)置

每次Vivado編譯的結(jié)果都一樣嗎

Vivado使用小技巧

Vivado編輯器亂碼問(wèn)題

Vivado Synthesis的各種流程

Vivado Synthesis的各種流程

評(píng)論