本來沒有在那個地方設計電容,但由于布線之間總是有互容,互容就好像是寄生在布線之間的一樣,所以叫寄生電容

寄生電容:

本質上還是電容,滿足i=c*du/dt。

電容是用來衡量儲存電荷能力的物理量。根據Q=CU,在相同電壓下,電容越大,所能儲存的電荷就越多。

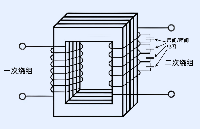

簡單來講,任何兩個面之間都有寄生電容。但同樣,這兩個面的大小,位置關系,兩個面中間的介質材料等因素都會影響寄生電容的大小。舉個例子,變壓器的每匝導線間,都會有寄生電容,在有些情況下,這個電容的充放電會影響變壓器的特性,需要特殊設計與考慮。

寄生電感:

本質是電感,具備電感特征,滿足u=L*di/dt。

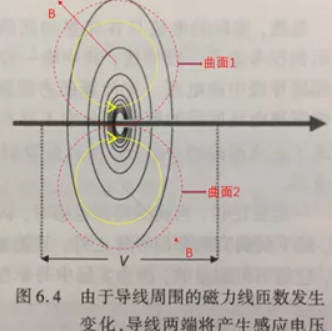

穿過線圈的磁通量發生變化時,線圈中會產生感應電勢。因此用電感來衡量線圈產生電磁感應能力的強弱,電感越大,在磁通量變化時,產生的感應電壓就越強。

寄生電感是指這個電感不是設計時故意設計出來的,是附加在某些東西上產生的。簡單來講,有導線的地方就有寄生電感。但不同特性的導線所攜帶的寄生電感是不同的。比如直導線肯定比線圈型導線的寄生電感要小。舉個例子,在電源系統PCB布線中,每一條布線都會攜帶一定的寄生電感,一般盡量減小關鍵換流回路的寄生電感,這是因為,當換流回路發生電流變化時,寄生電感上產生的感應電壓容易損壞元器件。

審核編輯 黃昊宇

-

電路設計

+關注

關注

6701文章

2529瀏覽量

213317 -

寄生電容

+關注

關注

1文章

297瀏覽量

19675 -

寄生電感

+關注

關注

1文章

160瀏覽量

14845

發布評論請先 登錄

逆變器寄生電容對永磁同步電機無傳感器控制的影響

【干貨分享】電源功率器件篇:變壓器寄生電容對高壓充電機輸出功率影響

CAN通信節點多時,如何減少寄生電容和保障節點數量?

半大馬士革工藝:利用空氣隙減少寄生電容

合金電阻的寄生電感及其影響

深入解析晶振時鐘信號干擾源:寄生電容、雜散電容與分布電容

仿真的時候在哪些地方添加寄生電容呢?

在LF411CD的放大模塊出現輸出會發生振蕩,請問該元件輸入端(2端)與GND間的寄生電容多大?

普通探頭和差分探頭寄生電容對測試波形的影響

系統寄生參數對SiC器件開關的影響分析

什么是寄生電容,什么是寄生電感

什么是寄生電容,什么是寄生電感

評論