電子系統中的噪聲有多種形式。無論是從外部來源接收到的,還是在PCB布局的不同區域之間傳遞,噪聲都可以通過兩種方法無意中接收:寄生電容和寄生電感。寄生電感相對容易理解和診斷,無論是從串擾的角度還是從板上不同部分之間看似隨機噪聲的耦合。

處理寄生電容并不一定更難,但確實需要理解PCB布局幾何形狀將如何影響互電容。在高頻操作的系統中,或者在高dV/dt節點可以創建電容耦合噪聲的地方,一些簡單的PCB布局選擇可以幫助減少寄生元件。在本文中,將一般性地描述如何減少寄生電容,并提供一些在高頻路由以及在開關轉換器中的例子。

識別并減少寄生電容

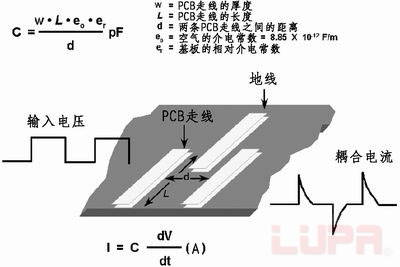

雖然沒有單一公式用于寄生電容,但它有一個一般定義:

- 寄生電容是兩個通過絕緣體分隔的導電結構之間存在的非故意電容(通常是不希望的)。

有時,這種非預期的電容實際上是有益的,在這種情況下,我們不使用“寄生”這個詞來描述它。以電源-地平面對為例;這種簡單結構有助于提供一個大的電荷儲備,以支持具有高輸入/輸出數量的高速組件,因為它具有固有的電容性。另一個例子是在共面波導中,基本上是利用寄生電容來將互連的阻抗設置為所需的值。

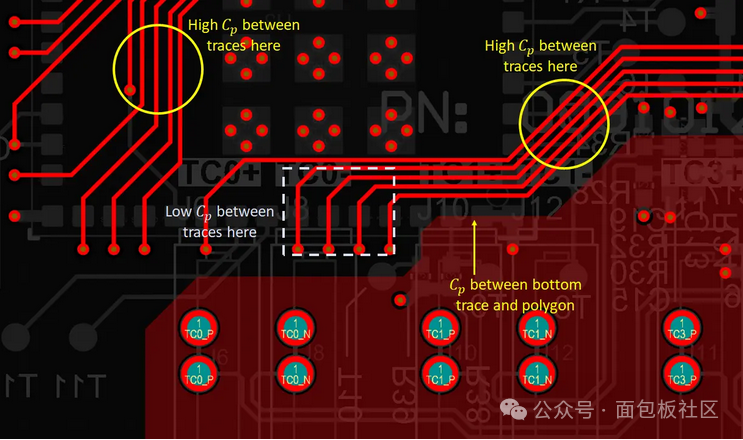

在PCB中,寄生電容幾乎可以出現在任何地方。看看下面的布局;我指出了一些寄生電容明顯的區域。這只顯示了頂層產生的電容,但任何層都可能有電容。

正如上面的定義所暗示的,寄生電容出現在任何由介電體分隔的導體對之間,我們可以快速識別上述示例中出現寄生電容的多個區域。每當在PCB布局中有寄生電容時,它可以通過兩種方式出現:

- 作為自身電容,它表現為導體與不同導體(通常是GND)之間的高不希望的電容。

- 互相電容是指兩個導電結構之間的電容,它們各自參考第三個導電結構;這實際上是導致兩條走線之間產生電容耦合的電容形式。

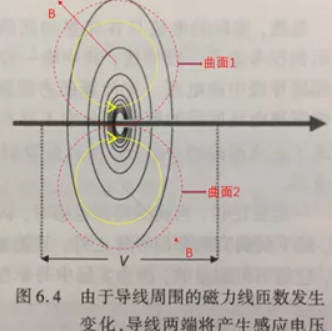

為什么高寄生電容很重要?這很重要,因為每當兩個電容耦合的導體之間存在變化的電位時,這會導致每個導體上流動一些位移電流。這是設計師應該熟悉的一種串擾形式。通常,當一個切換信號在受害走線上誘導其信號時,我們稱之為串擾,但同樣的機制在存在一些寄生電容時也可以在任何其他結構上誘導噪聲。

雖然永遠無法完全消除它,但在某些情況下,嘗試減少它是有益的。要了解如何減少寄生電容的一些策略,看一些例子會有所幫助。

示例:開關調節器中的高dV/dt節點

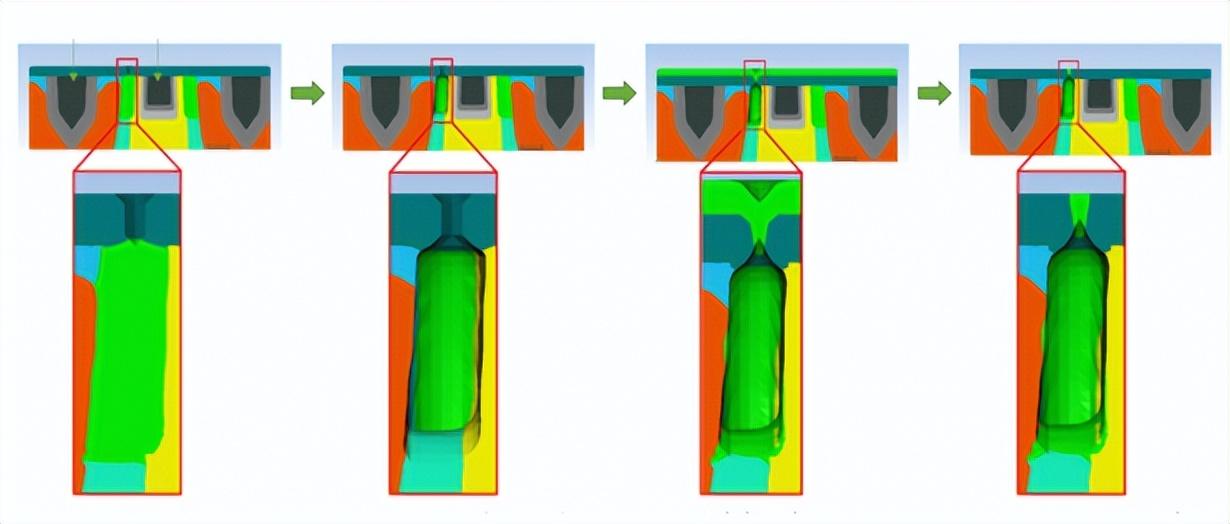

下面的調節器示例部分展示了一個強dV/dt節點的位置,以及為什么這種布局會有更大的耦合進入其反饋回路,而不是到系統的任何附近部分。在開關調節器中,dV/dt節點出現在開關階段的輸出上,但在整流/濾波階段之前。在下面的示例中,SW_OUT節點是我們的高dV/dt節點,由PWM信號驅動。

這個節點對附近的地面區域有一些寄生電容。如果附近有其他組件或電路,這些電路的寄生電容會導致開關噪聲出現在這些電路中。附近的地面有一些幫助,但真正防止噪聲耦合的是從SW_OUT回到調節器芯片的大電容器。這個大電容器為高dV/dt開關噪聲提供了一個低阻抗路徑回到開關階段的高側,有效地將開關階段的輸出與GND解耦。

dV/dt 節點可能會導致 PCB 布局中的噪聲耦合。一個有意放置的電容器可以防止這種情況

另一種減少SW_OUT與附近走線或電路之間寄生電容的策略是利用下一層的GND平面。將GND平面靠近高dV/dt節點,將通過創建更強的電場與GND的耦合,相比于PCB布局中的某些其他節點,減少相互電容。換句話說,會希望在這塊板子的L1和L2之間有一個更薄的介電層。

示例:兩條走線之間的相互電容

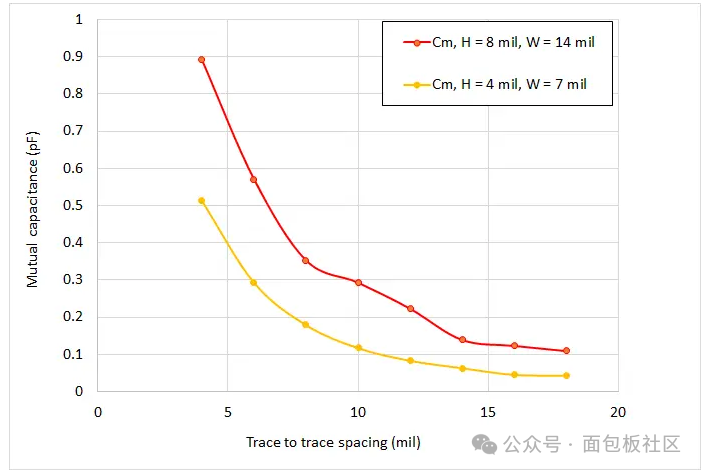

電容性串擾是走線之間兩種耦合類型之一(另一種是感應性),其中一條走線上的信號可以在另一條走線上產生噪聲。在逐漸增高的頻率下,這主要由相互電容主導。在PCB布局中,假設已經按照最佳實踐在GND區域上布線,基本上有兩種減少這種類型寄生電容的選擇:

- 在保持阻抗目標不變的情況下,使地線更靠近信號線,同時使信號線更窄

- 增加信號線之間的間距

幾乎能找到的所有關于減少串擾的建議都會推薦選項#2,但實際上選項#1同樣有效。這是因為它使地平面中的鏡像電荷/電流更靠近信號線。不應該嘗試像短接保護信號線這樣的操作,因為這會在地線上產生不希望的寄生電容,并且在某些配置中實際上會增加串擾。

仿真結果顯示,兩個50歐姆走線之間的寄生電容如何受與GND平面的距離(記作H)的影響。

總結

對于自電容形式的寄生電容,需要分開導體或使導體變小。對于互電容形式的寄生電容,需要通過增加自電容遠超過互電容來減少耦合。在上述例子中,我們看到,僅僅通過將地平面靠近我們的互電容信號線,就大大減少了它們的互電容,而無需對PCB布局中的其他導體進行任何改變。

-

pcb

+關注

關注

4362文章

23456瀏覽量

408129 -

寄生電容

+關注

關注

1文章

298瀏覽量

19712 -

調節器

+關注

關注

5文章

877瀏覽量

47542 -

開關轉換器

+關注

關注

0文章

50瀏覽量

13799

原文標題:如何在PCB布局中減少寄生電容

文章出處:【微信號:FANYPCB,微信公眾號:凡億PCB】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

PCB寄生電容的影響 PCB寄生電容計算 PCB寄生電容怎么消除

CAN通信節點多時,如何減少寄生電容和保障節點數量?

一種減少VDMOS寄生電容的新結構

什么是寄生電感_PCB寄生電容和電感計算

什么是寄生電容_寄生電容的危害

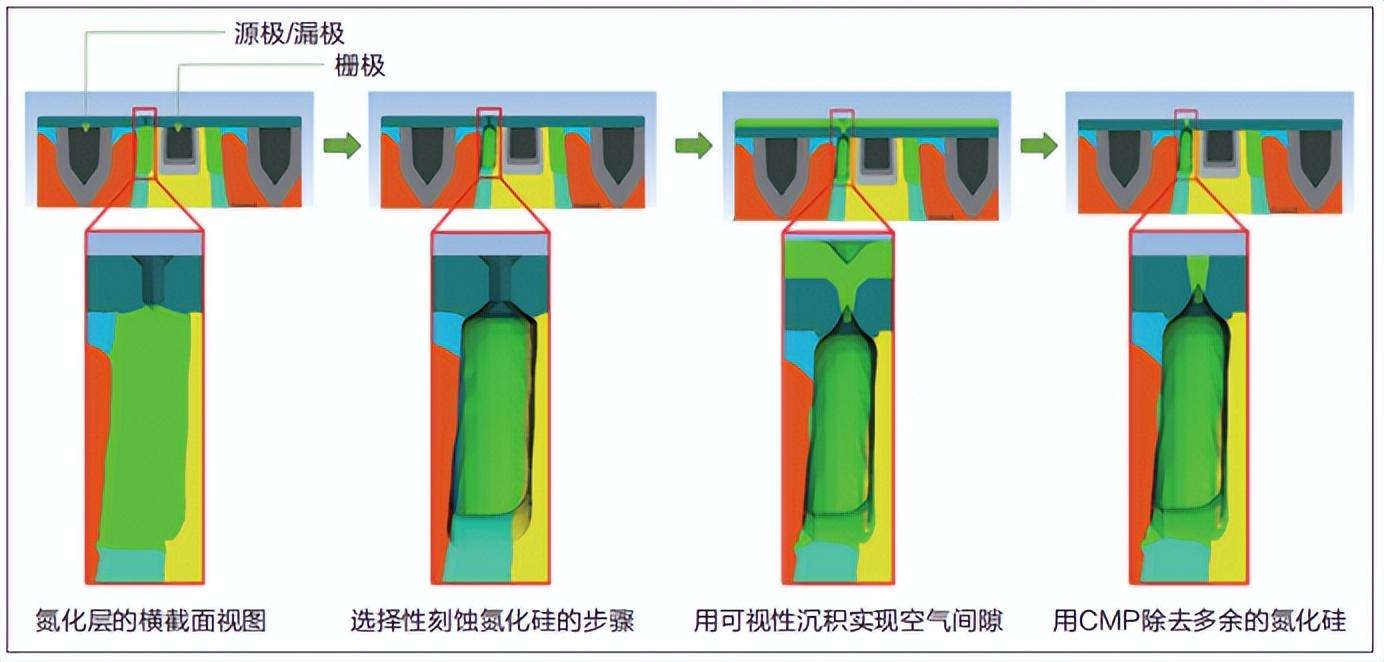

引入空氣間隙以減少前道工序中的寄生電容

PCB寄生電容的影響、計算公式和消除措施

減少PCB寄生電容的方法

減少PCB寄生電容的方法

評論