在典型的最后一英里廣播分發(fā)系統(tǒng)中,有線電視運(yùn)營商通過衛(wèi)星接收來自內(nèi)容提供商的廣播節(jié)目,使用集成接收器/解碼器 (IRD) 對其進(jìn)行解碼,然后重新編碼基帶視頻(在編碼器盒中)所需的分辨率、比特率和壓縮標(biāo)準(zhǔn)。接下來,他們將多個(gè)節(jié)目流結(jié)合起來,最終分發(fā)給最終消費(fèi)者。

一些國家要求有線電視運(yùn)營商在傳輸給最終消費(fèi)者的視頻中插入他們的標(biāo)志。本文討論了在基帶視頻中插入靜態(tài)徽標(biāo)的各種機(jī)制及其優(yōu)缺點(diǎn)。此外,本文還描述了我們認(rèn)為為實(shí)現(xiàn)低成本解決方案而采用的獨(dú)特設(shè)計(jì)方法。

視頻編碼器

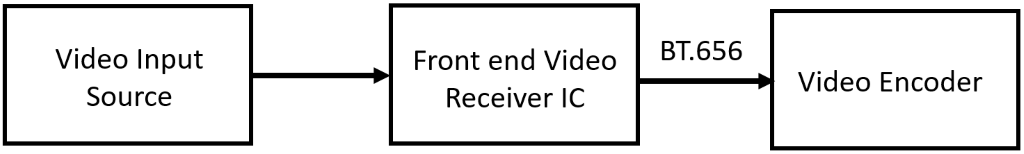

視頻編碼器通過各種模擬/數(shù)字接口接收視頻內(nèi)容,如復(fù)合 (S-Video)、分量 (YPbPr)、HDMI、DVI 和 3G-SDI,通常與視頻前端 IC 連接,如圖所示在圖 1 中。

圖 1:編碼器系統(tǒng)中的視頻接口

視頻前端包括一個(gè)視頻接收器 IC——它可以是一個(gè) ASIC 或一個(gè)編程為用作視頻接收器的 FPGA——它將前端視頻信號解碼為基帶視頻。該 ASIC/FPGA 的輸出通常是 BT.656 標(biāo)準(zhǔn)格式的并行端口數(shù)字視頻總線,連接到視頻編碼器進(jìn)行壓縮和持續(xù)傳輸。

標(biāo)識插入的設(shè)計(jì)方法

標(biāo)識圖像需要在編碼操作開始之前插入到基帶視頻幀中。將靜態(tài)徽標(biāo)插入視頻流有多種設(shè)計(jì)可能性,如下所示:

在視頻輸入源之后和前端接收器 IC 之前使用標(biāo)準(zhǔn)徽標(biāo)插入器。

選擇一個(gè)前端視頻接收器解決方案,它可以執(zhí)行將視頻解碼為 BT.656 以及插入徽標(biāo)的雙重功能。

使用在基于 Arm/GPU 的處理器上運(yùn)行的基于軟件的視頻編碼器系統(tǒng)在原始捕獲的視頻中執(zhí)行徽標(biāo)插入。

上述每種方法幾乎沒有缺點(diǎn)和限制。選項(xiàng) 1 需要為徽標(biāo)圖像編程和配置采購和維護(hù)外部硬件。

選項(xiàng) 2 涉及使用領(lǐng)先制造商提供的支持屏幕顯示 (OSD) 的視頻前端收發(fā)器 ASIC。這些都有其自身的限制,包括徽標(biāo)大小、混合能力、IC 成本以及每個(gè)視頻輸入接口對外部存儲器(如 DDR2)的要求。此外,在收發(fā)器之后,需要將數(shù)據(jù)呈現(xiàn)給視頻接收器,以將數(shù)據(jù)解碼為數(shù)字 BT.656 格式,以便與標(biāo)準(zhǔn)編碼器設(shè)備連接。

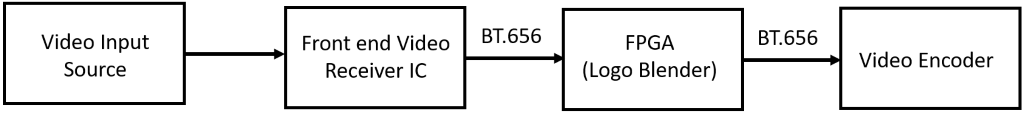

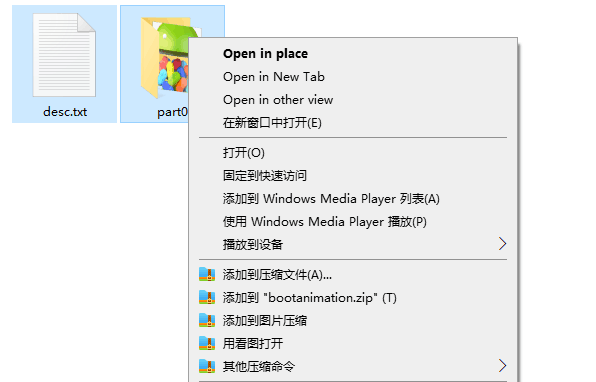

選項(xiàng) 3 是更好的解決方案,前提是視頻編碼器是基于軟件的,它提供了將徽標(biāo)圖像混合到作為幀緩沖區(qū)存儲在 DDR 中的原始視頻像素中的可配置性。但是,如果視頻編碼器是一個(gè)沒有提供標(biāo)識插入的 ASIC,那么這個(gè)選項(xiàng)會自動被排除,我們必須依賴選項(xiàng) 1 或 2。在這種情況下,要實(shí)現(xiàn)一個(gè)低成本的多- 輸入視頻編碼器的通道系統(tǒng),在 Ittiam,我們決定使用一種創(chuàng)新方法,包括低成本 FPGA,在視頻前端 IC 之后和基于 ASIC 的視頻編碼器之前混合徽標(biāo)圖像,如圖 2 所示。

圖 2:編碼前在數(shù)字視頻路徑中插入徽標(biāo)

此選項(xiàng)提供了一種低成本的多通道解決方案,因?yàn)閱蝹€(gè) FPGA 能夠?qū)Χ鄠€(gè)視頻通道執(zhí)行徽標(biāo)混合操作(上圖中僅顯示一個(gè)通道以進(jìn)行說明)。用于存儲徽標(biāo)圖像的 SPI 閃存連接到 FPGA。FPGA 可以在配置的適當(dāng)位置讀取這些徽標(biāo)圖像并將其與輸入基帶視頻流混合。

選擇的 FPGA 可以是低成本的,因?yàn)樵撛O(shè)計(jì)使用 FPGA 的內(nèi)部 RAM、邏輯元件和常見的 DSP 乘法器硬件塊來執(zhí)行混合操作所需的像素乘法操作。

FPGA RTL IP 旨在將 SPI 閃存配置為 QSPI 模式,以滿足 FIFO 讀寫接口的數(shù)據(jù)速率要求。QSPI 接口足夠快,可以在 BT.656 像素時(shí)鐘讀取單行徽標(biāo)數(shù)據(jù)之前將一行徽標(biāo)寫入或緩沖到 FPGA 的 FIFO 塊中以進(jìn)行混合操作(這決定了 QPSI 操作頻率在 FPGA 設(shè)計(jì)中)。透明度因子(α,或alpha)可由用戶在FPGA中配置,并且該因子可以被FPGA中實(shí)現(xiàn)的alpha混合算法用于執(zhí)行標(biāo)識插入操作。

結(jié)論在Ittiam Systems

開發(fā)的硬件設(shè)計(jì)中,上述方法已成功設(shè)計(jì)并實(shí)現(xiàn)了在基帶視頻中插入徽標(biāo)圖像。這種設(shè)計(jì)的優(yōu)點(diǎn)是它具有最小的延遲并降低了硬件解決方案的總體成本。

審核編輯:郭婷

-

解碼器

+關(guān)注

關(guān)注

9文章

1164瀏覽量

41771 -

編碼器

+關(guān)注

關(guān)注

45文章

3784瀏覽量

137454 -

接收器

+關(guān)注

關(guān)注

15文章

2563瀏覽量

73552

發(fā)布評論請先 登錄

飛凌嵌入式ElfBoard ELF 1板卡-uboot移植之logo的修改

全志T113-i開機(jī)Logo花屏問題排查與解決指南

迅為RK3562開發(fā)板旋轉(zhuǎn)Uboot logo和內(nèi)核logo

基于瑞芯微RK3562 四核 ARM Cortex-A53 + 單核 ARM Cortex-M0——系統(tǒng)啟動階段LOGO顯示

迅為RK3588開發(fā)板Buildroot系統(tǒng)設(shè)置屏幕旋轉(zhuǎn)旋轉(zhuǎn)Uboot logo和內(nèi)核 logo

插入式電磁流量計(jì)的應(yīng)用范圍要知道

光學(xué)元件的插入與移除,實(shí)現(xiàn)白光干涉中的機(jī)械相移原理

Linux系統(tǒng)更換開機(jī)logo方法教程,觸覺智能RK3562開發(fā)板演示

基帶視頻中Logo插入的設(shè)計(jì)方法

基帶視頻中Logo插入的設(shè)計(jì)方法

評論