電子發燒友網報道(文/吳子鵬)內核出貨量完成100億顆目標之后,RISC-V當前的聲勢更加空前,崛起的勢頭已經不可阻擋。與此同時,基于RISC-V內核實現的芯片,以及通過創新設計實現RISC-V+傳統芯片的案例越來越多,比如基于RISC-V實現高可靠性CPU,或者通過FPGA+RISC-V 實現一種創新設計。

我們都知道,安路科技發布的FPSoC新品便是上述舉例中的后者。5月27日,國內領先的FPGA芯片供應商安路科技在官方微信中表示,精心打造的SF1系列FPSoC器件現已全面推出,集成邏輯單元、存儲單元、視頻處理單元、RISC-V CPU硬核等資源,助力實現視頻圖像接口轉換和工業控制交互。

在這篇新品推文中,亮點除了安路科技成功推出FPSoC之外,RISC-V CPU的出現也極為引人關注。安路科技為什么要推出FPSoC?為什么會選擇RISC-V ?它起到了怎樣的作用?帶著這些問題,電子發燒友網記者采訪了安路科技SoC系統架構師楊益。

自賽靈思被AMD公司收購之后,全球FPGA市場兩大“頭牌”相繼歸入領先的CPU公司麾下。楊益表示,“這代表了異構計算是未來的發展趨勢,也是FPGA行業未來重要發展方向。同時,FPGA作為一種重要的異構計算單元,在很早之前,被收購的賽靈思公司就推出了像Zynq這樣的FPGA+CPU的架構,安路科技自然也會關注到這樣的發展趨勢。”

根據安路科技后續披露的投資者關系活動記錄,SF1系列FPSoC器件已經實現量產,并且正在研發一款高效率FPSoC器件。

FPSoC的英文全稱是Field Programmable System On Chip,中文釋義為現場可編程系統級芯片,其核心組成便是CPU+FPGA,具備兩種類型芯片的相應功能。而安路科技在SF1系列FPSoC器件上選擇的是RISC-V CPU和FPGA搭配。

“安路科技關注RISC-V有很長的時間了。首先,作為一種自主可控的處理器架構,RISC-V近年來得到了國內上下游廠商廣泛的關注和支持,其整個生態成熟度已經可以滿足很多領域的需求;其次,RISC-V開放特性非常適合FPGA 嵌入式CPU軟核應用,解決了之前FPGA公司主推封閉架構CPU軟核跨平臺移植困難的問題,幫助客戶保護其設計資產。” 楊益在解釋安路科技為什么選擇RISC-V 架構時講到。

在FPGA上搭配嵌入式處理器軟核,這一概念最早出現在Altera公司(已經被英特爾收購)提出來的SOPC技術中,其突出的優點是靈活性更高,對于CPU性能和外設功能,用戶可以按照自己的需求進行設定。楊益指出,“安路科技RISC-V 架構軟核推出后已經得到了很多客戶成功應用。新推出集成CPU硬核產品也選擇RISC-V 體系,可以和RISC-V軟核共享開發生態,讓客戶應用更加靈活方便。”

確實,對于SF1系列FPSoC器件,以及其他類型的SoC FPGA產品而言,是將CPU硬核和FPGA以異構集成的方式放置在一起,是純硬件實現的,不會消耗FPGA的邏輯資源,在系統性能方面能夠有更大的發揮空間。

對于RISC-V CPU+FPGA這種搭配如何取得1+1>2的效果,楊益在采訪過程中提到了三點:

RISC-V的指令集優勢

RISC-V是個精簡指令集處理器,功耗比較低,SF1的低功耗性能使得它在功耗敏感領域得到較多應用。

RISC-V CPU的豐富資源

RISC-V CPU硬核支持RV32IMAC指令集,支持指令數據Cache,同時也集成了SPI、UART、I2C等數據接口,內置大容量PSRAM可以很大擴展應用領域;支持FreeRTOS,RTthread,UCOSII等操作系統;SF1系列FPSoC在片上集成Flash和PSRAM模塊,同時提供RISC-V的Local Memory或Cache可配置方案,提供了的靈活的軟件運行方案。

FPGA對RISC-V的補充

FPGA的硬件可編程特性,可以作為可定制加速單元、高性能接口、實時處理模塊等多種應用模式,通過內部總線連接,作為RISC-V的補充形成完整單芯片方案。

除此之外,楊益強調,SF1系列還集成DSI(x2)和DSC硬核,提供了強大的圖像和視頻接口能力。在此基礎上,客戶可以利用FPGA邏輯資源進行個性化拓展,非常適同于人機交互、圖像視頻接口等領域。

當然,作為一種處于高速發展過程中的后發架構,開發者往往會擔憂RISC-V的軟件生態問題,映射到產品上就是產品的易用性問題。楊益對此回應稱。“我們看到在MCU/MPU領域,RISC-V的生態發展很快,國內已經有多家廠商對RISC-V 產品都提供了完善的開發生態,其中很多都開源或者基于開源項目。安路科技通過自研和第三方合作,推出了功能完善的基于RISC-V的SDK及IDE環境,我們同時提供了重點行業應用的參考方案。”

在完成核心出貨100億顆目標之后,RISC-V International首席執行官 Calista Redmond 表示,RISC-V CPU核心數有望在2025年達到800億顆。短短四年時間,從100億到800億,這是一種爆炸式的增長。無疑,安路科技也已經參與到這一發展洪流之中。“安路科技對RISC-V有長期的關注,并一直看好RISC-V在中國市場的發展前景。目前,安路科技已經成為RISC-V組織的戰略會員,在后續產品規劃會繼續發力RISC-V優勢市場并積極參與國內RISC-V生態的發展建設。” 楊益說到。

我們都知道,安路科技發布的FPSoC新品便是上述舉例中的后者。5月27日,國內領先的FPGA芯片供應商安路科技在官方微信中表示,精心打造的SF1系列FPSoC器件現已全面推出,集成邏輯單元、存儲單元、視頻處理單元、RISC-V CPU硬核等資源,助力實現視頻圖像接口轉換和工業控制交互。

在這篇新品推文中,亮點除了安路科技成功推出FPSoC之外,RISC-V CPU的出現也極為引人關注。安路科技為什么要推出FPSoC?為什么會選擇RISC-V ?它起到了怎樣的作用?帶著這些問題,電子發燒友網記者采訪了安路科技SoC系統架構師楊益。

自賽靈思被AMD公司收購之后,全球FPGA市場兩大“頭牌”相繼歸入領先的CPU公司麾下。楊益表示,“這代表了異構計算是未來的發展趨勢,也是FPGA行業未來重要發展方向。同時,FPGA作為一種重要的異構計算單元,在很早之前,被收購的賽靈思公司就推出了像Zynq這樣的FPGA+CPU的架構,安路科技自然也會關注到這樣的發展趨勢。”

根據安路科技后續披露的投資者關系活動記錄,SF1系列FPSoC器件已經實現量產,并且正在研發一款高效率FPSoC器件。

FPSoC的英文全稱是Field Programmable System On Chip,中文釋義為現場可編程系統級芯片,其核心組成便是CPU+FPGA,具備兩種類型芯片的相應功能。而安路科技在SF1系列FPSoC器件上選擇的是RISC-V CPU和FPGA搭配。

“安路科技關注RISC-V有很長的時間了。首先,作為一種自主可控的處理器架構,RISC-V近年來得到了國內上下游廠商廣泛的關注和支持,其整個生態成熟度已經可以滿足很多領域的需求;其次,RISC-V開放特性非常適合FPGA 嵌入式CPU軟核應用,解決了之前FPGA公司主推封閉架構CPU軟核跨平臺移植困難的問題,幫助客戶保護其設計資產。” 楊益在解釋安路科技為什么選擇RISC-V 架構時講到。

在FPGA上搭配嵌入式處理器軟核,這一概念最早出現在Altera公司(已經被英特爾收購)提出來的SOPC技術中,其突出的優點是靈活性更高,對于CPU性能和外設功能,用戶可以按照自己的需求進行設定。楊益指出,“安路科技RISC-V 架構軟核推出后已經得到了很多客戶成功應用。新推出集成CPU硬核產品也選擇RISC-V 體系,可以和RISC-V軟核共享開發生態,讓客戶應用更加靈活方便。”

確實,對于SF1系列FPSoC器件,以及其他類型的SoC FPGA產品而言,是將CPU硬核和FPGA以異構集成的方式放置在一起,是純硬件實現的,不會消耗FPGA的邏輯資源,在系統性能方面能夠有更大的發揮空間。

對于RISC-V CPU+FPGA這種搭配如何取得1+1>2的效果,楊益在采訪過程中提到了三點:

RISC-V的指令集優勢

RISC-V是個精簡指令集處理器,功耗比較低,SF1的低功耗性能使得它在功耗敏感領域得到較多應用。

RISC-V CPU的豐富資源

RISC-V CPU硬核支持RV32IMAC指令集,支持指令數據Cache,同時也集成了SPI、UART、I2C等數據接口,內置大容量PSRAM可以很大擴展應用領域;支持FreeRTOS,RTthread,UCOSII等操作系統;SF1系列FPSoC在片上集成Flash和PSRAM模塊,同時提供RISC-V的Local Memory或Cache可配置方案,提供了的靈活的軟件運行方案。

FPGA對RISC-V的補充

FPGA的硬件可編程特性,可以作為可定制加速單元、高性能接口、實時處理模塊等多種應用模式,通過內部總線連接,作為RISC-V的補充形成完整單芯片方案。

除此之外,楊益強調,SF1系列還集成DSI(x2)和DSC硬核,提供了強大的圖像和視頻接口能力。在此基礎上,客戶可以利用FPGA邏輯資源進行個性化拓展,非常適同于人機交互、圖像視頻接口等領域。

當然,作為一種處于高速發展過程中的后發架構,開發者往往會擔憂RISC-V的軟件生態問題,映射到產品上就是產品的易用性問題。楊益對此回應稱。“我們看到在MCU/MPU領域,RISC-V的生態發展很快,國內已經有多家廠商對RISC-V 產品都提供了完善的開發生態,其中很多都開源或者基于開源項目。安路科技通過自研和第三方合作,推出了功能完善的基于RISC-V的SDK及IDE環境,我們同時提供了重點行業應用的參考方案。”

在完成核心出貨100億顆目標之后,RISC-V International首席執行官 Calista Redmond 表示,RISC-V CPU核心數有望在2025年達到800億顆。短短四年時間,從100億到800億,這是一種爆炸式的增長。無疑,安路科技也已經參與到這一發展洪流之中。“安路科技對RISC-V有長期的關注,并一直看好RISC-V在中國市場的發展前景。目前,安路科技已經成為RISC-V組織的戰略會員,在后續產品規劃會繼續發力RISC-V優勢市場并積極參與國內RISC-V生態的發展建設。” 楊益說到。

聲明:本文內容及配圖由入駐作者撰寫或者入駐合作網站授權轉載。文章觀點僅代表作者本人,不代表電子發燒友網立場。文章及其配圖僅供工程師學習之用,如有內容侵權或者其他違規問題,請聯系本站處理。

舉報投訴

-

FPGA

+關注

關注

1646文章

22054瀏覽量

618820 -

RISC-V

+關注

關注

46文章

2584瀏覽量

48888

發布評論請先 登錄

相關推薦

熱點推薦

高度集成,基于RISC-V AI CPU芯片K1的PsP封裝CoM產品發布

DDR接口信號,重排布信號電源ball。通過進一步優化硬件解決方案,可以協助解決客戶設計DDR模板的困難,縮短客戶產品開發周期,助力RISC-V生態建設。B1產品

FPGA與RISC-V淺談

全球半導體產業競爭格局正在經歷深刻變革,物聯網、邊緣計算等新興技術的蓬勃發展,讓RISC-V憑借其開源、精簡以及模塊化的靈活優勢,日益成為業界焦點,也為全球半導體產業注入新的活力與挑戰

發表于 04-11 13:53

?362次閱讀

k32l2b31寫入LPUART1-&;gt;STAT |= (1&;lt;&lt;25)會導致semihost_hardfault是為什么?

我想在 k32l2b31 上激活 LIN Break 檢測

必須在狀態寄存器中設置位 LKDE

i try LPUART1-&;gt;STAT |= (1&;lt;&

發表于 04-08 06:36

OrangePi RV2發布: 8核RISC-V AI CPU,“OpenHarmony5.0?X DeepSeek&amp;quot;引領智能未來

繼剛剛發布OrangePiRV之后,香橙派又為大家帶來了一款RISC-V開發板OrangePiRV2。OrangePiRV2是香橙派在RISC-V布局的一個標志性產品,采用KyX18核

RISC-V架構及MRS開發環境回顧

一、RISC-V架構介紹

1. RISC 架構的起源

1981年,在David Patterson(大衛·帕特森)的帶領下,美國加州大學伯克利分校的一個研究團隊起 草了RISC-I,是

發表于 12-16 23:08

RISC-V 與 ARM 架構的區別 RISC-V與機器學習的關系

在現代計算機架構中,RISC-V和ARM是兩種流行的處理器架構。它們各自具有獨特的特點和優勢,適用于不同的應用場景。 1. RISC-V架構 RISC-V(讀作“risk-five”)

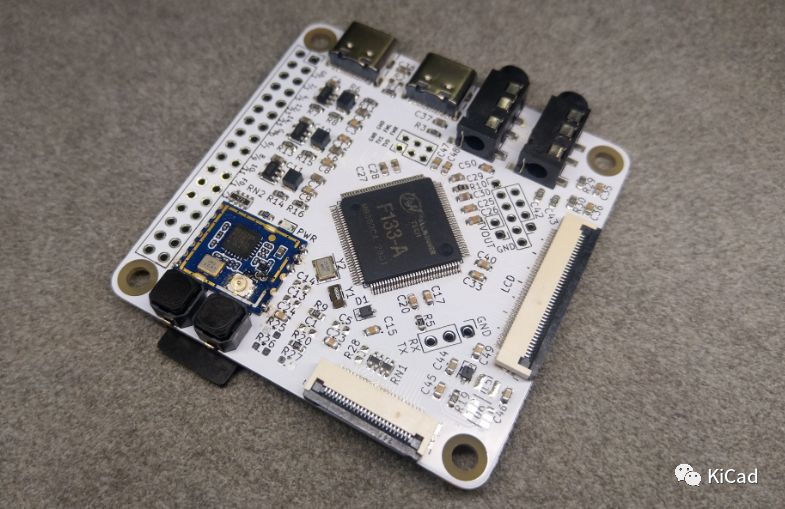

Made with KiCad(十六):全志RISC-V 64 SoC F133/D1s開發板

Linux 的開發板一起推出的全志D1 RISC-V 處理器的低成本版,它和D1的主要區別在于D1s內置的RAM是 64MB DDR2。

RISC-V發展及FPGA廠商為什么選擇RISC-V

Microsemi 于 2017 年開始在其 FPGA 中提供 RISC-V 軟核,Lattice 于 2020 年開始提供,英特爾 (Altera) 于 2021 年開始提供,因此 Xilinx

RISC-V基本整數指令

運算并將結果存儲在Rd中。

LOGICAL(邏輯運算):RISC-V還支持多種邏輯運算指令,如與(AND)、或(OR)、異或(XOR)等。這些指令可以對寄存器中的數據進行位運算,以實現各種邏輯功能

發表于 10-31 16:15

RISC-V之li指令講解

, immediate 會直接擴展成:

luia0,immediate &gt;&gt; 12

addia0, a0, (immediate &

發表于 10-28 14:55

精益生產的數字化轉型:1+1&;gt;2的效應

復雜多變的市場環境和消費者需求的快速迭代,單純依靠傳統精益生產已難以滿足企業高質量發展的需求。 數字化轉型,則是利用云計算、大數據、人工智能等先進技術,對企業進行全方位、深層次的改造升級。它不僅能夠實現生產過

物聯網+六西格瑪:1+1&;gt;2的協同效應

物聯網 物聯網,作為新一代信息技術的重要組成部分,通過智能感知、識別技術與普適計算等通信感知技術,將各種信息傳感設備與互聯網結合起來而形成的一個巨大網絡。它讓萬物互聯成為可能,從智能家居到智慧城市,從工業制造到農業灌溉,物聯網正以前所未有的速度滲透到我們生活的方方面面,極大地提升了社會的智能化水平。 六西格瑪 而六西格瑪,則是一套以數據為基礎,追求近乎零缺陷的質量管理方法論。它不僅僅關注產品質量的提升,

2024 RISC-V 中國峰會:華秋電子助力RISC-V生態!

技術未來發展方向的寶貴機會。

華秋電子&lt;電子發燒友&gt;作為RISC-V中國峰會的核心媒體社區合作伙伴,深度參與此次峰會。通過其廣泛的影響力,積極推廣前沿的

發表于 08-26 16:46

rIsc-v的缺的是什么?

通過軟件模擬或復雜的指令序列來實現一些高級功能,這可能會增加執行時間和功耗。

2. 生態系統支持不足

軟件和工具鏈的可用性:盡管RISC-V社區在快速發展,但與成熟的ARM等架構相比,其生

發表于 07-29 17:18

FPGA+RISC-V ,如何實現1+1>2?

FPGA+RISC-V ,如何實現1+1>2?

評論