ACE 要求 WU/WLU 傳輸事務不得繞過任何未完成的逐出類型傳輸事務 (WriteBack/WriteEvict/WriteClean)。

為滿足此要求,如果在逐出處于暫掛狀態時嘗試 WU/WLU 傳輸事務,則會導致微架構危害并強制回放。

在極為罕見的情況下,如果存在由 L2 高速緩存行填充和關聯逐出構成的持久性數據流,并且互連中存在顯著反壓,這兩者相結合并搭配特定時序,就可能導致 WBNA 存儲無限停滯。

條件

1. 通過將 L2ACTLR[4] 默認值更改為 1b0 來啟用 WriteUnique/WriteLineUnique 傳輸事務。

2. Cortex-A72 處理器發出寫回無分配存儲 (OP1) 指令。如果處理器將數據流傳輸存儲降級至寫回無分配,則同樣滿足此條件。

3. 存在暫掛的逐出事務,因 ACE 要求未完成的逐出事務必須完成后才能執行 WriteUnique/WriteLineUnique 存儲,從而導致 (OP1) 強制停滯。

4. 因其它核和/或預取導致發生持續性的 L2 高速緩存行填充數據流,從而觸發新的逐出。

5. 在互連中存在顯著持續性反壓,使系統保持處于擁塞,從而使 ACE 寫入通道隊列近滿。

6. 存在特定仲裁和時序條件,并且此類條件與條件 5 相結合導致觸發微架構危害,導致條件 3 不斷重復。

解決方案

影響:

如滿足以上條件,(OP1) 將停滯直至 L2 子系統中的特定時序條件和反壓放寬為止。寫回無分配存儲后的中斷和屏障也將延遲,直至存儲完成為止。

此錯誤的條件極為罕見,應該不會對實際系統性能產生顯著影響。

此外,如果使用 L2ACTLR[4] 的復位值,并禁用 WriteUnique/WriteLineUnique 傳輸事務,則可提升大部分系統的性能。

變通方法:

如無需 WriteUnique/WriteLineUnique 傳輸事務,則可通過設置 L2ACTLR[4] = 1'b1 來將其禁用。

這是復位值。否則,設置 L2ACTLR[7] = 1'b1 即可啟用 L2 危害檢測超時。這將強制 L2 高速緩存定期重新評估危害,屆時將釋放停滯。

受影響的配置:

具有 Arm Cortex-A72 (APU) 的所有 Versal 器件。

解決方案:

請參閱此第三方勘誤表 (Arm, Inc. 851022)。不對該問題進行修復。

-

處理器

+關注

關注

68文章

19388瀏覽量

230559 -

數據

+關注

關注

8文章

7113瀏覽量

89310 -

存儲

+關注

關注

13文章

4340瀏覽量

86010

發布評論請先 登錄

相關推薦

AN126-用于穩壓器的2線虛擬遙感-千里眼與遙感相結合

運放的壓擺率可能因芯片過熱變小嗎?

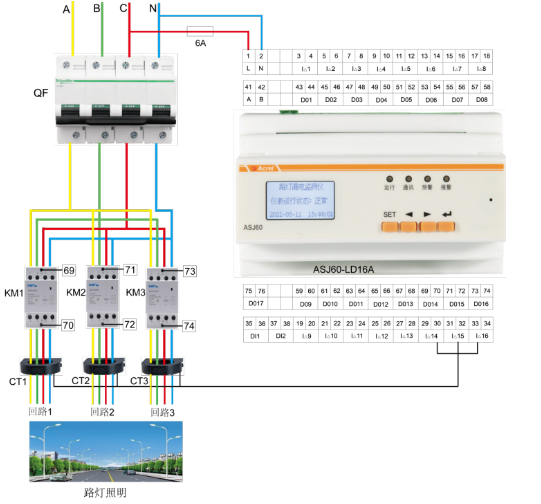

路燈漏電會導致哪些安全隱患

未接地可能導致的后果和維護注意事項

電路的失壓保護常由什么來實施

如何保障變電站母線零失壓措施

逆變器正負接反燒了怎么處理

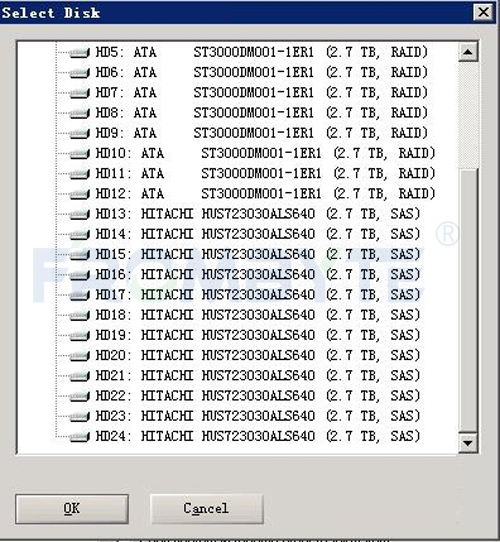

服務器數據恢復—異常斷電導致存儲癱瘓的數據恢復案例

持續逐出與互連反壓相結合可能導致寫回無分配存儲發生停滯

持續逐出與互連反壓相結合可能導致寫回無分配存儲發生停滯

評論