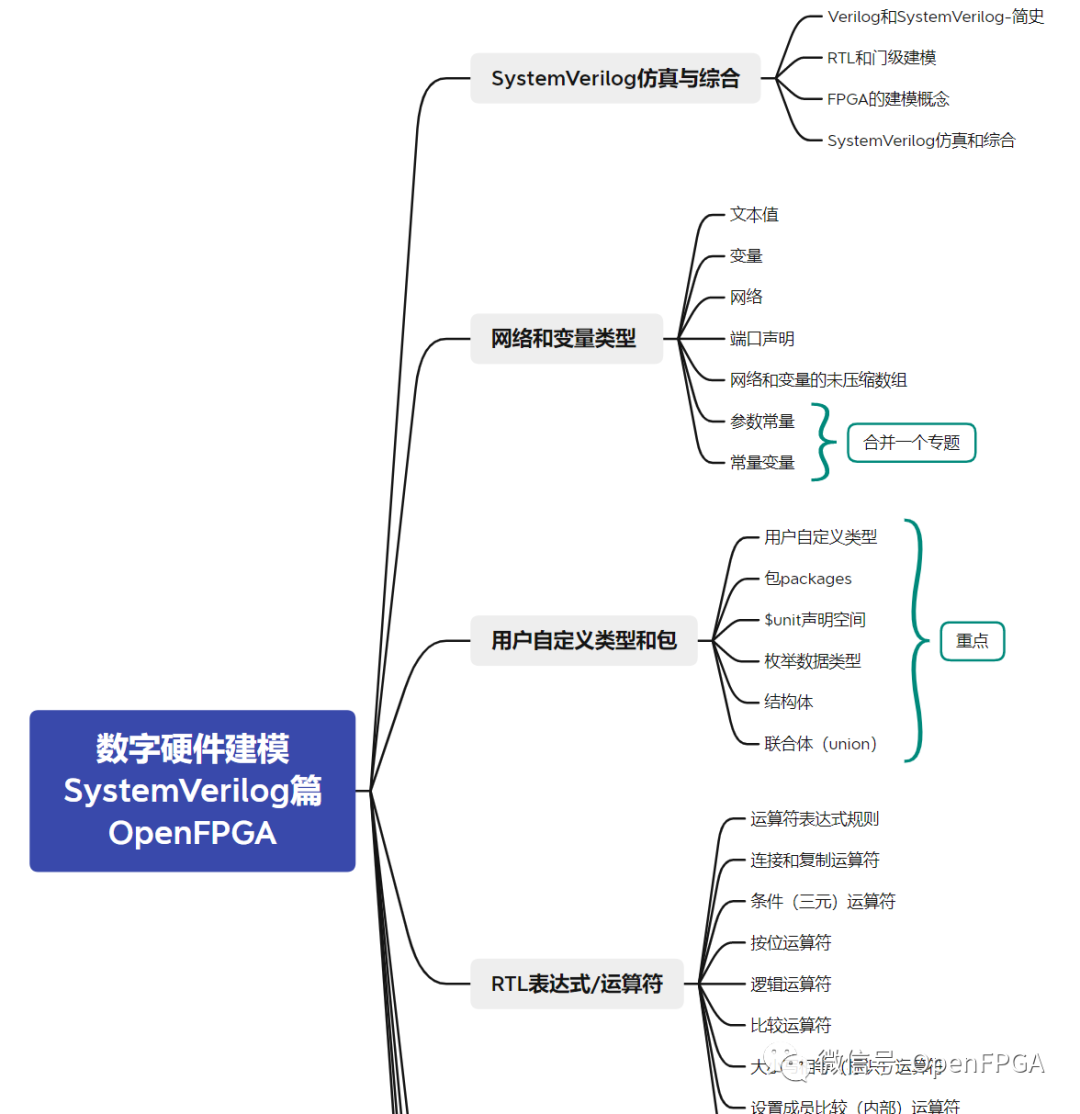

數字硬件建模SystemVerilog-按位運算符

經過幾周的更新,SV核心部分用戶自定義類型和包內容已更新完畢,接下來就是RTL表達式和運算符。

馬上HDLBits-SystemVerilog版本也開始準備了,基本這一部分完成后就開始更新~

介紹

(按)位運算符(Bitwise operators)

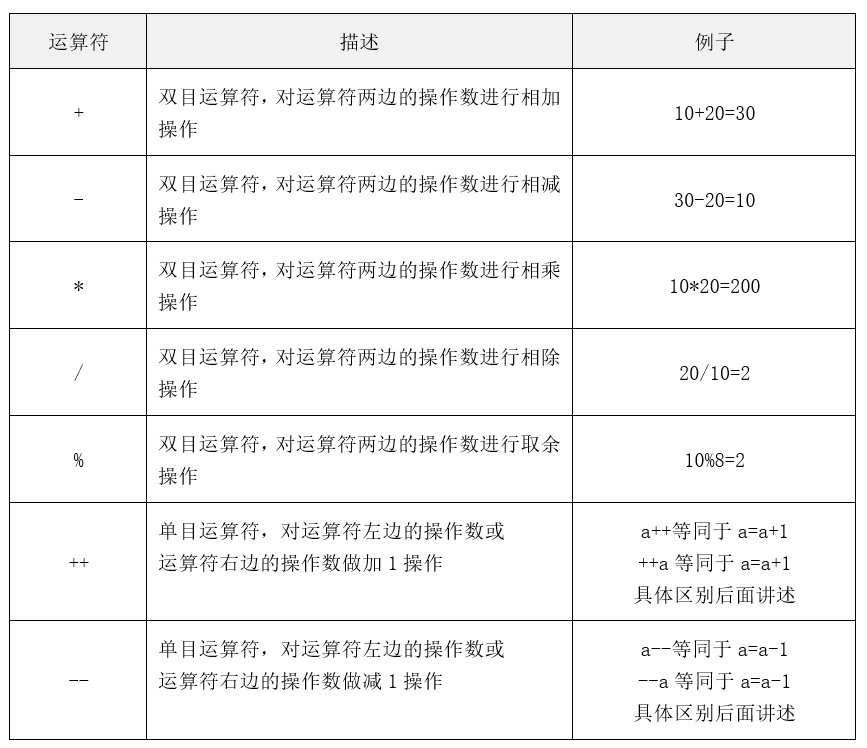

位運算符一次執行一位操作,從最右邊的位(最低有效位)向最左邊的位(最高有效位)移動。表5-3列出了按位運算符功能。

| 運算符 | 示例用法 | 描述 |

|---|---|---|

| ~ | ~m | 將m(1的補碼)的每一位反轉 |

| & | m&n | m和n的每一位相與(AND) |

| ^ | m ^ n | m與n的每一位相異或(XOR) |

| ^~或者~^ | m ^~n | m和n的每一位相同或 |

| I | mIn | m和n的每一位相或(OR) |

(I代表 | - 或操作)

沒有位NAND或NOR運算符。NAND或NOR操作是分別反轉AND或OR操作的結果,如~(m&n)。需要括號,以便先執行AND運算。

位運算要求兩個操作數的向量大小相同。在執行操作之前,較小的操作數將擴展以匹配較大操作數的大小。

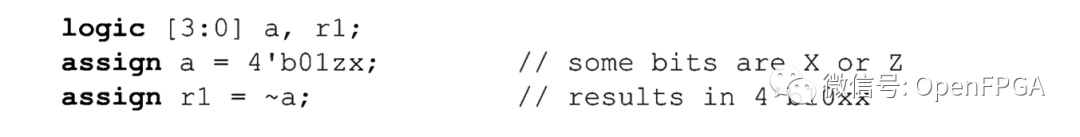

(按)位反轉

按位反轉(Bitwise inversion.)。位反轉運算符將其單個操作數的每一位反轉,從右向左操作,結果是操作數值的一個補數。位反轉運算符是X-pessimistic-反轉X或Z值的結果始終是X。表5-4顯示了位反轉的真值表。表中的結果針對操作數的每一位。

| ~ | 結果 |

|---|---|

| 0 | 1 |

| 1 | 0 |

| X | X |

| Z | X |

位反轉操作的一個示例結果是:

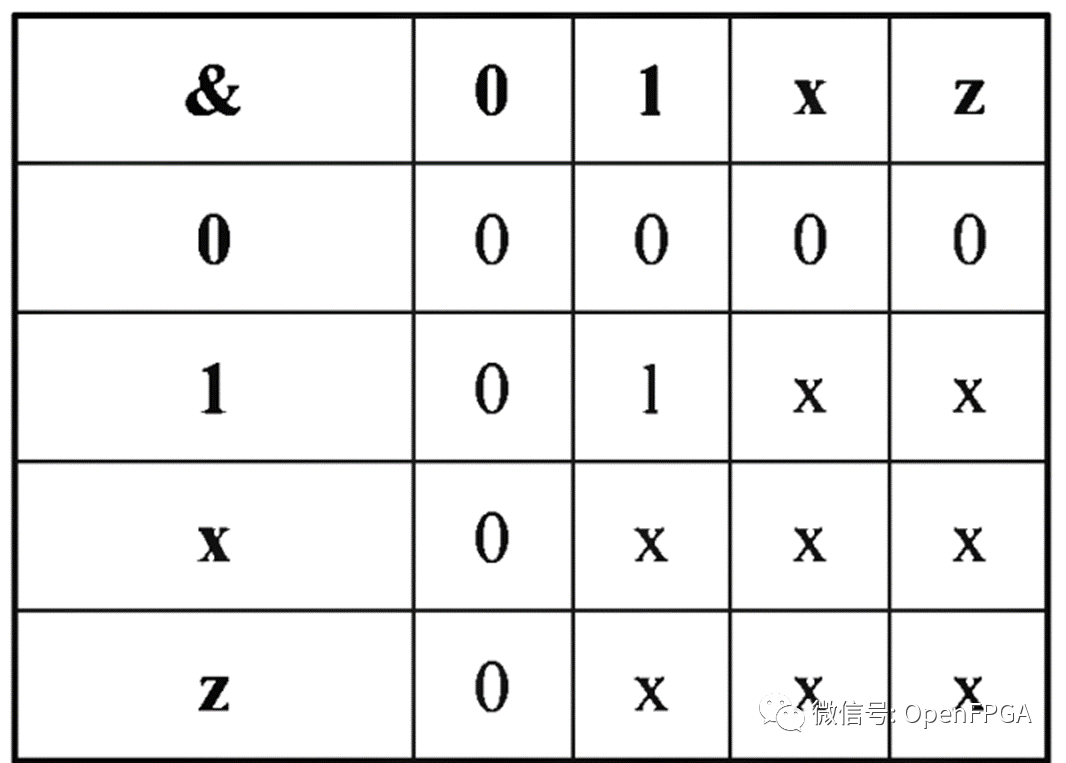

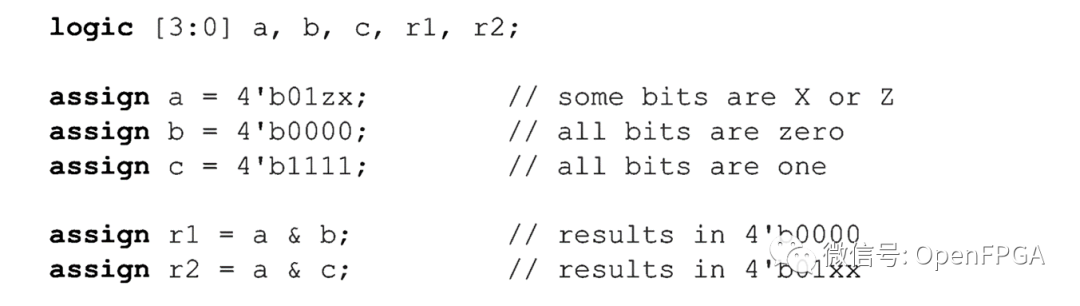

(按)位AND

按位和(Bitwise AND)。位AND運算符對第一個操作數的每一位與第二個操作數中的對應位進行布爾AND運算,從右到左運算。位AND運算符是X-optimistic:0與任何值的AND運算都將得到0。表5-5顯示了位AND的真值表。表中的結果針對兩個操作數的每一位。

位AND運算的一些示例結果如下:

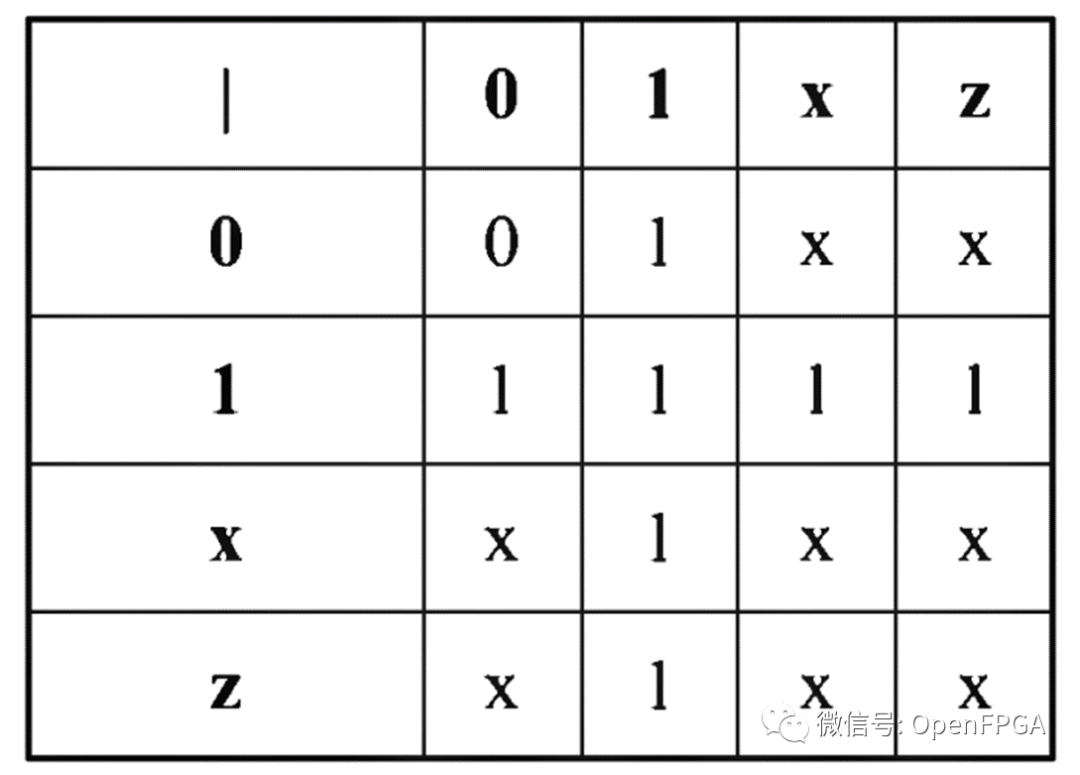

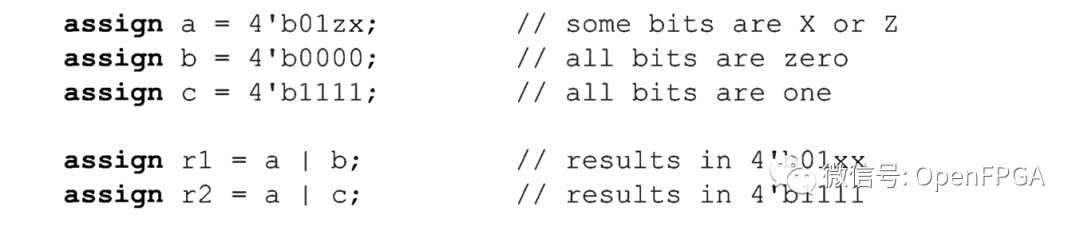

(按)位OR

按位或(Bitwise OR)。位OR運算符對第一個操作數的每一位與第二個操作數中的對應位進行布爾OR運算,從右向左進行運算。位OR運算符是X-optimistic-與任何值進行OR運算結果都是1。表5-6顯示了位OR的真值表。

按位OR運算的一些結果示例如下:

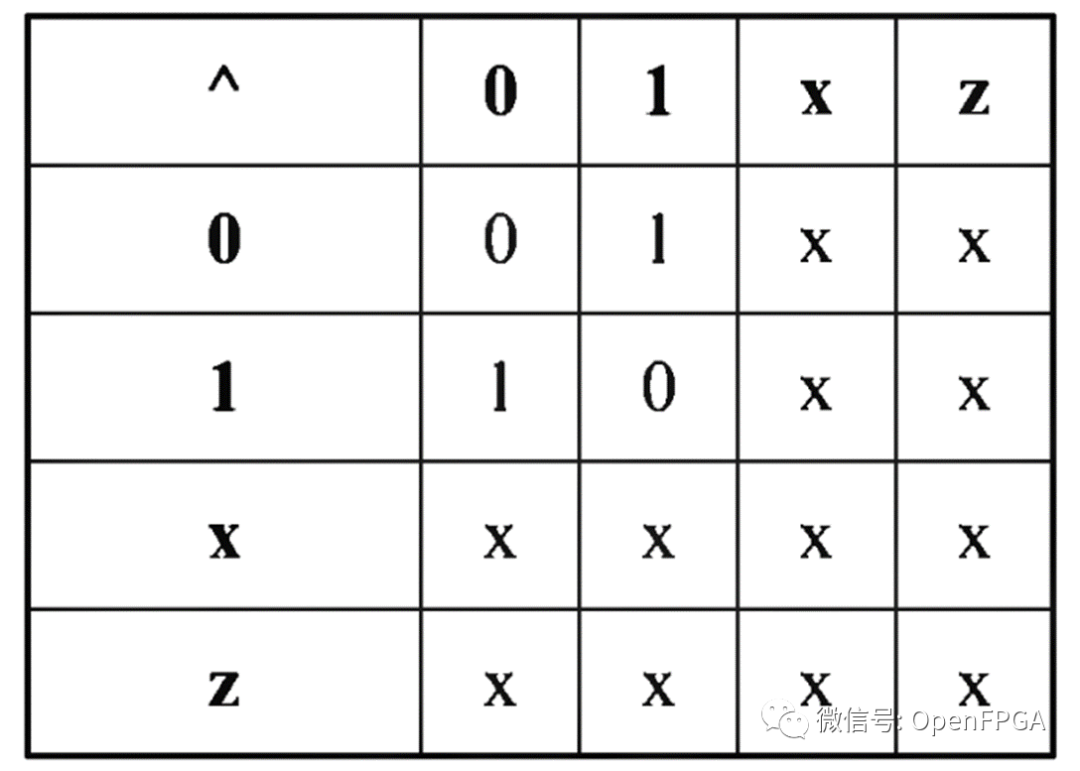

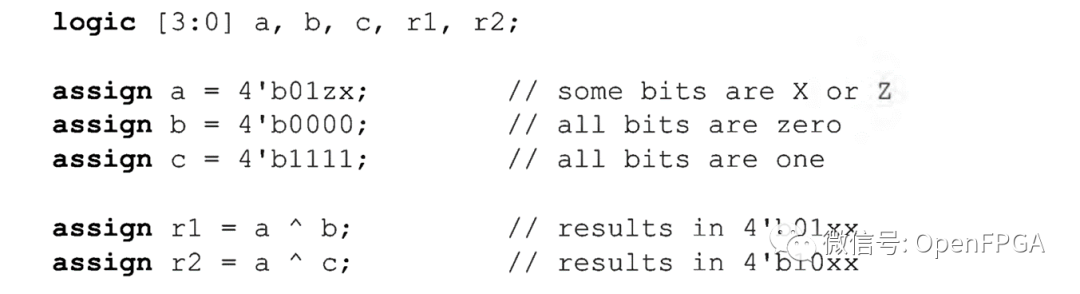

(按)位XOR

按位異或(Bitwise XOR)。位XOR運算符對第一個操作數的每一位與第二個操作數的對應位進行布爾異或XOR運算,從右到左進行運算。按位異或運算符為X-pessimistic——對X或Z值進行異或運算的結果始終為X。表5-7顯示了按位異或的真值表。

按位異或運算的一些示例結果如下:

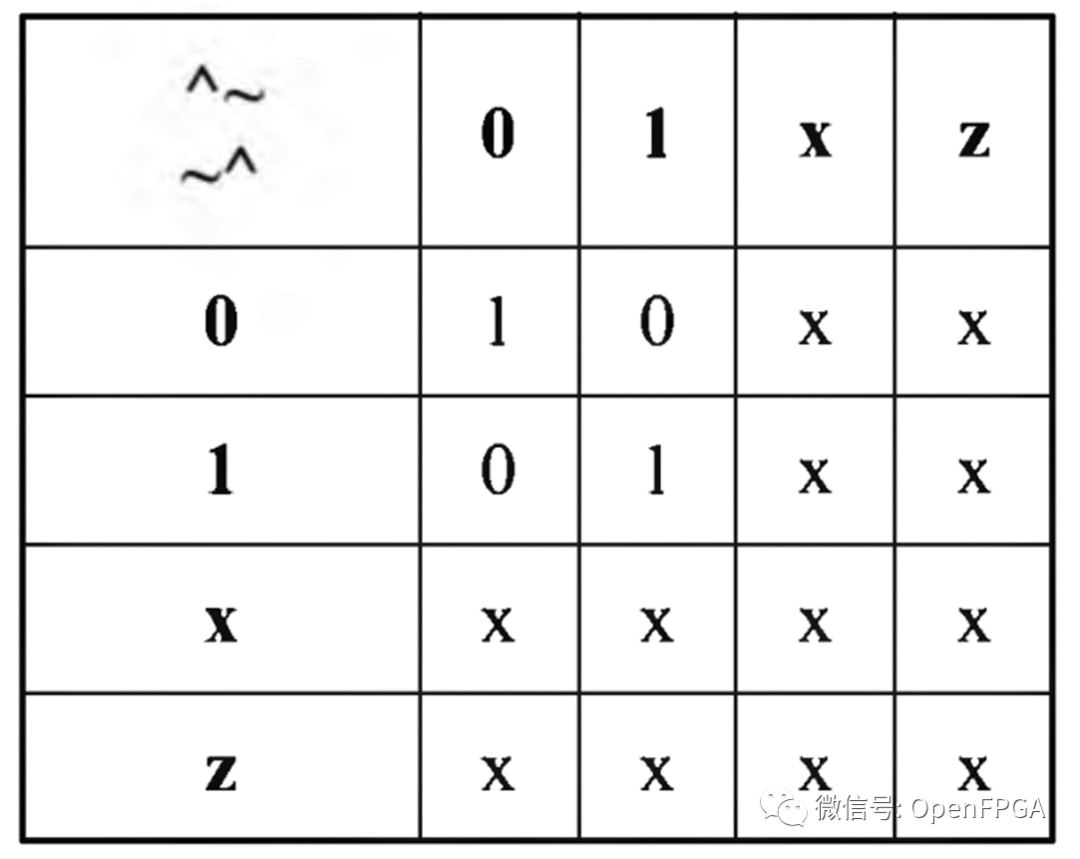

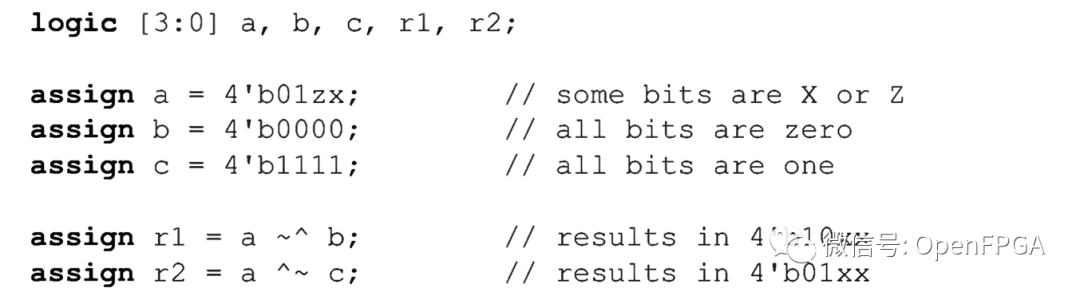

(按)位XNOR

按位XNOR(Bitwise XNOR)。位XNOR運算符對第一個操作數的每一位與第二個操作數的對應位進行布爾XNOR運算,從右到左進行運算。位XNOR運算符為X-pessimistic ——對X或Z值進行XNOR運算的結果為X。表5-8顯示了按位XNOR的真值表。

按位XNOR運算的一些示例結果如下:

示例5-5說明了一個利用按位運算符的小型RTL模型。

//`begin_keywords"1800-2012"//useSystemVerilog-2012keywords

//User-definedtypedefinitions

packagedefinitions_pkg;

typedefenumlogic{AND_OP,XOR_OP}mode_t;

endpackage:definitions_pkg

//MultiplexedN-bitwidebitwise-ANDorbitwise-XORoperation

moduleand_xor

importdefinitions_pkg::*;

#(parameterN=4)//opsize(default8-bits)

(inputmode_tmode,//1-bitenumeratedinput

inputlogic[N-1:0]a,b,//scalableinputsize

outputlogic[N-1:0]result//scalableoutputsize

);

timeunit1ns;timeprecision1ns;

always_comb

case(mode)

AND_OP:result=a&b;

XOR_OP:result=a^b;

endcase

endmodule:and_xor

//`end_keywords

圖5-5顯示了示例5-5中的RTL模型綜合結果,如上一節前面所述,綜合創建的實現可能受到多個因素的影響,包括:目標設備、與運算符一起使用的任何其他運算符或編程語句、使用的綜合編譯器以及指定的綜合選項和約束。

圖5-5:示例5-5的綜合結果:按位AND和OR運算

-

Verilog

+關注

關注

29文章

1367瀏覽量

112319 -

按位運算符

+關注

關注

0文章

3瀏覽量

4835

原文標題:(按)位XNOR

文章出處:【微信號:Open_FPGA,微信公眾號:OpenFPGA】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

數字硬件建模SystemVerilog-按位運算符

數字硬件建模SystemVerilog-按位運算符

評論