數(shù)字硬件建模SystemVerilog-移位運算符

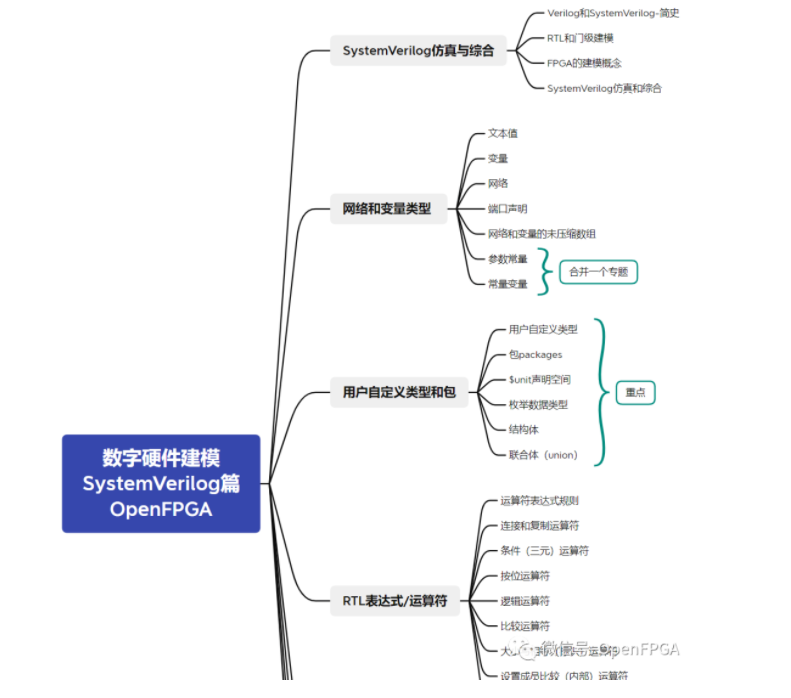

經(jīng)過幾周的更新,SV核心部分用戶自定義類型和包內(nèi)容已更新完畢,接下來就是RTL表達(dá)式和運算符。

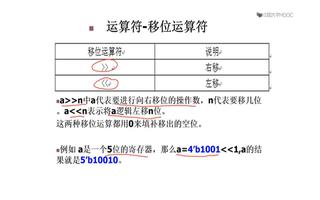

移位運算符

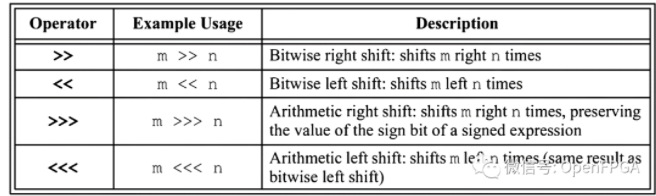

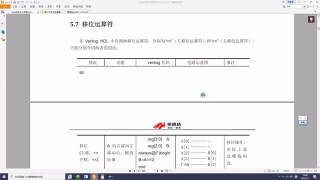

移位運算符將向量的位向右或向左移位指定的次數(shù)。SystemVerilog具有按位和算術(shù)移位運算符,如表5-18所示。

表5-18:RTL建模的移位運算符

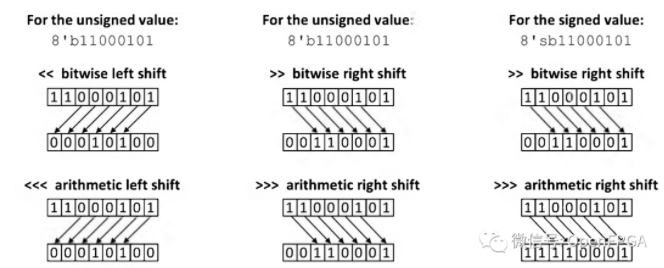

按位移位只是將向量的位向右或向左移動指定的次數(shù),移出向量的位丟失。移入的新位是零填充的。例如,操作8’b11000101 << 2將產(chǎn)生值8’b00010100。按位移位將執(zhí)行相同的操作,無論被移位的值是有符號的還是無符號的。

算術(shù)左移位對有符號和無符號表達(dá)式執(zhí)行與按位右移位相同的操作。算術(shù)右移位對“無符號”和“有符號”表達(dá)式執(zhí)行不同的運算。如果要移位的表達(dá)式是無符號的, 算術(shù)右移位的行為與按位右移相同,即用零填充輸入位。如果表達(dá)式是有符號的,則算術(shù)右移將通過用符號位的值填充每個輸入位來保持值的有符號性。

圖5-11顯示了這些移位操作如何將向量的位移動2位,

圖5-11:按位和算術(shù)移位運算-將值向左或向右移動2位圖5-11:按位和算術(shù)移位運算-將值向左或向右移動2位

可綜合移位操作

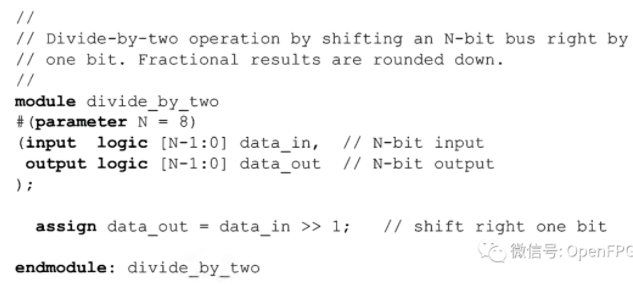

移動固定的次數(shù)。固定次數(shù)的移位操作只需將總線的位重新布線,“輸入位”接地。實現(xiàn)固定移位不需要邏輯門。示例5-11說明了一個簡單的除二組合邏輯模型,其中通過將8位總線右移一位來進(jìn)行除法。

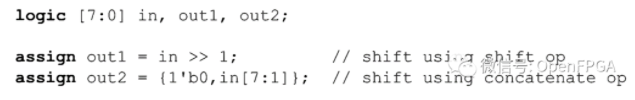

示例5-11:使用移位運算符:通過右移一位除以二

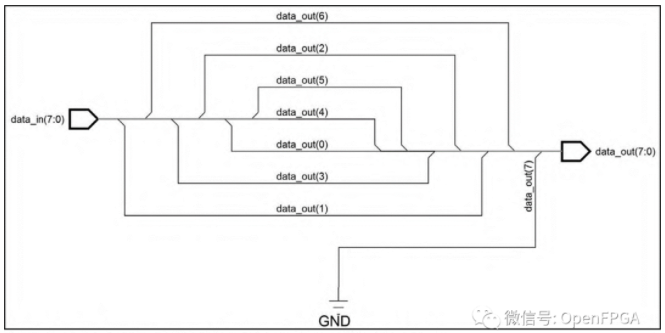

圖5-12顯示了固定位數(shù)的右移是如何綜合的。綜合編譯器在模塊的輸入和輸出上放置了緩沖區(qū),但沒有使用任何額外的門來執(zhí)行操作。

圖5-12:示例5-11的綜合結(jié)果:移位運算符,按1位右移

固定次數(shù)的移位也可以使用連接操作來表示。下面兩行代碼在功能上是相同的。

執(zhí)行移位操作的兩種類型都將綜合為相同的布線硬件,一種類型沒有優(yōu)于另一種類型的優(yōu)勢。

移動次數(shù)可變。可變次數(shù)的移位操作代表是桶形移位器(barrel shifter)的功能,但具體實現(xiàn)將取決于特定目標(biāo)庫中可用的門級功能。一些目標(biāo)設(shè)備可能有一個已經(jīng)針對該設(shè)備進(jìn)行了優(yōu)化的預(yù)構(gòu)建桶形移位器,其他設(shè)備可能需要綜合以從較低級別的門構(gòu)建桶形移位器。

桶形移位器的一個應(yīng)用是用2的冪乘(向左移位)或除(向右移位)。例如,左移1位將值乘以2。左移2位將一個值乘以4。

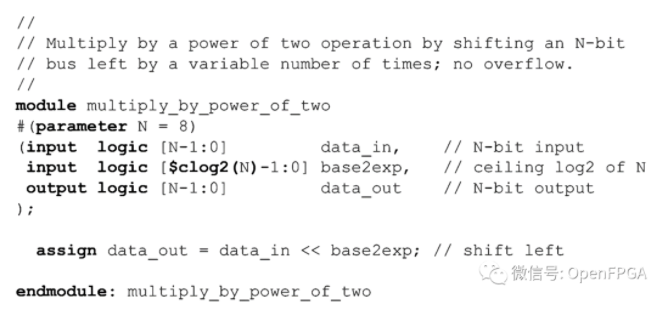

示例5-12顯示了可變左移操作的代碼

示例5-12:使用移位運算符:通過向左移位乘以二的冪

本例中的$ciog2系統(tǒng)函數(shù)用于計算base2exp輸入端口的寬度。此函數(shù)用于返回一個log2值的的上限(分?jǐn)?shù)向上舍入到下一個整數(shù))。該函數(shù)是計算一個值需要多少位的便捷方法。

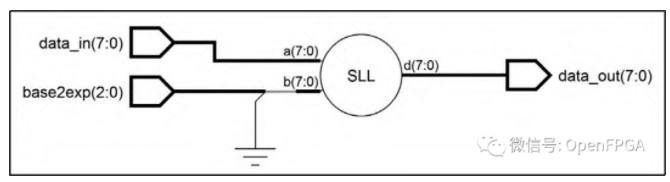

圖5-13說明了該模型可能如何綜合。該示意圖是“在將移位功能映射并優(yōu)化”到特定設(shè)備之前的“中間綜合結(jié)果”。通用的“左移位邏輯”組件表示未映射的移位操作。

圖5-13:綜合結(jié)果“例如5-12:移位運算符,可變左移位”

綜合結(jié)果中的通用左移分量對其兩個輸入具有相同的位數(shù)。base2exp輸入未使用的高位與地相連。當(dāng)綜合將通用左移組件映射到特定的目標(biāo)實現(xiàn)時,這些未使用的位可能會被刪除。

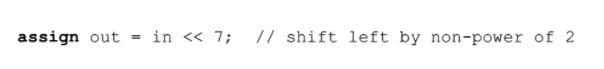

移位運算符可用于乘以或除以除2的冪以外的值,以下示例將向量移動7次。

可以在硬件中使用cading shift實現(xiàn)非2次方的移位,例如,操作可以通過鏈接4位左移位器、2位左移位器和1位左移位器來完成7次左移位。

讓綜合器完成它的工作!綜合使工程師能夠在抽象層次上進(jìn)行設(shè)計,專注于功能,而不必陷入實現(xiàn)細(xì)節(jié)的泥潭,也不必過度關(guān)注特定ASIC或FPGA的功能。綜合編譯器將抽象功能模型轉(zhuǎn)換為目標(biāo)ASIC或FPGA的有效實現(xiàn)。雖然可以在更詳細(xì)的層面上仿真barrel shift行為,但這樣做通常沒有好處。現(xiàn)代綜合編譯器使用移位運算符識別抽象RTL模型中的barrel shift行為,并將在目標(biāo)設(shè)備中生成此功能的最佳實現(xiàn)。對于不同的目標(biāo)設(shè)備,這種實現(xiàn)可能會有所不同,具體取決于該設(shè)備中可用的標(biāo)準(zhǔn)單元、LUT或門陣列。

-

Verilog

+關(guān)注

關(guān)注

29文章

1366瀏覽量

111869 -

System

+關(guān)注

關(guān)注

0文章

166瀏覽量

37584 -

運算符

+關(guān)注

關(guān)注

0文章

172瀏覽量

11353

發(fā)布評論請先 登錄

18_移位運算符 [001100000064] - 第1節(jié) #硬聲創(chuàng)作季

18_移位運算符 [001100000064] - 第3節(jié) #硬聲創(chuàng)作季

VHDL中移位運算符的實現(xiàn)之SLL使用

【FPGA】VHDL 語言的運算符有哪些?計算的優(yōu)先級是怎樣的?

【夢翼師兄今日分享】 常見的關(guān)系運算符(移位運算符)

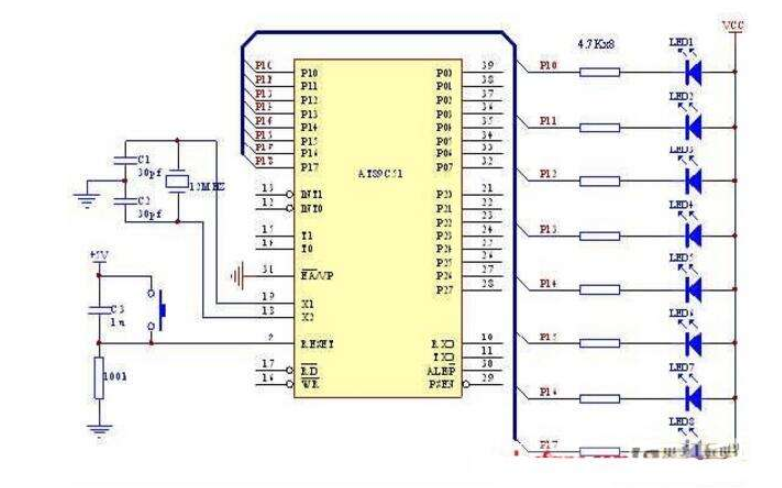

FPGA入門實驗教程之進(jìn)行LED跑馬燈實驗的詳細(xì)資料說明

數(shù)字設(shè)計FPGA應(yīng)用:移位運算符

FPGA入門系列教程之進(jìn)行LED流水燈的實驗資料免費下載

移位運算符的應(yīng)用實例講解

什么是移位運算符

什么是移位運算符

評論