1. 緒論

經過了立項和規格和計劃的確認,此處我們開始講芯片設計。

這個內容就挺多了,也可能是大家最關心的一個部分,可能要分幾次講。在整個流程中處于這位置。

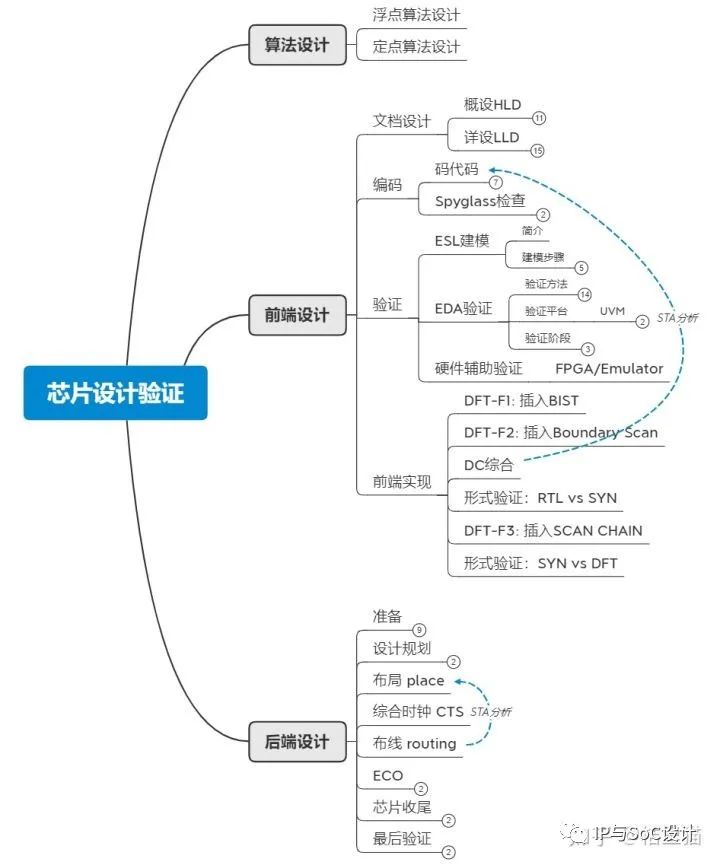

此處由于我自己還是對數字芯片系統更了解,所以按數字的來。模擬芯片的設計流程后續有精力或者請個大佬補個概述。芯片的設計流程還是比較長的,我們先來個birdmap。這個圖很復雜,看不懂的名詞不要慌,我會一步一步講。

2. 算法設計

我們先來講第一部分,這個部分其實比較簡單。所以就在此處講講,后續不再單獨開章節來講這個東西。芯片最終還是算法的一種加速。如果一個東西你用C++都實現不了,芯片怎么可能實現。第一步就是算法。

算法實現其實有兩個步驟的。為什么有兩個步驟呢,這就涉及到浮點和定點的區別。浮點精讀高,但是硬件實現代價大,定點成本低,硬件實現代價小。一般先設計浮點算法,然后再犧牲一點精度,搞成定點算法。

浮點算法設計浮點算法偏重于功能,由于浮點精度高,最原始的功能一般會用浮點實現。比如你要整一個AI芯片,你首先得用pytorch或者tensorflow訓練出一個浮點網絡,看看效果是不是還行,能不能實現網絡正常的功能。算法鏈路先測試好了后續才能用芯片加速。浮點算法一般由純軟件工程師設計的。他們并不需要知道硬件實現,只需要對功能的正確性負責即可。

定點算法設計定點算法就是找個位置,把浮點中的指數為給歸一了。精度是肯定會損失的,但是換來了硬件設計的簡單。這個也容易理解,用芯片算一個3.5+0.025和用芯片算一個3500+25復雜程度完全不一樣啊。為了平衡精度和定點位寬,此處定點化可以有各種門道,比如采用批處理的定點化,一部分數據采用一個定點位置,另一部分數據采用另一個定點位置等等。總之就是,這一步實現的是如何用最小的定點位寬,在精度可接受的前提下實現浮點的算法。

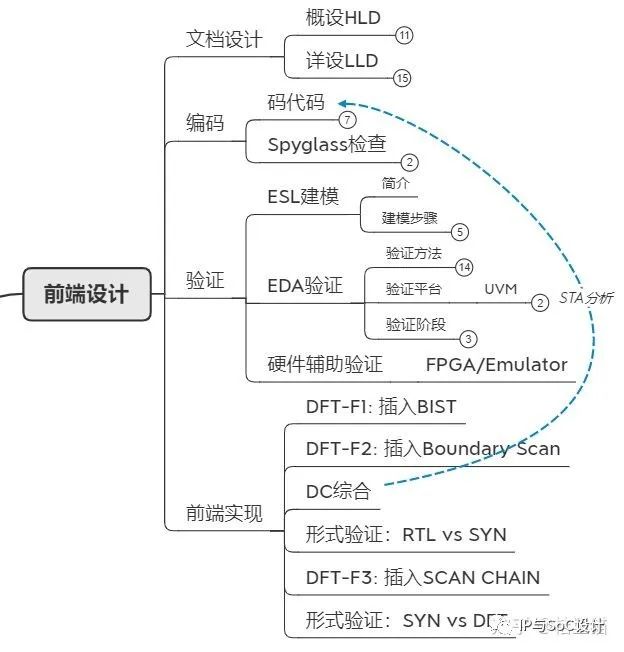

3. 前端設計

和其他一些復雜的東西類似,比如編譯器,網站等等類似,芯片設計也有前端和后端之分,前端到網表,后端到版圖。

前端主要包含4個步驟:文檔設計、編碼、驗證、前端實現。主要就是從設計需求到網表的一個流程。

4. 后端設計

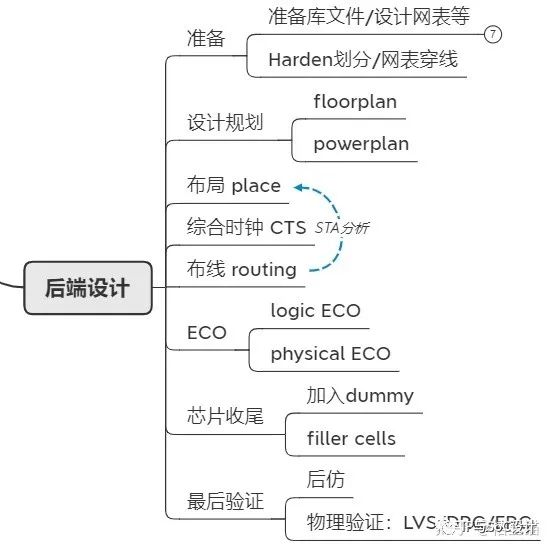

這個步驟,主要是把網表整成我們最后的版圖。可以直接丟給代工廠生產了。

一共7個步驟。此處給個概述,后面專門寫文章介紹。

準備:這一個步驟中準備主要是準備一些庫文件,前端準備好的網表,劃分好harden, 然后穿線。

設計規劃:設計規劃主要是擺放一些大件,比如memory硬核,IO PAD, 電源網絡等等,方便下一個步驟擺放小單元。

布局:這個步驟就把具體的單元擺放到版圖上。

綜合時鐘:把時鐘網絡擺放好,保證到各個地方的長度都差不多。

布線:真正把線聯通。此處會通過STA,不斷調整布局以及routing。

ECO:版圖搞定后,需要工程師手動修一些東西。

芯片收尾:加入dummy, filler cells等等,讓密度滿足光刻需求。

最后驗證:交芯片前,最后再驗證一把。主要包含了后仿,形式驗證,物理驗證。

這7個步驟完成以后,就可以交版圖給代工廠了,接下來就是等芯片回片。

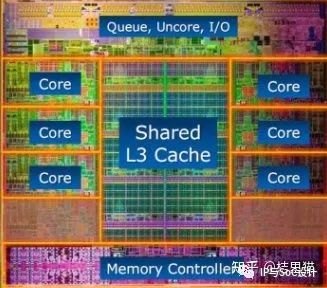

最后的輸出大概這設個樣子的。

5. 總結

本篇內容是芯片設計的提綱。這個階段的輸入是設計需求,輸出是芯片版圖。設計主要涉及到3方面的內容,算法設計,芯片前端設計,芯片后端設計。一整個流程很長,至此芯片的設計過程就結束了,下一個過程就是制造!

審核編輯 :李倩

-

芯片

+關注

關注

459文章

52308瀏覽量

437907 -

算法

+關注

關注

23文章

4702瀏覽量

94976 -

數字芯片

+關注

關注

1文章

115瀏覽量

18743

原文標題:一顆芯片的前世今生:設計(流程概述)

文章出處:【微信號:IP與SoC設計,微信公眾號:IP與SoC設計】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

超大規模芯片驗證:基于AMD VP1902的S8-100原型驗證系統實測性能翻倍

數字IC設計:方法、技巧與實踐

神眸2025春季新品發布會:以芯片創新引領AI智能影像新時代,發布極致低功耗「研極芯」

芯原推出業界領先的車規級智慧駕駛SoC設計平臺

新思科技利用人工智能加速芯片設計流程

大規模硬件仿真系統的編譯挑戰

芯片失效分析的方法和流程

數字設計ic芯片流程

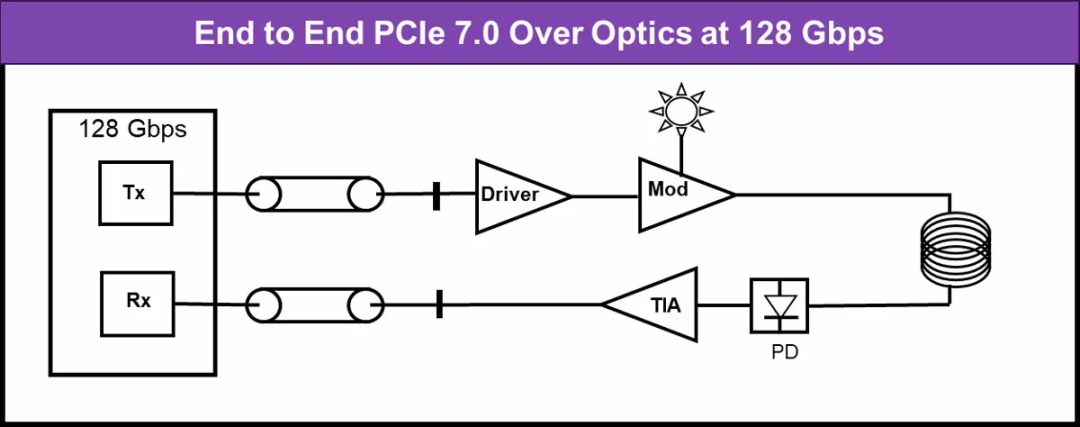

PCIe光傳輸的優勢與挑戰

新思科技7月份行業事件

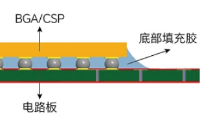

芯片底部填充工藝流程有哪些?

芯片的設計流程

芯片的設計流程

評論