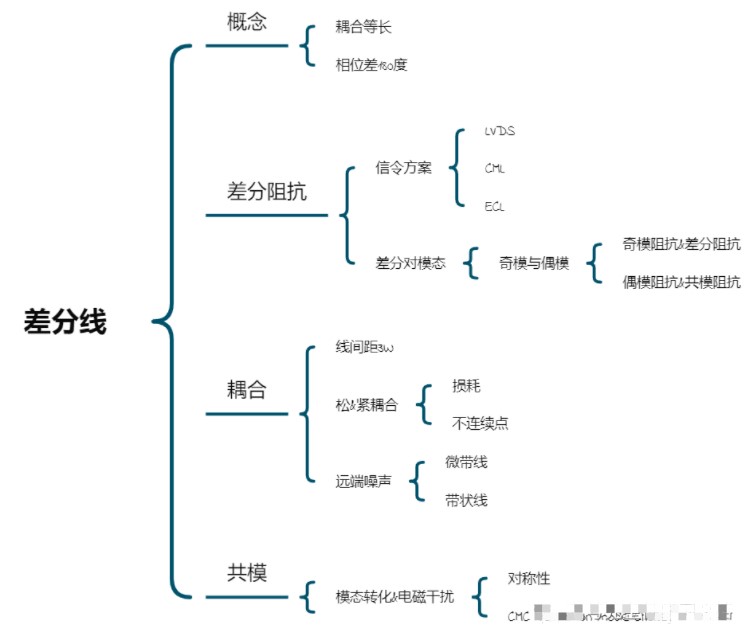

整個基礎(chǔ)知識體系中,差分線(對)是很難搞的部分,卻是最常用的部分。說到差分線基礎(chǔ)知識,里面的概念很多,記得剛接觸的時候,奇模&共模有時候會搞不清楚。話不多說,直接上圖:

1、概念

差分線從理論上說,可以是任意兩根傳輸線。

最初的時候,曾有疑惑:距離很遠的兩根傳輸線呢?實際工作中,很多高速線都是差分線,更多的是利用其抗干擾的能力。既然講到抗干擾,那是不是盡量保證兩根線的周圍環(huán)境一致。

所以,差分線的定義:兩條存在耦合且平行等長的兩根傳輸線,用來傳輸相位差180度的信號。

2、差分阻抗

差分線本身沒有什么特別,決定它們特性的是這兩條傳輸線上的信號傳輸方式。差分線除了傳輸差分信號,還有共模信號,前一種是大小相等方向相反的驅(qū)動電壓,后一種是相等方向相同的驅(qū)動電壓。

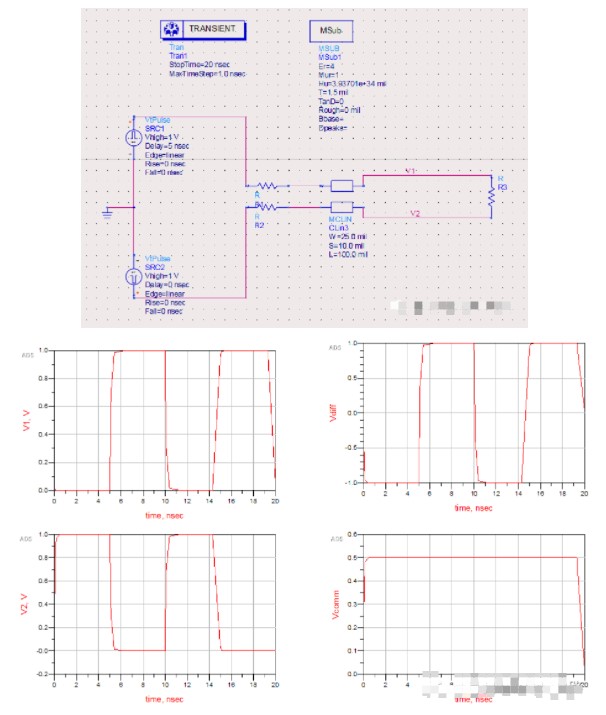

為了方便理解,針對差分阻抗的特性,搭建相關(guān)鏈路:

Vdiff = V1–V2 Vdiff 表示差分線號

Vcomm= (V1+V2) Vcomm表示共模信號

V1表示線1相對于其返回路徑的信號電壓

V2表示線2相對于其返回路徑的信號電壓

從仿真結(jié)果看出:相同電平的幅值,差分線的峰峰值是單端線的兩倍。單端線的基準是地平面,外界的干擾差異會很大;而差分線的基準是彼此,對共模干擾有很好的抑制。

差分線最重要的電特性就是對差分信號的阻抗,稱為差分阻抗。

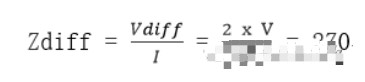

以Z=V/I來推算:

Z0單端信號線的特性阻抗

差分阻抗還可以看成兩條單端信號線等效阻抗的串聯(lián):

Zdiff = Z0 +Z0 = 2 x Z0

Zdiff 表示兩條信號線之間的等效阻抗(即差分阻抗)

Z0 表示每條信號線與返回路徑之間的阻抗

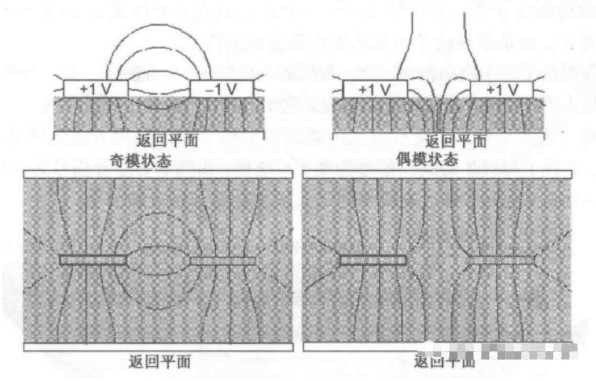

上面計算方法可以得出差分阻抗,由差分阻抗引出兩種模態(tài):

奇模阻抗

奇模阻抗與差分阻抗有直接的關(guān)系。差分阻抗是差分信號受到的阻抗,奇模阻抗是傳輸線處于奇模狀態(tài)時每條信號線的阻抗。

偶模阻抗

共模信號使差分對處于偶模狀態(tài)。當傳輸線上傳播共模信號時,此時每條線的特性阻抗稱為偶模特性阻抗。

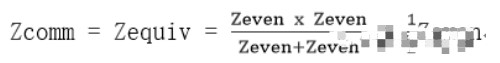

對于共模信號而言,阻抗是每條線特性阻抗的并聯(lián)。兩個偶模阻抗的并聯(lián)阻值:

Zcomm表示共模阻抗

Zeven表示當差分對處于偶模狀態(tài)時每條線的特性阻抗

信令方案有多種,最常用的就是LVDS低壓差分信號。

需要注意的是:LVDS 信號不僅有差分信號還有共模信號,只不過默認共模信號是沒有變化的直流。

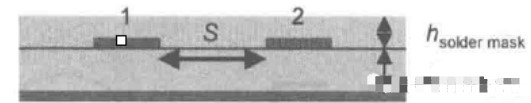

除了常規(guī)的線寬線距,介質(zhì)厚度等因素對差分阻抗的影響。最近有寫阻焊相關(guān)的發(fā)明,發(fā)現(xiàn)隨著阻焊層厚度的增加,緊耦合的情況下,阻焊層對奇模阻抗影響比較大,差分阻抗偏離值高達10%。設(shè)計表面層信號線差分阻抗時要考慮阻焊層的原因,這也是為什么差分線建議走內(nèi)層的原因之一。

上面講的概念都是無耦合的情況,如果考慮耦合,就引入了共模干擾的問題。

3、耦合

寫到耦合的時候,想起之前有和同事聊過:關(guān)于差分線,因為相互耦合,一條線的返回路徑可不可以是另外一條線?

當?shù)仄矫姘l(fā)生不連續(xù)的時候,無參考平面的區(qū)域,差分走線之間的耦合才會提供主要的回流通路。這是沒有任何問題的。

其實上面說差分線的一條線的返回電流由另一條線傳輸,還有一個前提條件:當信號線與返回路徑平面之間的距離大于等于兩條信號線距離(包含線寬)。

但是共模信號怎么辦?不給共模信號提供地阻抗回路,勢必會造成EMI 輻射,引入電磁干擾。相互作為回流路徑的做法弊大于利。

在實際工作中,大多數(shù)板級互連中,信號線與平面之間的耦合度遠大于兩條信號線之間的耦合度,所以此時平面的返回電流十分重要。此時,第一條信號線的返回電流不能看成由第二條信號線運送。

線間距3倍線寬(3W)的情況,耦合很小,可以忽略。考慮兩條線之間的耦合,當線間距的減小,奇模阻抗減小,偶模阻抗增加,對應(yīng)的差分阻抗減小,共模阻抗增加。相對于3W的情況,差分阻抗減小了約12%。

遠端串擾

如果差分對為同介質(zhì)的,比如帶狀線,兩種模態(tài)的傳播速度相同,差分對就不會出現(xiàn)遠端噪聲。如果差分對為不同介質(zhì)的,比如微帶線,那么奇模的有效介電常數(shù)比偶模小,奇模有更快的傳播速度。差分信號分量比共模分量先到達末端,相互間造成遠端噪聲。

緊耦合與松耦合

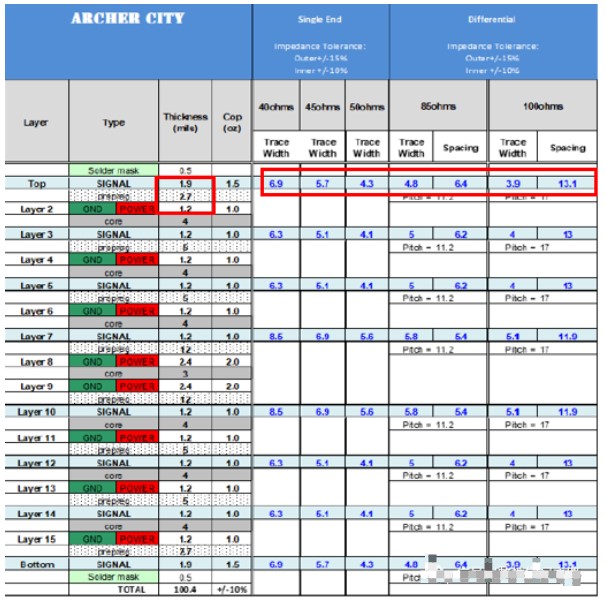

下圖為阻抗計算軟件算出差分阻抗為85 ?,線間距差別比較大:

一般松耦合經(jīng)驗值為線間距大于2倍的線寬

返回平面受損時,例如在雙絞線電纜、帶狀電纜、連接器和一些集成電路封裝中,使用緊耦合。緊耦合對減小串擾有很強的作用。

緊耦合情況下,差分阻抗和共模阻抗受耦合的影響依然很小。在最緊耦合下,差分阻抗僅減小了10%。

一般規(guī)則:高速率產(chǎn)品,損耗要求較嚴,應(yīng)當使用松耦合的差分對。消費類產(chǎn)品,成本要求較嚴,應(yīng)使用緊耦合的差分對。

4、共模信號

我們主要用差分線傳輸差分信號,但在實際的鏈路中,任何不對稱因素(串擾、驅(qū)動器錯位、線長偏差及不對稱的負載等)都會使部分差分信號轉(zhuǎn)化為共模信號。

共模信號的產(chǎn)生及改變,危害就是會引起誤碼,引入過量電磁干擾。消費類的產(chǎn)品,一般都進行相關(guān)電磁輻射測試,這就需要我們在實際工作中進行管控。如何使共模信號的影響降到最小:

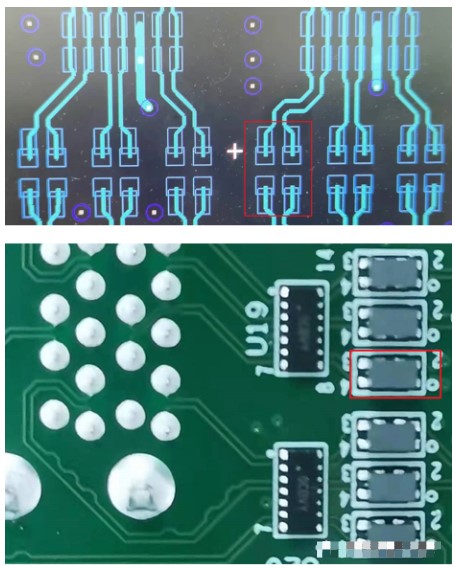

1.鏈路做到盡量對稱。過孔轉(zhuǎn)換&等長匹配&出Pin區(qū)域等。

2.增加共模信號扼流器CMC(Common mode Choke),起到EMI濾波的作用,用于抑制高速信號線產(chǎn)生的電磁波向外輻射發(fā)射。

實際應(yīng)用

講到電磁干擾,還有一種情況需要說明:雙絞線是否使用屏蔽?

屏蔽對差分阻抗影響其實不大,屏蔽的重要作用在于為共模電流提供一個返回路徑,從而減小它的輻射效應(yīng)。

審核編輯:劉清

-

lvds

+關(guān)注

關(guān)注

2文章

1118瀏覽量

67143 -

差分阻抗

+關(guān)注

關(guān)注

1文章

27瀏覽量

10489 -

共模信號

+關(guān)注

關(guān)注

1文章

86瀏覽量

14354 -

差分線

+關(guān)注

關(guān)注

0文章

38瀏覽量

9076 -

驅(qū)動電壓

+關(guān)注

關(guān)注

0文章

94瀏覽量

13673

發(fā)布評論請先 登錄

差分線是如何去定義的呢

差分線是如何去定義的呢

評論