目前為止,常見的電路包括多路復(fù)用器、解復(fù)用器、編碼器、解碼器、奇偶校驗(yàn)發(fā)生器和校驗(yàn)器等被稱為組合邏輯電路。在這些類型的電路中,輸出僅取決于輸入的當(dāng)前狀態(tài),而不取決于輸入或輸出的過去狀態(tài)。

除了很小的傳播延遲外,當(dāng)輸入發(fā)生變化時(shí),組合邏輯電路的輸出會(huì)立即發(fā)生變化。

還有另一類電路,其輸出不僅取決于當(dāng)前輸入,還取決于過去的輸入/輸出。這些類型的電路稱為順序邏輯電路。那么,如何獲得“之前的輸入/輸出”數(shù)據(jù)?所以必須有某種“內(nèi)存”來存儲(chǔ)數(shù)據(jù)以備后用。可以存儲(chǔ)數(shù)據(jù)并充當(dāng)“內(nèi)存”單元的設(shè)備或電路稱為鎖存器或觸發(fā)器。

使用反相器的觸發(fā)器

觸發(fā)器是一種基本的存儲(chǔ)單元,可以存儲(chǔ)1位數(shù)字信息。它是一個(gè)雙穩(wěn)態(tài)電子電路,即它有兩種穩(wěn)定狀態(tài):高或低。由于觸發(fā)器是雙穩(wěn)態(tài)元件,其輸出保持在任一穩(wěn)定狀態(tài),直到應(yīng)用外部事件(稱為觸發(fā))。

由于它在應(yīng)用輸入后很長時(shí)間仍保留輸出(除非進(jìn)行了某些更改),因此觸發(fā)器可以被視為存儲(chǔ)設(shè)備,它可以存儲(chǔ)一個(gè)二進(jìn)制位。

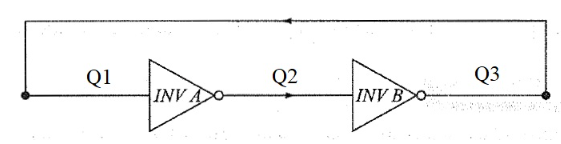

可以使用兩個(gè)串聯(lián)的反相器設(shè)計(jì)一個(gè)簡單的觸發(fā)器,從第二個(gè)反相器的輸出到第一個(gè)反相器的輸入的反饋。以下電路顯示了使用反相器的觸發(fā)器:

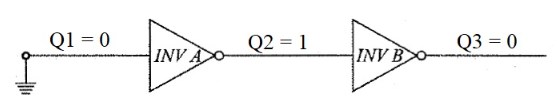

令Q1為輸入,Q3為輸出。最初,假設(shè)反饋已斷開,并且通過將Q1連接到地而使其變?yōu)?(邏輯0、低電平、位0)。Q3也將為0。現(xiàn)在,如果連接了反饋并且輸入Q1與地?cái)嚅_,則Q3仍將繼續(xù)為0。

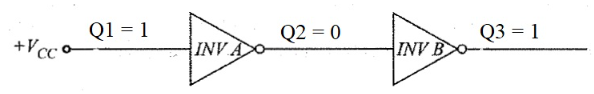

同樣,如果用1(邏輯1,高電平,位1)重復(fù)相同的過程,而不是接地,則輸出Q 3保持在 1。

上面是一個(gè)簡單的觸發(fā)器,有兩個(gè)穩(wěn)定狀態(tài),它保持在一個(gè)特定的狀態(tài),因此是一個(gè)內(nèi)存,直到出現(xiàn)外部事件觸發(fā)(這種情況下比如輸入變化)。

SR觸發(fā)器

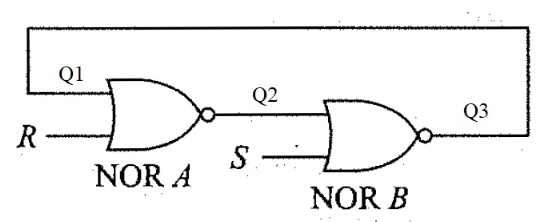

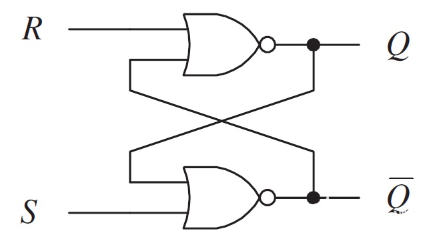

上述基于反相器的觸發(fā)器只是為了理解工作原理,但它沒有任何實(shí)際用途,因?yàn)闆]有提供任何輸入。這就是NOR和NAND門發(fā)揮作用的地方。其實(shí),上述基于反相器的觸發(fā)器可以使用NOR門實(shí)現(xiàn),如下圖所示:

現(xiàn)在忽略“R”和“S”值,這里以更傳統(tǒng)的形式重新繪制上述電路,并將Q2重命名為Q ,將Q3重命名為Q-(注意,字母上面的一橫表示低電平有效,為方便寫出,本文以“-”代替一橫)。

可以看出,觸發(fā)器有兩個(gè)輸入:R和S以及兩個(gè)輸出:Q和Q-,從表示中可以清楚地看出輸出是相互補(bǔ)充的。現(xiàn)在嘗試分析輸入的不同可能性及其對(duì)應(yīng)的輸出。

這里要注意的重要一點(diǎn)是,對(duì)于NOR門,邏輯“1”是主要輸入,如果其任何一個(gè)輸入是邏輯“1”(高),則輸出為邏輯“0”(低),不考慮其它輸入。

情況1:R = 0和S = 0

在第一種情況下,兩個(gè)或非門的輸入都是邏輯“0”。由于它們都不是主要輸入,因此它們對(duì)輸出沒有影響。因此,輸出保留了它們以前的狀態(tài),即輸出沒有變化。此條件稱為保持條件或無變化條件。

情況2:R = 0且S = 1

在這種情況下,“S”輸入為1,這意味著或非門B的輸出將變?yōu)?。結(jié)果,或非門A的兩個(gè)輸入都變?yōu)?,因此或非門A的輸出和因此Q的值為1(高)。由于輸入S處的“1”使輸出切換到其穩(wěn)定狀態(tài)之一并將其設(shè)置為“1”,因此S輸入稱為SET(置位)輸入。

情況3:R = 1且S = 0

在這種情況下,“R”輸入為1,這意味著或非門A的輸出將變?yōu)?,即Q為 0(低電平)。結(jié)果,或非門B的兩個(gè)輸入都變?yōu)?,因此或非門B的輸出為1(高電平)。由于輸入R處的“1”使輸出切換到其穩(wěn)定狀態(tài)之一并將其重置為“0”,因此R輸入稱為RESET(復(fù)位)輸入。

情況4:R = 1 且 S = 1

這種輸入條件是禁止的,因?yàn)樗鼤?huì)強(qiáng)制兩個(gè)或非門的輸出變?yōu)?,這違反了互補(bǔ)輸出。即使應(yīng)用了此輸入條件,如果下一個(gè)輸入變?yōu)镽 = 0和S = 0(保持條件),也會(huì)導(dǎo)致或非門之間出現(xiàn)“競爭條件”,從而導(dǎo)致輸出處于不穩(wěn)定或不可預(yù)測的狀態(tài)。

因此,根本不使用輸入條件 R = 1和S = 1。

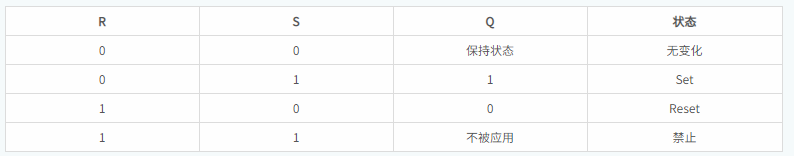

所以,基于上述情況和不同的輸入組合,SR觸發(fā)器的真值表如下表所示。

SR觸發(fā)器的邏輯符號(hào)如下所示:

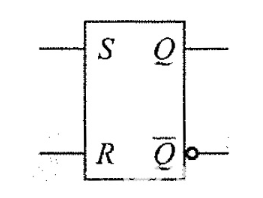

使用NAND門的SR觸發(fā)器(技術(shù)上稱為RS-觸發(fā)器)

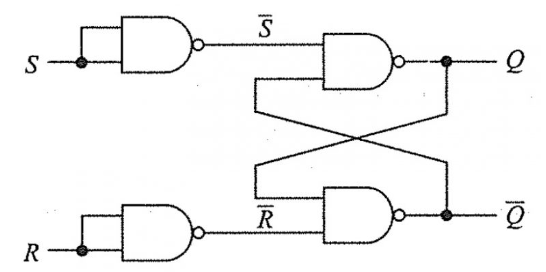

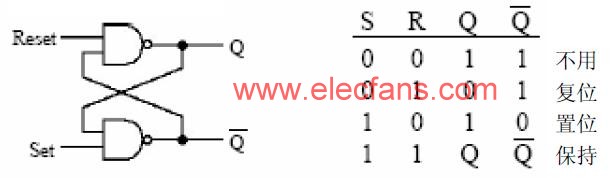

SR觸發(fā)器也可以通過兩個(gè)NAND門的交叉耦合來設(shè)計(jì),但是Hold和Forbidden狀態(tài)是相反的。它是一個(gè)低電平有效輸入SR觸發(fā)器,因此稱之為RS-觸發(fā)器。使用與非門的SR觸發(fā)器電路如下圖所示:

關(guān)于NAND門的一個(gè)重要點(diǎn)是它的主要輸入是0,即,如果它的任何輸入是邏輯“0”,則輸出是邏輯“1”,而與其他輸入無關(guān)。僅當(dāng)所有輸入為1時(shí),輸出為0。考慮到這一點(diǎn),下面看看基于NAND的RS-觸發(fā)器的工作原理。

情況1:R- = 1且S- = 1

當(dāng)S-和R-輸入都為高時(shí),輸出保持在先前的狀態(tài),即它保存先前的數(shù)據(jù)。

情況2:R- = 1 且S- = 0

當(dāng)R-輸入為HIGH且S-輸入為LOW時(shí),觸發(fā)器將處于SET狀態(tài)。當(dāng)R-為高時(shí),與非門B的輸出,即Q-變?yōu)榈汀_@導(dǎo)致與非門A的兩個(gè)輸入都變?yōu)榈碗娖剑虼伺c非門A的輸出即Q變?yōu)楦唠娖健?/p>

情況 3:R- = 0且S- = 1

當(dāng)R-輸入為LOW且S-輸入為HIGH時(shí),觸發(fā)器將處于RESET狀態(tài)。由于S-為高電平,與非門A的輸出即Q變?yōu)榈碗娖健_@導(dǎo)致與非門B的兩個(gè)輸入都變?yōu)榈碗娖剑虼伺c非門B的輸出即Q-變?yōu)楦唠娖健?/p>

情況 4:R- = 0且S- = 0

當(dāng)R-和S-輸入均為低電平時(shí),觸發(fā)器將處于未定義狀態(tài)。因?yàn)镾和R的低輸入,違反了觸發(fā)器的規(guī)則,即輸出應(yīng)相互補(bǔ)充。因此,觸發(fā)器處于未定義狀態(tài)(或禁止?fàn)顟B(tài))。

下面的真值表總結(jié)了在NAND門SR觸發(fā)器的工作原理:

另外,通過反轉(zhuǎn)輸入可以將使用NAND門的RS-觸發(fā)器轉(zhuǎn)換為具有與常規(guī)SR觸發(fā)器相同的真值表。除了使用反相器,還可以使用具有公共輸入的與非門,如下圖所示。

簡單SR觸發(fā)器的問題在于它們對(duì)控制信號(hào)的電平敏感(盡管圖中未顯示),這使得它們成為透明設(shè)備。為了避免這種情況,引入了門控或時(shí)鐘SR觸發(fā)器(無論何時(shí)使用SR 觸發(fā)器,它通常指的是時(shí)鐘SR觸發(fā)器)。時(shí)鐘信號(hào)使設(shè)備邊沿敏感(因此沒有透明度)。

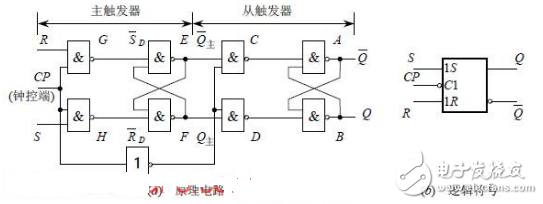

時(shí)鐘SR觸發(fā)器

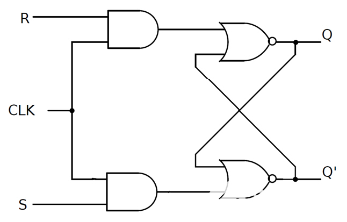

目前主要有兩種類型的時(shí)鐘SR觸發(fā)器,分別是基于NAND和NOR。使用NAND門的時(shí)鐘SR觸發(fā)器電路如下圖所示:

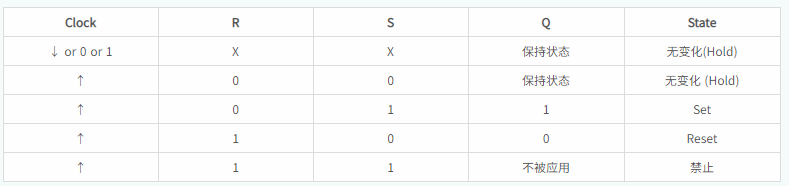

該電路是通過在基于NAND的SR觸發(fā)器上添加兩個(gè)NAND門而形成的。當(dāng)額外的與非門反轉(zhuǎn)輸入時(shí),輸入為高電平有效。時(shí)鐘脈沖作為兩個(gè)額外與非門的輸入。因此,時(shí)鐘脈沖的轉(zhuǎn)換是該設(shè)備運(yùn)行的關(guān)鍵因素。現(xiàn)在假設(shè)它是一個(gè)上升沿觸發(fā)設(shè)備,這個(gè)觸發(fā)器的真值表如下所示:

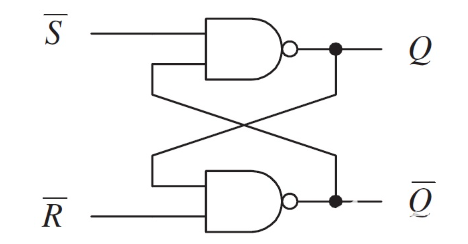

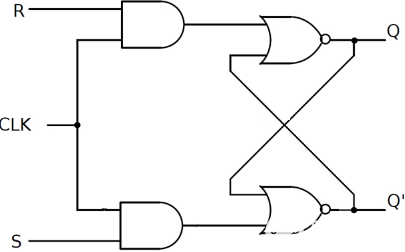

同樣可以通過使用或非門來實(shí)現(xiàn)。使用NOR門的時(shí)鐘SR觸發(fā)器電路如下所示:

上圖圖顯示了RS觸發(fā)器的結(jié)構(gòu)(因?yàn)镽與輸出Q相關(guān)聯(lián)),SET和RESET的功能保持不變,即當(dāng)S為高電平時(shí),Q設(shè)置為 1,當(dāng) R為高電平時(shí),Q為重置為0。

應(yīng)用示例

SR觸發(fā)器是非常簡單的電路,但由于其非法狀態(tài),S和R都為高電平(S = R = 1),因此在實(shí)際電路中沒有廣泛使用。但它們用于開關(guān)電路,因?yàn)樗鼈兲峁┖唵蔚拈_關(guān)功能(在置位和復(fù)位之間)。

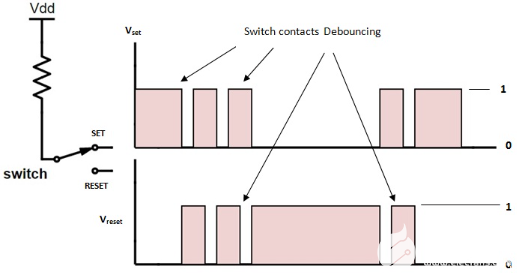

一種這樣的應(yīng)用是開關(guān)去抖動(dòng)電路。SR觸發(fā)器用于消除數(shù)字電路中開關(guān)的機(jī)械彈跳。

機(jī)械彈跳

機(jī)械開關(guān)在按下或釋放時(shí)通常需要一些時(shí)間并振動(dòng)幾次才能穩(wěn)定下來,開關(guān)的這種非理想行為稱為開關(guān)彈跳或機(jī)械彈跳。這種機(jī)械彈跳往往會(huì)在低電壓和高電壓之間波動(dòng),這可以通過數(shù)字電路來解釋。

這可能會(huì)導(dǎo)致脈沖信號(hào)的變化,而這些不需要的脈沖系列將導(dǎo)致數(shù)字系統(tǒng)無法正常工作。

例如,在信號(hào)的這個(gè)反彈周期中,輸出電壓的波動(dòng)非常大,因此寄存器計(jì)數(shù)多個(gè)輸入而不是單個(gè)輸入。為了消除數(shù)字電路的這種行為,使用了開關(guān)去抖電路,在這種情況下,使用了SR觸發(fā)器。

SR觸發(fā)器如何消除機(jī)械彈跳?

根據(jù)當(dāng)前狀態(tài)輸出,如果按下置位或復(fù)位按鈕,則輸出將以計(jì)數(shù)多個(gè)信號(hào)輸入的方式發(fā)生變化,即電路可能會(huì)接收到一些不需要的脈沖信號(hào),因此由于機(jī)械彈跳作用機(jī)器,Q的輸出沒有變化。

按下按鈕時(shí),觸點(diǎn)將影響觸發(fā)器的輸入,并且當(dāng)前狀態(tài)將發(fā)生變化,并且不會(huì)對(duì)任何其他機(jī)械開關(guān)彈跳對(duì)電路/機(jī)器產(chǎn)生進(jìn)一步影響。如果開關(guān)有任何額外的輸入,則不會(huì)發(fā)生變化,并且SR觸發(fā)器將在一小段時(shí)間后復(fù)位。

因此,只有在SR觸發(fā)器執(zhí)行狀態(tài)更改后,即僅在接收到單個(gè)時(shí)鐘脈沖信號(hào)后,才能使用相同的開關(guān)。

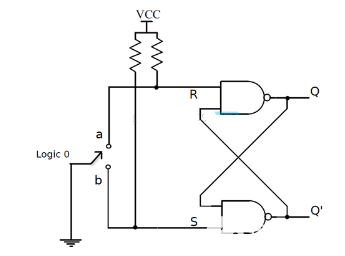

開關(guān)去抖電路的電路如下所示:

開關(guān)的輸入接地(邏輯0),有兩個(gè)上拉電阻連接到每個(gè)輸入。它們確保當(dāng)開關(guān)在觸點(diǎn)之間時(shí)觸發(fā)器輸入S和R始終為1。

另一個(gè)電路可以用NOR SR觸發(fā)器構(gòu)成,如下圖所示:

開關(guān)的輸入連接到邏輯1,有兩個(gè)下拉電阻連接到每個(gè)輸入。它們確保當(dāng)開關(guān)位于觸點(diǎn)a和b之間時(shí),觸發(fā)器輸入S和R始終為0。

用于消除機(jī)械開關(guān)抖動(dòng)的常用IC是MAX6816 – 單輸入、MAX6817 – 雙輸入、MAX6818 – 八輸入開關(guān)去抖動(dòng) IC。這些IC包含帶有SR觸發(fā)器的必要配置。

總結(jié)

以上就是關(guān)于SR觸發(fā)器的基本內(nèi)容,主要包括SR觸發(fā)器的工作原理、使用NOR和NAND門的實(shí)現(xiàn)、時(shí)鐘SR觸發(fā)器以及SR觸發(fā)器的重要應(yīng)用。

需要注意的是,術(shù)語“l(fā)atch(鎖存器)”和“flip-flop(觸發(fā)器)”將作為同義詞使用,盡管在技術(shù)上它們略有不同。簡單來說,觸發(fā)器是一個(gè)時(shí)鐘控制的鎖存器,即只有在有時(shí)鐘信號(hào)(高或低電平,取決于設(shè)計(jì))時(shí),輸出才會(huì)改變。

-

反相器

+關(guān)注

關(guān)注

6文章

316瀏覽量

44109 -

觸發(fā)器

+關(guān)注

關(guān)注

14文章

2034瀏覽量

61968 -

組合邏輯電路

+關(guān)注

關(guān)注

6文章

71瀏覽量

14887

發(fā)布評(píng)論請先 登錄

鎖存器與觸發(fā)器的工作原理是什么

鎖存器和觸發(fā)器原理

CMOS觸發(fā)器的結(jié)構(gòu)與工作原理

JK觸發(fā)器工作原理詳細(xì)介紹

D觸發(fā)器工作原理是什么?

什么是RS觸發(fā)器,RS觸發(fā)器的工作原理是什么?

jk邊沿觸發(fā)器工作原理

主從sr觸發(fā)器基本原理分析

單穩(wěn)態(tài)觸發(fā)器有哪些_單穩(wěn)態(tài)觸發(fā)器工作原理介紹

SR觸發(fā)器的工作原理及應(yīng)用示例

SR觸發(fā)器的工作原理及應(yīng)用示例

評(píng)論