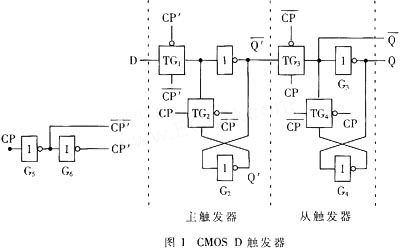

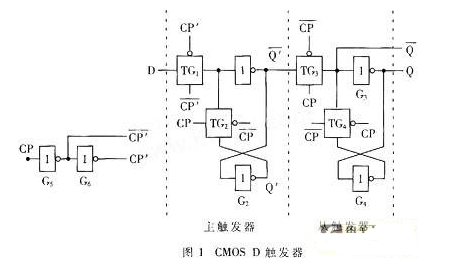

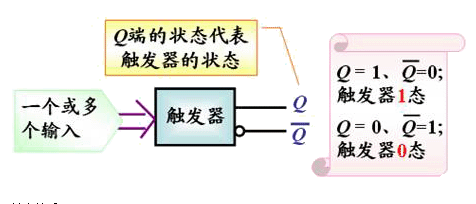

??? CMOS D觸發器足主-從結構形式的一種邊沿觸發器,CMOS T型觸發器、JK觸發器、計數單元、移位單元和各種時序電路都由其組成,因此儀以CMOS D觸發器為例進行說明。

????

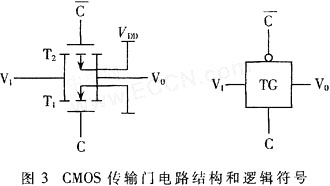

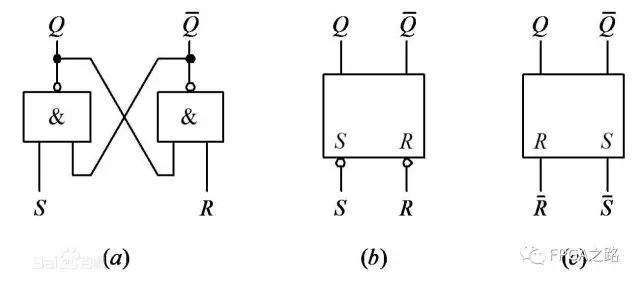

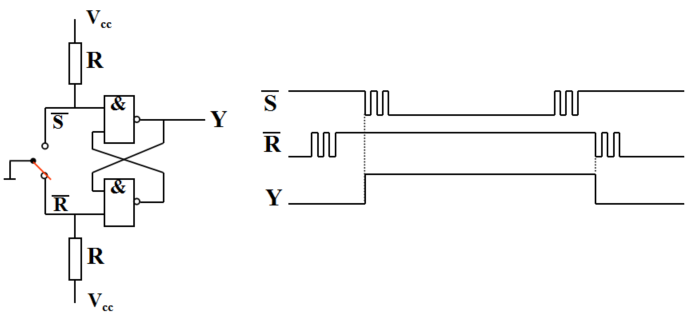

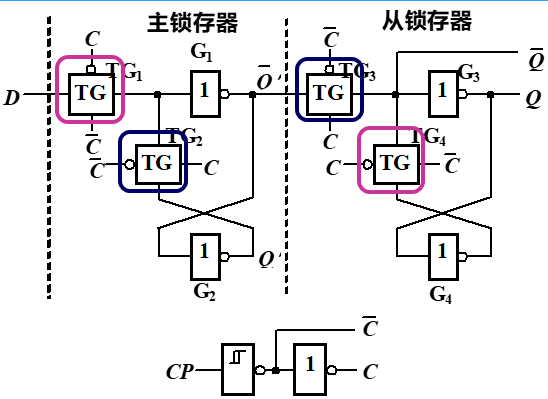

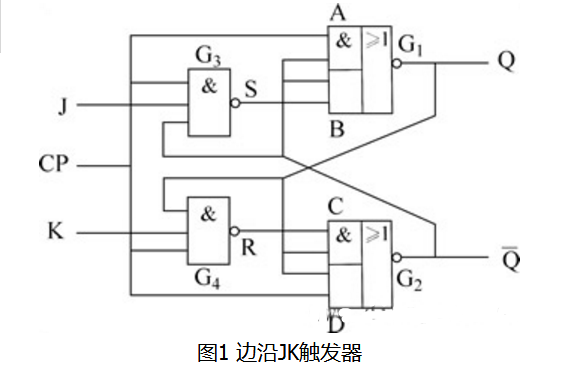

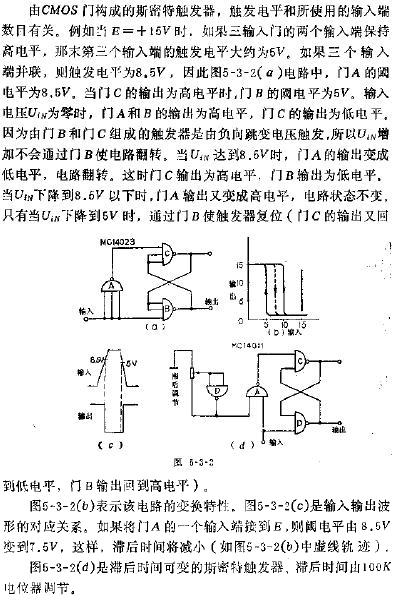

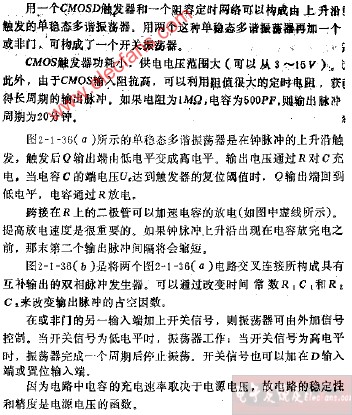

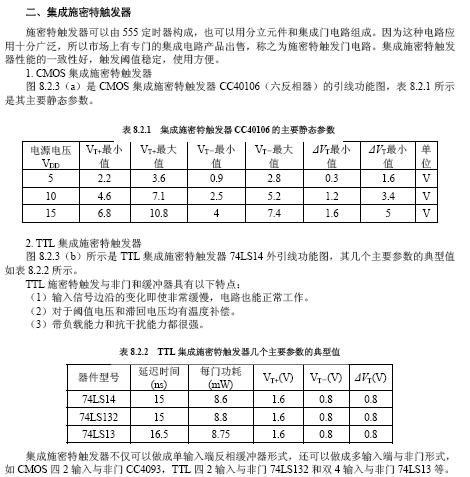

??? 圖1是用CMOS傳輸門和反相器構成的D觸發器,反相器G1、G2和傳輸門TG1、TG2組成了主觸發器,反相器G3、G4和傳輸門TG3、TG4組成了從觸發器。TG1和TG3分別為主觸發器和從觸發器的輸入控制門。反相器G5、G6對時鐘輸入信號CP進行反相及緩沖,其輸出CP和CP′作為傳輸門的控制信號。根據CMOS傳輸門的工作原理和圖中控制信號的極性標注可知,當傳輸門TG1、TG4導通時,TG2、TG3截止;反之,當TG1、TG4截止時,TG2、TG3導通。

????

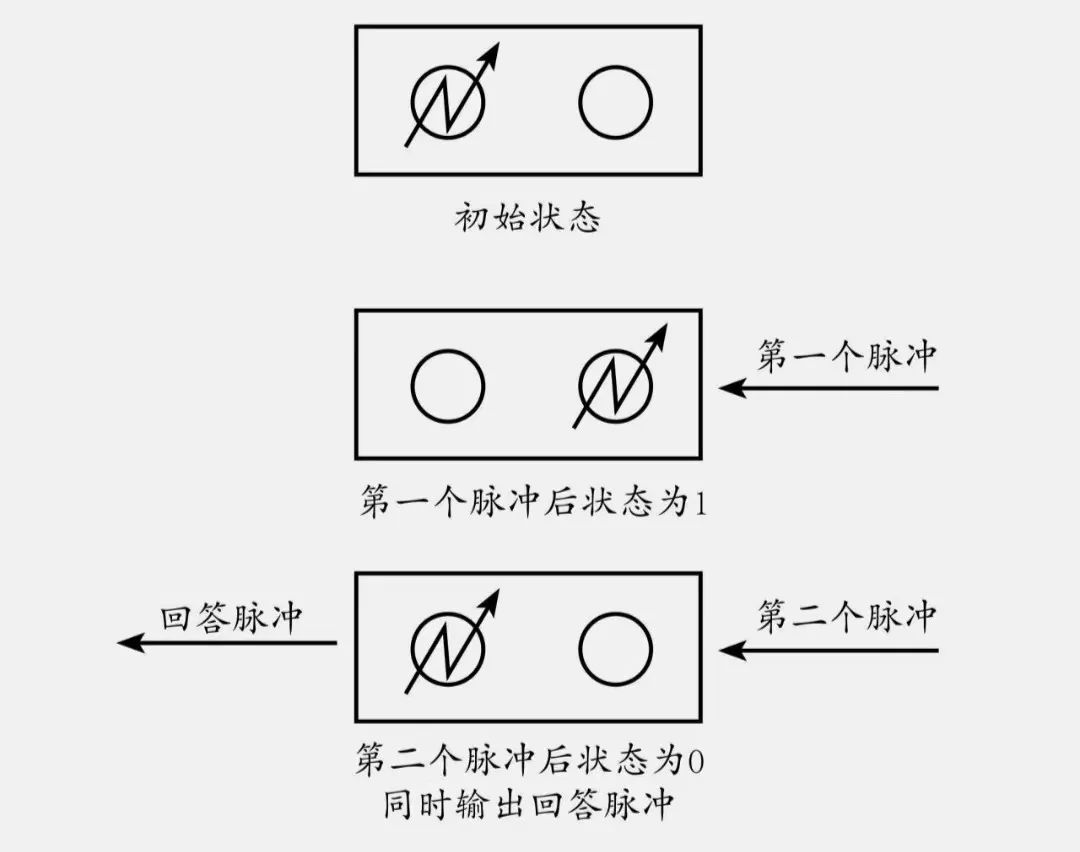

??? 當CP′=0,CP′=1時,TG1導通,TG2截止,D端輸入信號送人主觸發器中,使Q′=D,Q′=D,但這時主觸發器尚未形成反饋連接,不能自行保持。Q′、Q′跟隨D端的狀態變化;同時,由于TG3截止,TG4導通,所以從觸發器形成反饋連接,維持原狀態不變,而且它與主觸發器的聯系被TG3切斷。

??? 當CP′的上升沿到達(即CP′跳變為1,CP′下降為0)時,TG1截止,TG2導通,切斷了D信號的輸入,由于G1的輸入電容存儲效應,G1輸入端電壓不會立即消失,于是Q′、Q′在TG1截止前的狀態被保存下來;同時由于TG3導通、TG4截止,主觸發器的狀態通過TG3和G3送到了輸出端,使Q=Q′=D(CP上升沿到達時D的狀態),而Q=Q′=D。

??? 在CP′=1,CP′=0期間,Q=Q′=D,Q=Q′=D的狀態一直不會改變,直到CP′下降沿到達時(即CP′跳變為0,CP′跳變為1),TG2、TG3又截止,TG1、TG4又導通,主觸發器又開始接收D端新數據,從觸發器維持已轉換后的狀態。

??? 可見,這種觸發器的動作特點是輸出端的狀態轉換發生在CP′的上升沿,而且觸發器所保持的狀態僅僅取決于CP′上升沿到達時的輸入狀態。正因為觸發器輸出端狀態的轉換發生在CP′的上升沿(即CP的上升沿),所以這是一個CP上升沿觸發的邊沿觸發器,CP上升沿為有效觸發沿,或稱CP上升沿為有效沿(下降沿為無效沿)。若將四個傳輸門的控制信號CP′和CP′極性都換成相反的狀態,則CP下降沿為有效沿,而上升沿為無效沿。下面以CP上升沿為有效觸發沿進行分析。

???

電子發燒友App

電子發燒友App

評論