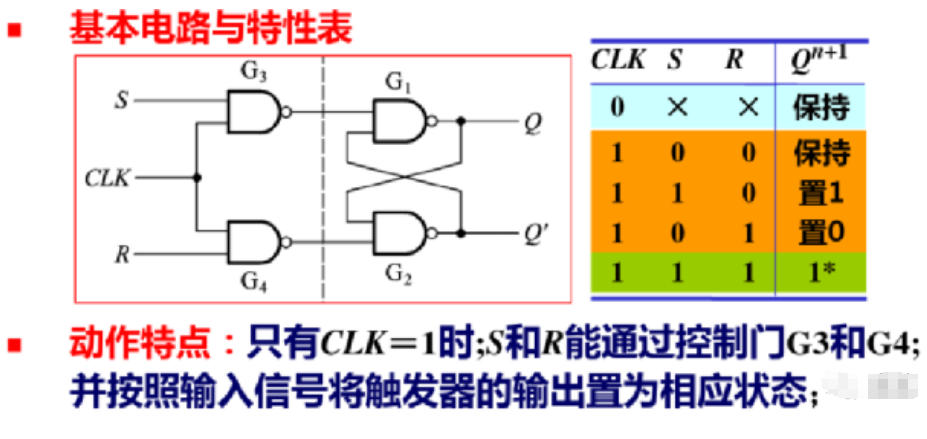

在實(shí)際的數(shù)字系統(tǒng)中往往包含大量的存儲(chǔ)單元,而且經(jīng)常要求他們?cè)谕粫r(shí)刻同步動(dòng)作,為達(dá)到這個(gè)目的,在每個(gè)存儲(chǔ)單元電路上引入一個(gè)時(shí)鐘脈沖(CLK)作為控制信號(hào),只有當(dāng)CLK到來(lái)時(shí)電路才被“觸發(fā)”而動(dòng)作,并根據(jù)輸入信號(hào)改變輸出狀態(tài)。把這種在時(shí)鐘信號(hào)觸發(fā)時(shí)才能動(dòng)作的存儲(chǔ)單元電路稱為觸發(fā)器,以區(qū)別沒有時(shí)鐘信號(hào)控制的鎖存器。

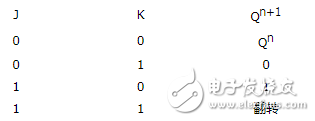

jk觸發(fā)器功能描述

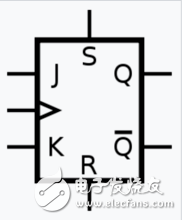

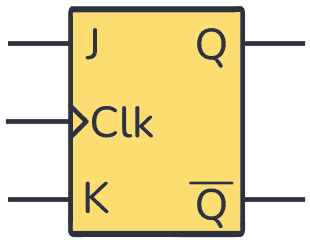

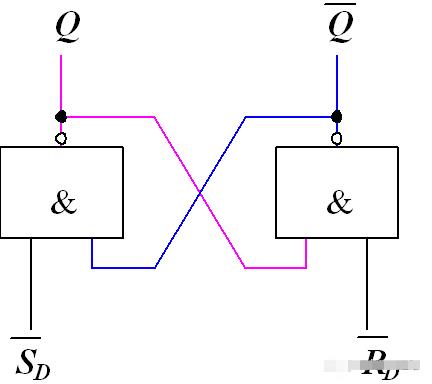

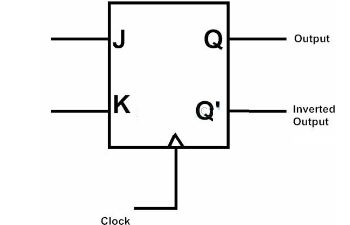

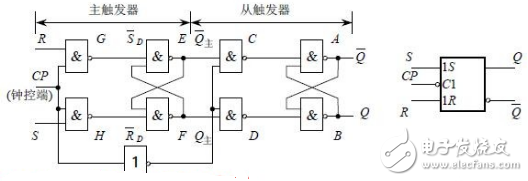

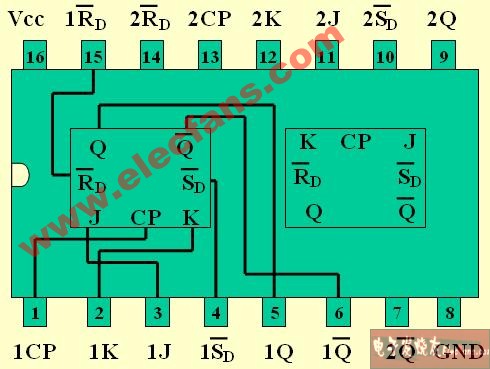

JK觸發(fā)器邏輯簡(jiǎn)圖如下圖所示

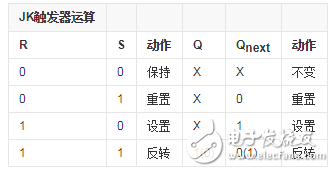

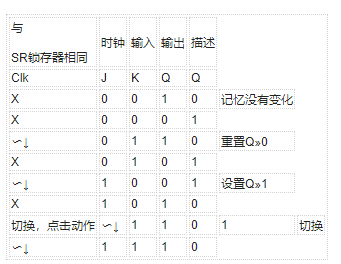

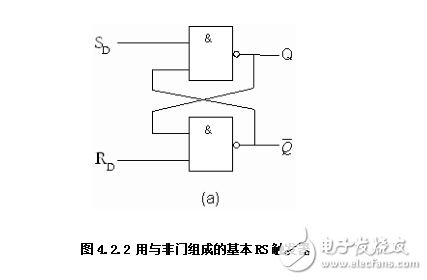

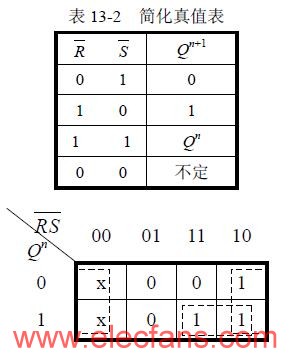

JK觸發(fā)器和觸發(fā)器中最基本的RS觸發(fā)器結(jié)構(gòu)相似,其區(qū)別在于,RS觸發(fā)器不允許R與S同時(shí)為1,而JK觸發(fā)器允許J與K同時(shí)為1。當(dāng)J與K同時(shí)變?yōu)?的同時(shí),輸出的值狀態(tài)會(huì)反轉(zhuǎn)。也就是說(shuō),原來(lái)是0的話,變成1;原來(lái)是1的話,變成0。對(duì)應(yīng)表如下:

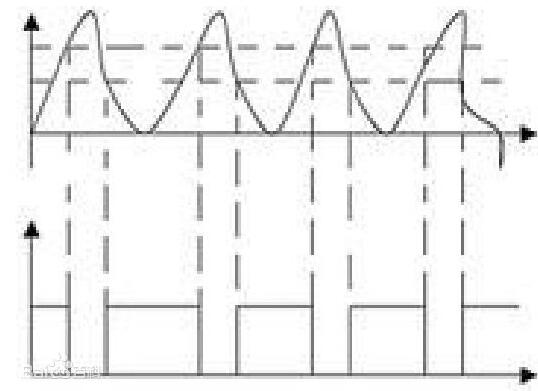

主從JK觸發(fā)器工作特性

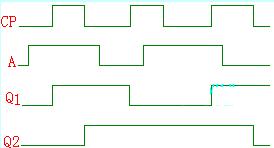

建立時(shí)間:是指輸入信號(hào)應(yīng)先于CP信號(hào)到達(dá)的時(shí)間,用tset表示。J、K信號(hào)只要不遲于CP信號(hào)到達(dá)即可,因此有tset=0。

保持時(shí)間:為保證觸發(fā)器可靠翻轉(zhuǎn),輸入信號(hào)需要保持一定的時(shí)間。保持時(shí)間用tH表示。如果要求CP=1期間J、K的狀態(tài)保持不變,而CP=1的時(shí)間為tWH,則應(yīng)滿足:tH≥tWH。

傳輸延遲時(shí)間:若將從CP下降沿開始到輸出端新狀態(tài)穩(wěn)定地建立起來(lái)的這段時(shí)間定義為傳輸時(shí)間,則有:tPLH=3tpdtPHL=4tpd最高時(shí)鐘頻率:因?yàn)橹鲝挠|發(fā)器都是由兩個(gè)同步RS觸發(fā)器組成的,所以由同步RS觸發(fā)器的動(dòng)態(tài)特性可知,為保證主觸發(fā)器的可靠翻轉(zhuǎn),CP高電平的持續(xù)時(shí)間tWH應(yīng)大于3tpd。同理,為保證從觸發(fā)器能可靠地翻轉(zhuǎn),CP低電平的持續(xù)時(shí)間tWL也應(yīng)大于3tpd。因此,時(shí)鐘信號(hào)的最小周期為:Tc(min)≥6tpd最高時(shí)鐘頻率fc(max)≤1/6tpd。

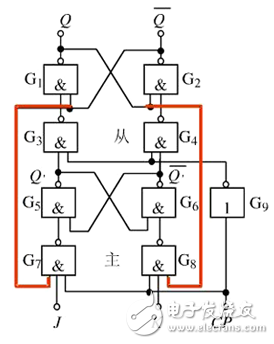

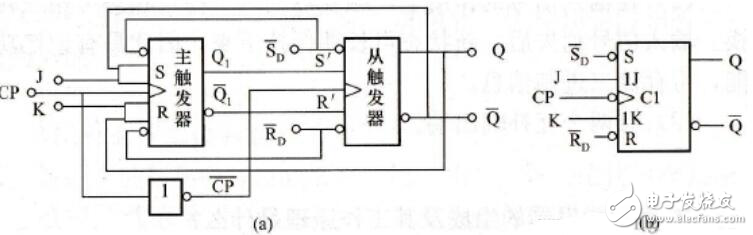

主從JK觸發(fā)器電路圖

主從JK觸發(fā)器特點(diǎn)

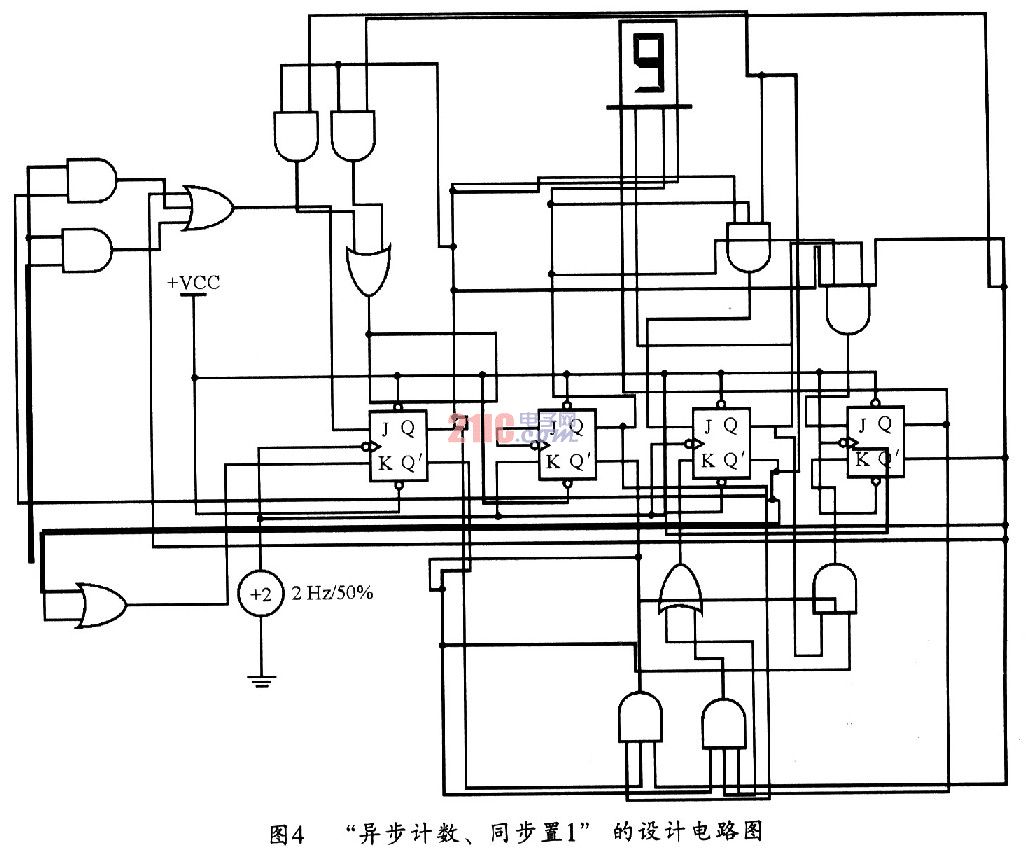

1.主從JK觸發(fā)器具有置位、復(fù)位、保持(記憶)和計(jì)數(shù)功能;

2.主從JK觸發(fā)器屬于脈沖觸發(fā)方式,觸發(fā)翻轉(zhuǎn)只在時(shí)鐘脈沖的負(fù)跳變沿發(fā)生;

3.不存在約束條件,但存在一次變化現(xiàn)象。

4.產(chǎn)生一次變化的原因是因?yàn)樵贑P=1期間,主觸發(fā)器一直在接收數(shù)據(jù),但主觸發(fā)器在某些條件下(Q=0,CP=1期間J端出現(xiàn)正跳沿干擾或Q=1,CP=1期間K端出現(xiàn)正跳沿干擾),不能完全隨輸入信號(hào)的變化而發(fā)生相應(yīng)的變化,以至影響從觸發(fā)器 狀態(tài)與輸入信號(hào)的不對(duì)應(yīng)。

電子發(fā)燒友App

電子發(fā)燒友App

評(píng)論