D觸發(fā)器,是時(shí)序邏輯電路中必備的一個(gè)基本單元,學(xué)好 D 觸發(fā)器,是學(xué)好時(shí)序邏輯電路的前提條件,其重要性不亞于加法器,二者共同構(gòu)成數(shù)字電路組合、時(shí)序邏輯的基礎(chǔ)。

2023-10-09 17:26:57 234

234

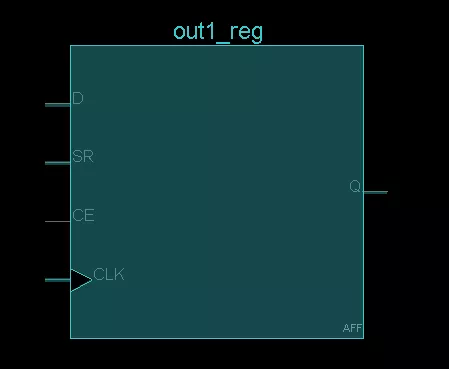

的存儲(chǔ)單元,具有時(shí)鐘同步的特性。其中,D觸發(fā)器是數(shù)字電路設(shè)計(jì)中使用最廣泛的一種觸發(fā)器類型之一,因?yàn)樗哂泻?jiǎn)單、穩(wěn)定和多功能等優(yōu)點(diǎn)。

2023-08-31 10:50:19 1436

1436

D觸發(fā)器組成音頻信號(hào)發(fā)生器? D觸發(fā)器是一種數(shù)字邏輯電路元件,它是由若干個(gè)邏輯門(mén)組成的,常用于數(shù)字系統(tǒng)中的寄存器、計(jì)數(shù)器等。D觸發(fā)器在數(shù)字系統(tǒng)中起到很重要的作用,它能夠存儲(chǔ)和傳輸數(shù)字信號(hào),并且能

2023-08-24 15:50:29 160

160 用D觸發(fā)器設(shè)計(jì)一個(gè)序列發(fā)生器 怎么用D觸發(fā)器做序列信號(hào)發(fā)生器? 序列發(fā)生器是數(shù)字電子技術(shù)中常用的電路模塊之一,它可以用來(lái)生成一系列的數(shù)字信號(hào)序列。在數(shù)字電路中,D觸發(fā)器是一種被廣泛使用的數(shù)字邏輯組件

2023-08-24 15:50:17 549

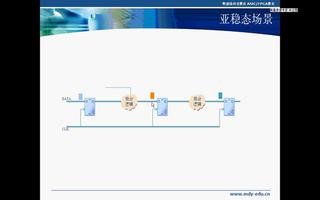

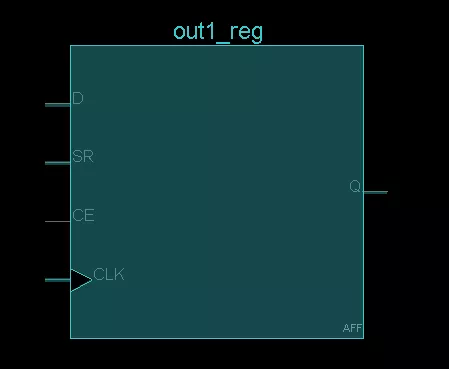

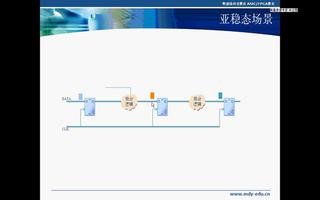

549 本系列整理數(shù)字系統(tǒng)設(shè)計(jì)的相關(guān)知識(shí)體系架構(gòu),為了方便后續(xù)自己查閱與求職準(zhǔn)備。對(duì)于FPGA和ASIC設(shè)計(jì)中,D觸發(fā)器是最常用的器件,也可以說(shuō)是時(shí)序邏輯的核心,本文根據(jù)個(gè)人的思考?xì)v程結(jié)合相關(guān)書(shū)籍內(nèi)容和網(wǎng)上文章,聊一聊D觸發(fā)器與亞穩(wěn)態(tài)的那些事。

2023-07-25 10:45:39 274

274

鎖存器和觸發(fā)器有時(shí)組合在一起,因?yàn)樗鼈兌伎梢栽谄漭敵錾洗鎯?chǔ)一位(1或0)。與鎖存器相比,觸發(fā)器是需要時(shí)鐘信號(hào)(Clk)的同步電路。D 觸發(fā)器僅在時(shí)鐘從

2023-06-29 11:50:18 5258

5258

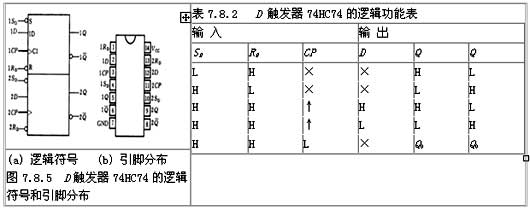

本文旨在總結(jié)近期復(fù)習(xí)的數(shù)字電路D觸發(fā)器(邊沿觸發(fā))的內(nèi)容。

2023-05-22 16:54:29 3707

3707

本系列整理數(shù)字系統(tǒng)設(shè)計(jì)的相關(guān)知識(shí)體系架構(gòu),為了方便后續(xù)自己查閱與求職準(zhǔn)備。對(duì)于FPGA和ASIC設(shè)計(jì)中,D觸發(fā)器是最常用的器件,也可以說(shuō)是時(shí)序邏輯的核心,本文根據(jù)個(gè)人的思考?xì)v程結(jié)合相關(guān)書(shū)籍內(nèi)容和網(wǎng)上文章,聊一聊D觸發(fā)器與亞穩(wěn)態(tài)的那些事。

2023-05-12 16:37:31 975

975

本帖最后由 gk320830 于 2015-3-5 20:47 編輯

如何用JK觸發(fā)器構(gòu)成D觸發(fā)器 電路圖來(lái)人給個(gè)圖吧..

2011-11-14 15:21:03

最近在用LTspice仿真D觸發(fā)器的一個(gè)串并輸入功能,只有第一個(gè)觸發(fā)器的波形跟理論分析一致,其他剩余的就是怎么也不行。 經(jīng)過(guò)資料查找,和不停地嘗試,最終還是找出了原因。 確實(shí)每一個(gè)工具還是有其特點(diǎn)的,跟實(shí)際的芯片還是有差異。

2023-01-19 17:28:00 1872

1872

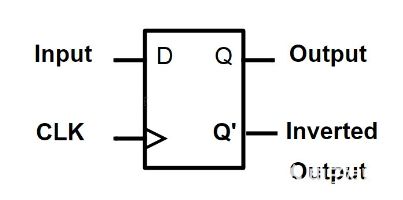

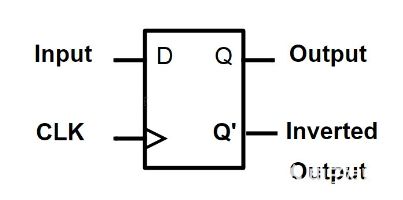

D 觸發(fā)器或數(shù)據(jù)觸發(fā)器是一種觸發(fā)器,它只有一個(gè)數(shù)據(jù)輸入“D”和一個(gè)時(shí)鐘脈沖輸入, 這種觸發(fā)器也稱為延遲觸發(fā)器,經(jīng)常用于許多時(shí)序電路,如寄存器、計(jì)數(shù)器等。下面一起來(lái)了解一下D觸發(fā)器不同應(yīng)用下的電路圖。

2023-01-06 14:19:46 1874

1874 D觸發(fā)器也稱為“延遲觸發(fā)器”或“數(shù)據(jù)觸發(fā)器”,主要用于存儲(chǔ)1位二進(jìn)制數(shù)據(jù),是數(shù)字電子產(chǎn)品中廣泛使用的觸發(fā)器之一。除了作為數(shù)字系統(tǒng)中的基本存儲(chǔ)元件外,D觸發(fā)器也被視為延遲線元件和零階保持元件。

2022-10-11 17:21:02 97371

97371

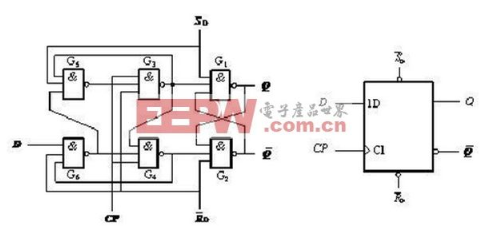

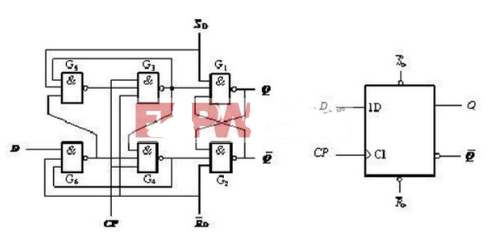

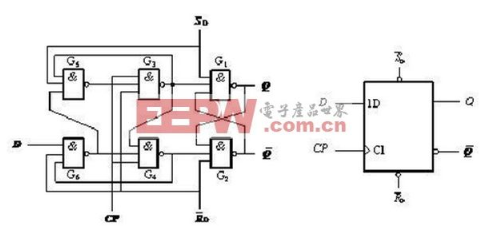

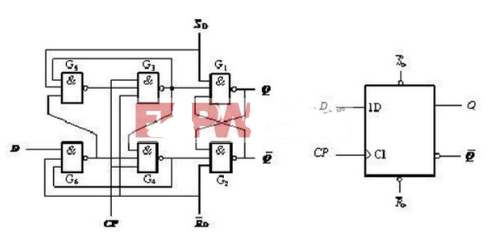

上圖是用與非門(mén)實(shí)現(xiàn)的D觸發(fā)器的邏輯結(jié)構(gòu)圖,CP是時(shí)鐘信號(hào)輸入端,S和R分別是置位和清零信號(hào),低有效; D是信號(hào)輸入端,Q信號(hào)輸出端;

2022-09-19 15:22:24 3240

3240 今天我們來(lái)研究一下D觸發(fā)器都有哪幾種類型?又對(duì)應(yīng)什么樣的代碼?

2022-08-02 09:07:49 3454

3454

明德?lián)P有完整的時(shí)序約束課程與理論,接下來(lái)我們會(huì)一章一章以圖文結(jié)合的形式與大家分享時(shí)序約束的知識(shí)。要掌握FPGA時(shí)序約束,了解D觸發(fā)器以及FPGA運(yùn)行原理是必備的前提。今天第一章,我們就從D觸發(fā)器開(kāi)始講起。

2022-07-11 11:33:10 2327

2327

D觸發(fā)器在FPGA里用得很多,但我經(jīng)常無(wú)法理解D觸發(fā)器為什么能對(duì)數(shù)據(jù)延遲一個(gè)時(shí)鐘周期(打一拍)。下面從信號(hào)處理的角度來(lái)談一下我的理解。如發(fā)現(xiàn)理解有誤,煩請(qǐng)留言指正。

2022-06-17 16:56:19 4177

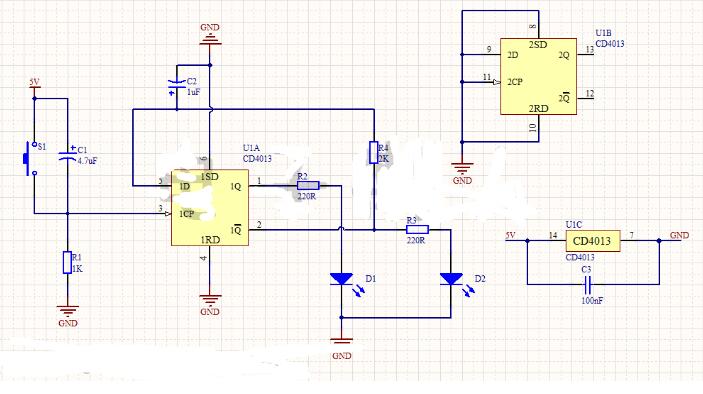

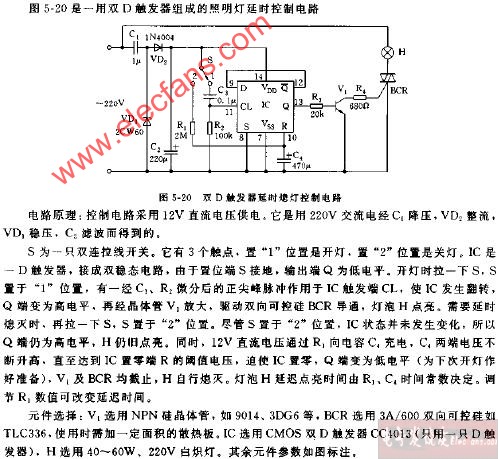

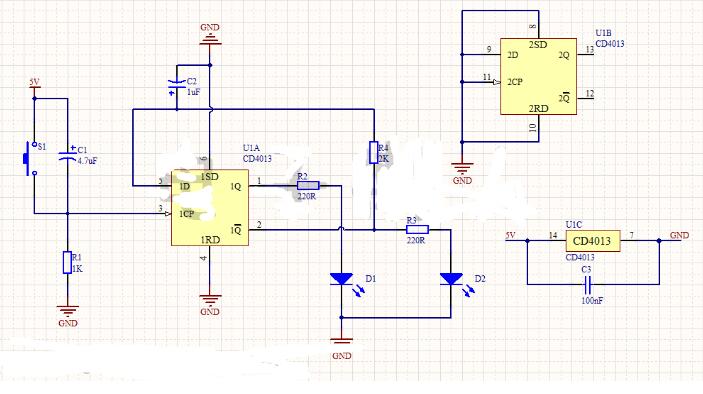

4177 CD4013或74LS74雙D觸發(fā)器的應(yīng)用實(shí)驗(yàn)

2022-05-11 17:11:19 128

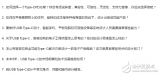

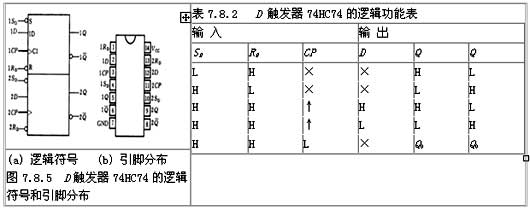

128 74LS74內(nèi)含兩個(gè)獨(dú)立的D上升沿雙d觸發(fā)器,每個(gè)觸發(fā)器有數(shù)據(jù)輸入(D)、置位輸入( )復(fù)位輸入( )、時(shí)鐘輸入(CP)和數(shù)據(jù)輸出(Q)。 的低電平使輸出預(yù)置或清除,而與其它輸入端的電平無(wú)關(guān)。當(dāng)

2021-06-04 15:40:41 63776

63776

在分析維持-阻塞邊沿D觸發(fā)器的工作原理之前,讓我們先來(lái)看看 R0的復(fù)位功能 、S0的置位功能是如何實(shí)現(xiàn)的吧。

2020-10-18 11:26:31 19272

19272

本文檔的主要內(nèi)容詳細(xì)介紹的是Multisim仿真實(shí)例D觸發(fā)器的研究原理圖免費(fèi)下載。

2020-04-28 14:55:00 44

44 D觸發(fā)器是一個(gè)具有記憶功能的,具有兩個(gè)穩(wěn)定狀態(tài)的信息存儲(chǔ)器件,是構(gòu)成多種時(shí)序電路的最基本邏輯單元,也是數(shù)字邏輯電路中一種重要的單元電路。

2019-12-02 07:06:00 6002

6002

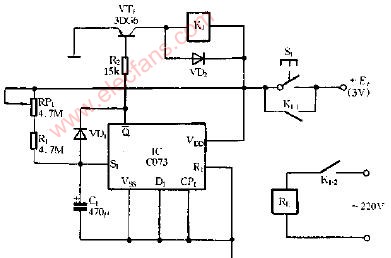

所謂自鎖開(kāi)關(guān)就是按一下,開(kāi)關(guān)接通并保持接通狀態(tài);再按一下,開(kāi)關(guān)解鎖復(fù)位到初始狀態(tài)。本例通過(guò)D觸發(fā)器而設(shè)計(jì)的電子自鎖開(kāi)關(guān),當(dāng)每按一下電路中的輕觸按鍵S1時(shí),都可以使D觸發(fā)器翻轉(zhuǎn)一次,同時(shí)利用CD4013的特性,按鍵松開(kāi)后電路仍然保持自鎖狀態(tài)。

2019-10-01 11:03:00 16749

16749

負(fù)跳沿觸發(fā)的主從觸發(fā)器工作時(shí),必須在正跳沿前加入輸入信號(hào)。如果在CP 高電平期間輸入端出現(xiàn)干擾信號(hào),那么就有可能使觸發(fā)器的狀態(tài)出錯(cuò)。而邊沿觸發(fā)器允許在CP 觸發(fā)沿來(lái)到前一瞬間加入輸入信號(hào)。這樣,輸入端受干擾的時(shí)間大大縮短,受干擾的可能性就降低了。邊沿D觸發(fā)器也稱為維持-阻塞邊沿D觸發(fā)器。

2019-07-12 08:50:36 94674

94674

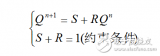

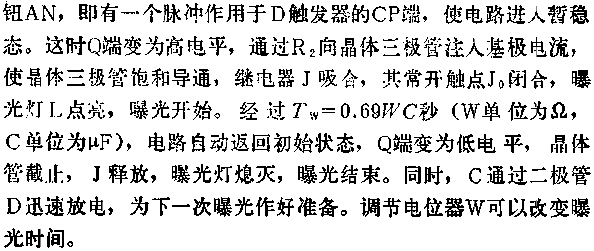

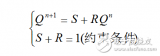

現(xiàn)在介紹一種用D觸發(fā)器制作的該類裝置,制作簡(jiǎn)單經(jīng)濟(jì),效果較好。

2019-02-16 10:48:01 3169

3169

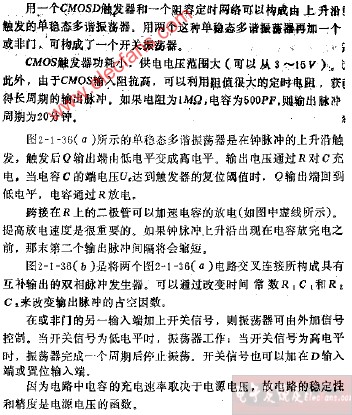

關(guān)鍵詞:D觸發(fā)器 , VCO 如圖所示為雙D觸發(fā)器式的VCO。電路輸出一個(gè)占空比50%的方波信號(hào),而消耗的電流卻很小。當(dāng)輸入電壓為5~12V時(shí),輸出頻率范圍從20~70kHz。首先假設(shè)IC-A的初始

2018-10-08 09:27:01 140

140 D觸發(fā)器(data flip-flop或delay flip-flop)由6個(gè)與非門(mén)組成,其中G1和G2構(gòu)成基本RS觸發(fā)器。電平觸發(fā)的主從觸發(fā)器工作時(shí),必須在正跳沿前加入輸入信號(hào)。如果在CP高電平期間輸入端出現(xiàn)干擾信號(hào),那么就有可能使觸發(fā)器的狀態(tài)出錯(cuò)。

2017-11-02 09:59:08 95590

95590

請(qǐng)高手指點(diǎn)下有啥問(wèn)題,D觸發(fā)器開(kāi)關(guān)電路

2017-01-14 01:30:04 25

25 用一對(duì)互補(bǔ)的輸入信號(hào)送入RS 觸發(fā)器,就得到單輸入的 D 觸發(fā)器。由于D 觸發(fā)器有一對(duì)互補(bǔ)信號(hào)接至RS 觸發(fā)器的 輸入端,所以它避免了RS 輸入端同時(shí)為1 的不允許工作狀 態(tài)。D 觸發(fā)器通常用來(lái)暫時(shí)存儲(chǔ)一個(gè)比特的信息或用作時(shí)延 器件。當(dāng)CLOCK=1 時(shí),觸發(fā)器能把輸

2011-03-09 16:20:01 92

92 D觸發(fā)器的常規(guī)使用一般是用作二分頻器、計(jì)數(shù)器或移位寄存器。然而,只要對(duì)D觸發(fā)器的外圍電路加以改進(jìn),根據(jù)其基本邏輯功能。就可充分發(fā)揮其獨(dú)特的作用。數(shù)

2010-12-29 11:44:46 2899

2899

圖中所示是用J-K觸發(fā)器組成的D觸發(fā)器電路。

從J-K觸發(fā)器的邏輯圖已知在D觸發(fā)器端增

2010-09-24 00:21:27 5729

5729

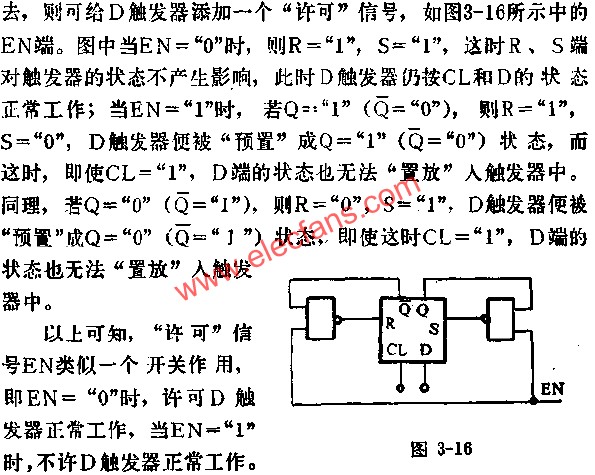

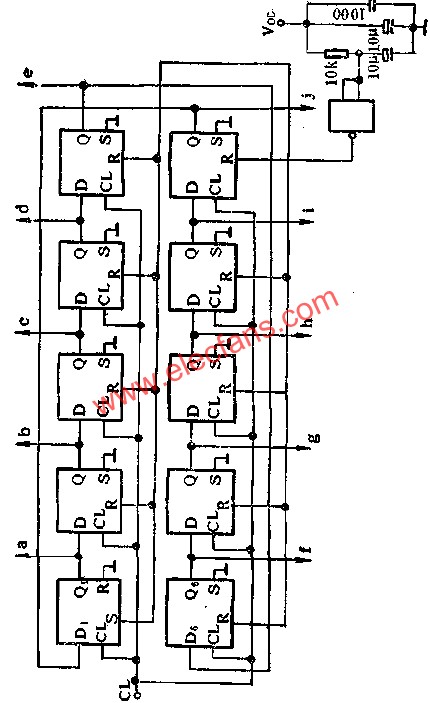

圖中是用D觸發(fā)器組成的曝光定時(shí)器電路。曝光時(shí)間可在1秒至30秒內(nèi)任意選擇。

2010-09-23 23:53:40 757

757

圖中所示是用CMOS四鎖定D觸發(fā)器組成的四選一判別電路。

四選一判別電路即那個(gè)信號(hào)

2010-09-21 01:59:27 3192

3192

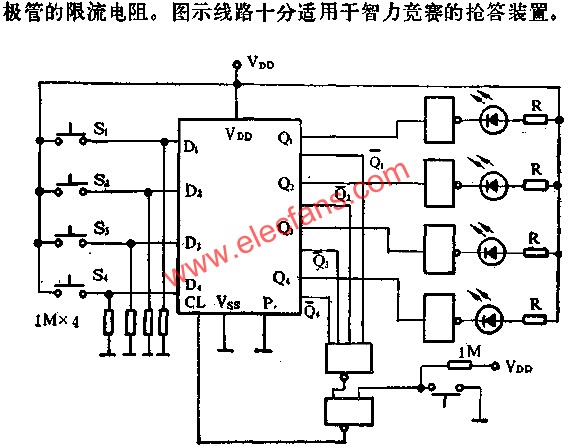

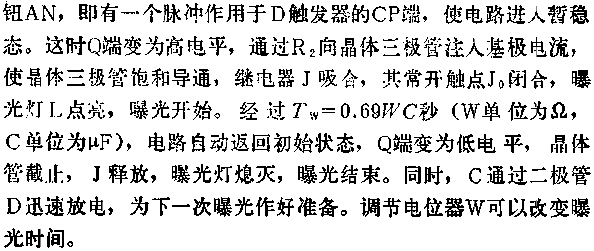

從D觸發(fā)器的真值表可知,當(dāng)時(shí)鐘脈沖CL="1"時(shí),數(shù)據(jù)輸入端D的狀態(tài)會(huì)被“置放”入觸發(fā)器中去,而與觸發(fā)器原狀無(wú)關(guān)。如果當(dāng)時(shí)鐘沖CL="1",D端狀態(tài)不旋轉(zhuǎn)放入

2010-09-21 01:27:59 577

577

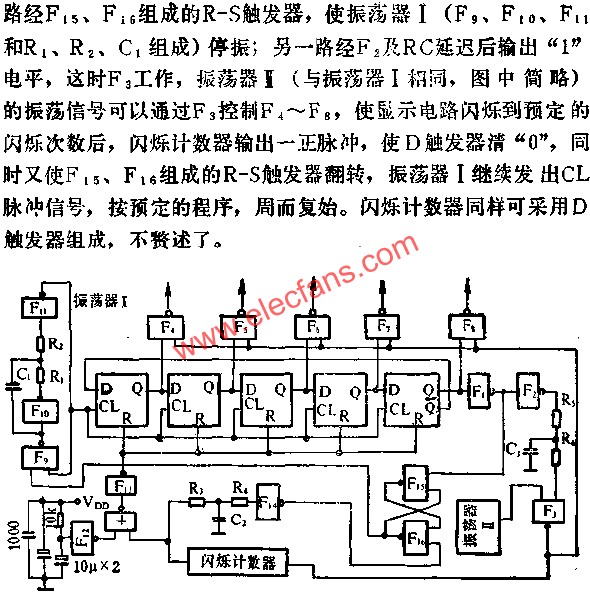

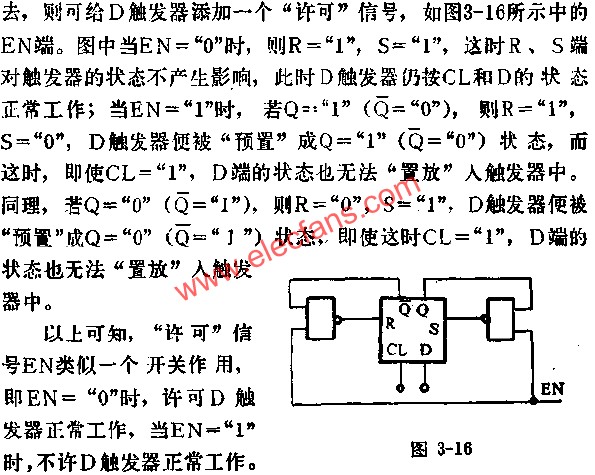

遞增顯示也是將靜態(tài)顯示變?yōu)閯?dòng)態(tài)顯示,它和交替式不同的是逐級(jí)遞增。圖中所示是用CMOS電路D觸發(fā)器組成的

2010-09-21 01:00:59 902

902

交替顯示就是將靜態(tài)顯示變?yōu)閯?dòng)態(tài)顯示,圖中所示是用CMOS電路D觸發(fā)器組成的交替顯示的控制電路。

2010-09-21 00:50:29 1130

1130

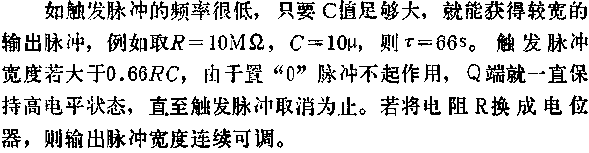

圖中所示是用CMOS電路D觸發(fā)器組成的單穩(wěn)態(tài)多諧振蕩器.因?yàn)?b style="color: red">D觸發(fā)器除了具有傳送D端數(shù)據(jù)的功能外,還具

2010-09-21 00:08:57 3792

3792

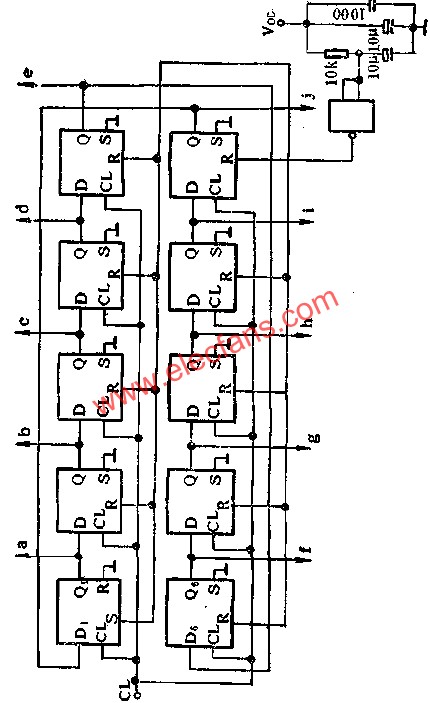

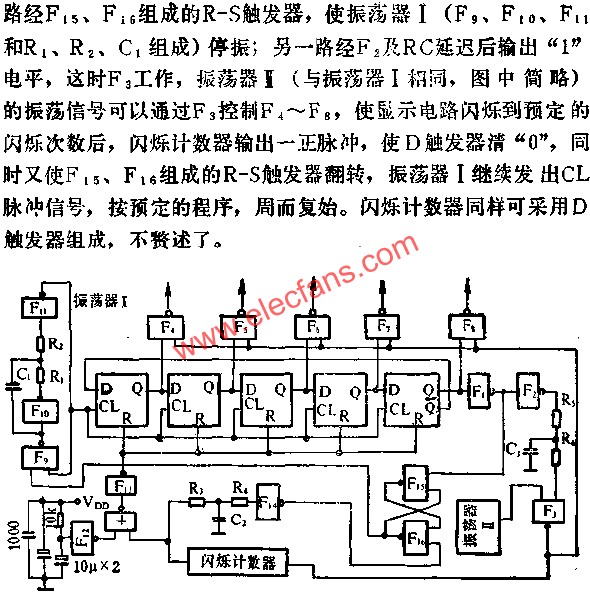

圖中所示是用CMOS電路D觸發(fā)器組成的十進(jìn)制環(huán)形計(jì)數(shù)器.圖中先將D觸發(fā)器拼成移位寄存器,然后把最后一級(jí)D觸發(fā)器

2010-09-20 23:46:58 17359

17359

如果連接N個(gè)D觸發(fā)器,則組成N位移位寄

2010-09-20 04:48:02 9137

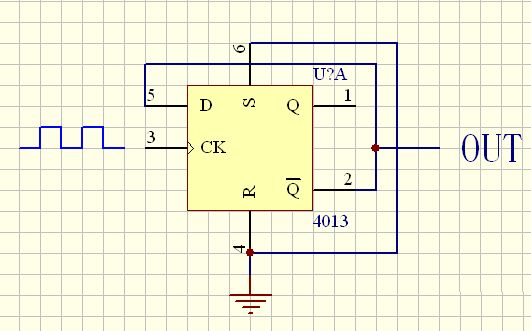

9137 上例圖中A將D觸發(fā)器的D端和Q相連,即可組成二分頻電路,如果把三個(gè)D觸發(fā)器串行相連,如圖所示,則經(jīng)過(guò)一

2010-09-20 03:40:48 11549

11549 圖中所示是用CMOS電路D觸發(fā)器組成T型觸發(fā)器和J-K觸發(fā)器線路。圖示線路將D觸發(fā)器的Q端與D端相連,就可組成T

2010-09-20 03:31:35 15895

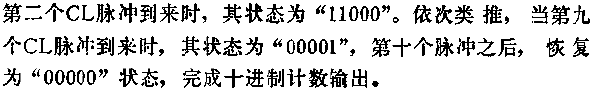

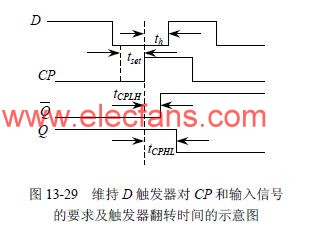

15895 根據(jù)前面分析可知,維持阻塞D觸發(fā)器的工作分兩個(gè)階段,在CP=0時(shí),為準(zhǔn)備階段;CP由0向1正向跳變時(shí)刻為狀態(tài)轉(zhuǎn)移階段。為了使維持阻塞D觸發(fā)器(見(jiàn)圖13-22)能可靠

2010-08-23 09:31:03 4526

4526

摘 要:通過(guò)對(duì)鐘控神經(jīng)MOS 管特性和冗余抑制技術(shù)的研究,提出了一種新型多值雙邊沿D 觸發(fā)器的設(shè)計(jì)方案.該方案利用鐘控神經(jīng)MOS 管多輸入柵加權(quán)信號(hào)控制、浮柵上的電容耦合

2010-08-12 16:06:26 17

17 D觸發(fā)器工作原理是什么?

邊沿D 觸發(fā)器:

負(fù)跳沿觸發(fā)的主從觸發(fā)器工作時(shí),必須在正跳沿前加入輸入信號(hào)。如果在CP 高電平期間輸入端出

2010-03-08 13:56:50 68940

68940

D觸發(fā)器,D觸發(fā)器是什么意思

邊沿D 觸發(fā)器: 電平觸發(fā)的主從觸發(fā)器工作時(shí),必須在正跳沿前加入輸入信號(hào)。如果在CP 高

2010-03-08 13:53:13 4130

4130 維持阻塞D觸發(fā)器

(a) 邏輯電路 &

2009-09-30 18:23:59 17890

17890

40174 CMOS 六D觸發(fā)器:

2009-08-08 11:32:28 46

46 d觸發(fā)器構(gòu)成2分頻電路

2009-06-22 07:36:33 7322

7322

雙D觸發(fā)器延時(shí)熄燈控制電路圖

2009-06-13 17:11:57 1944

1944

D觸發(fā)器實(shí)現(xiàn)二分頻電路(D觸發(fā)器構(gòu)成的2分頻電路)&

2009-06-12 13:58:56 73460

73460

D觸發(fā)器的制作及電路圖

2009-05-19 09:35:49 33

33

D觸發(fā)器構(gòu)成的定時(shí)電路圖

2009-05-08 15:15:26 3107

3107

D觸發(fā)器電路圖

2009-05-08 14:26:44 3484

3484

用CMOS“D”觸發(fā)器構(gòu)成的脈沖發(fā)生器

2009-03-23 10:19:05 1447

1447

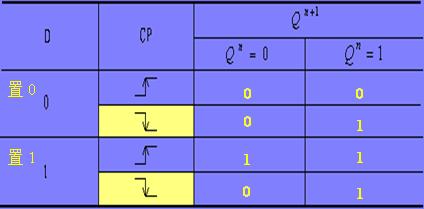

D觸發(fā)器邏輯功能表

同

2009-03-18 20:13:59 43773

43773

D觸發(fā)器的功能測(cè)試74LS74型雙D觸發(fā)器芯片引腳圖,D觸發(fā)器功能測(cè)試的引腳連線圖,D觸發(fā)器功能測(cè)試的引腳連線圖,用D觸發(fā)器構(gòu)成二進(jìn)制計(jì)數(shù)器,用D觸發(fā)器構(gòu)成四位移位寄存器

J-K

2009-02-14 15:27:51 290

290 同步式D觸發(fā)器邏輯電路圖

2008-10-20 09:58:19 7678

7678

d觸發(fā)器芯片有:

74HC74 74LS90? 雙D觸發(fā)器74LS74?

74LS364八D觸發(fā)器(三態(tài))

2008-01-22 12:42:33 43218

43218

cd4013雙d觸發(fā)器

CD4013雙D觸發(fā)器做的脈沖4分頻器應(yīng)用

-----------------------------. ┌─────

2008-01-09 23:48:45 4487

4487 D觸發(fā)器真值表分析:

1. D 觸發(fā)器真值表

Dn

2007-09-11 23:15:20 17600

17600 D觸發(fā)器邊沿D 觸發(fā)器: 負(fù)跳沿觸發(fā)的主從觸發(fā)器工作時(shí),必須在正跳沿前加入輸入信號(hào)。如果在CP 高電平期間輸入端出現(xiàn)干擾信號(hào),那么就有可能使觸發(fā)器的狀態(tài)出錯(cuò)。而邊

2007-09-11 23:13:22 173406

173406

電子發(fā)燒友App

電子發(fā)燒友App

硬聲App

硬聲App

234

234

1436

1436

160

160 549

549 274

274

5258

5258

3707

3707

975

975

1872

1872

1874

1874 97371

97371

3240

3240 3454

3454

2327

2327

4177

4177 128

128 63776

63776

19272

19272

44

44 6002

6002

16749

16749

94674

94674

140

140 95590

95590

25

25 92

92 2899

2899

5729

5729

757

757

577

577

902

902

1130

1130

3792

3792

17359

17359

11549

11549 15895

15895 4526

4526

17

17 68940

68940

4130

4130 73460

73460

290

290 43218

43218

4487

4487 173406

173406

評(píng)論