從D觸發器的角度說明建立和保持時間。

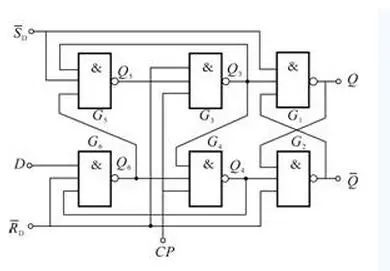

上圖是用與非門實現的D觸發器的邏輯結構圖,CP是時鐘信號輸入端,S和R分別是置位和清零信號,低有效; D是信號輸入端,Q信號輸出端;

這里先說一下D觸發器實現的原理:(假設S和R信號均為高,不進行置位和清零操作)

CP=0時: G3和G4關閉,Q3和Q4輸出為’1’。那么G5和G6打開,Q5=D,Q6=/D。Q5,Q6

的信號隨輸入信號D的改變而變化; G1和G2構成一個SR鎖存器,我們知道,當SR鎖存器的S、R的輸入均為高的時候,鎖存器的輸出保持不變,所以Q和/Q保持不變。

CP從0跳變為1時: G3和G4打開,Q3=Q6=/D,Q4=Q5=D。由SR鎖存器的特性,Q=Q3=D,/Q=/D;CP=1時: 不管D怎么變化,Q3和Q4的信號都不會發生變化,所以輸出也不會改變,具體原因由興趣的可以推一下;下面就又重復CP=0的時刻了。

從上面的分析可以知道,輸入信號D是在CP=0的時刻,經過與G5和G6兩個與非門的延遲Tsu之后才傳輸到Q5和Q6端的,然后再CP跳變為1的時候被鎖存到輸出端的。

我們假設Tsu=5ns,如果D輸入信號在CP跳變為1之前4ns(《5ns)的時候,才發生變化,那么在CP跳變為1時,輸入信號D還沒有傳輸到Q5和Q6,SR鎖存器鎖存的將是D變化之前的數據。也就是說D輸入信號只有在CP跳變之前》Tsu的時間里準備好,觸發器才能將數據鎖存到Q輸出端口,也就是所說的要保證信號的建立時間。

在CP跳變為1之后,Q5和Q6的信號要經過G3和G4兩個與非門的延遲(Thd)才能傳遞到Q3和Q4,構成SR鎖存器之前的D輸入的阻塞,保證在CP=1是輸入數據變化不會影響鎖存結果。

我們假設Thd=5ns,如果D輸入信號在CP跳變為1之后5ns內發生跳變,因為此時Q3和Q4還沒發生變化,均為’1’,Q5和Q6的狀態將會發生跳變。在CP=1的時刻,Q3和Q4跟隨Q5、Q6的改變也發生跳變,末端SR鎖存器的輸出Q也發生跳變,造成輸出結果不對。 也就是說在CP跳變為1之后的Thd時間內,D信號不能發生變化,也就是所說的要保證信號的保持時間(Thd)。

-

FPGA

+關注

關注

1644文章

21993瀏覽量

615316 -

數據

+關注

關注

8文章

7249瀏覽量

91314 -

鎖存器

+關注

關注

8文章

923瀏覽量

42195 -

D觸發器

+關注

關注

3文章

165瀏覽量

48599

原文標題:FPGA學習-從D觸發器的角度說明建立和保持時間

文章出處:【微信號:gh_9d70b445f494,微信公眾號:FPGA設計論壇】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

基于D觸發器實現時鐘電路同步設計

如何實現半個時鐘周期延時

用D觸發器實現2倍分頻的邏輯電路?

數字電路D觸發器怎么實現狀態機

解決方案:Chipscope中抓取的信號名改變,影響數據觀測和分析

怎樣使用D觸發器實現二分頻器

八人搶答器電路的設計的詳細資料免費下載來設計看看吧!內含基本電路

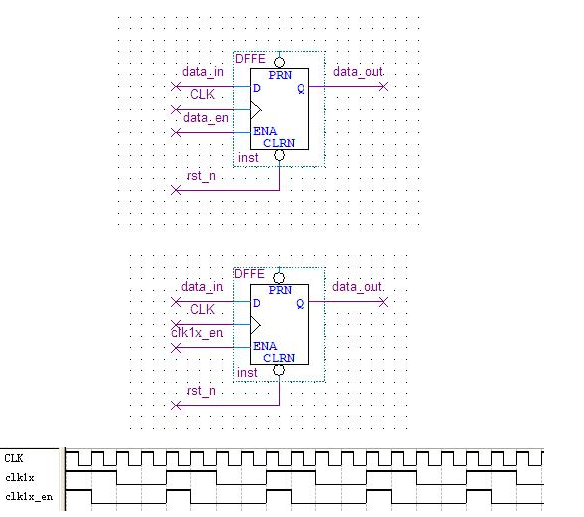

verilog模型舉例:利用D觸發器實現時鐘使能

D觸發器實現的原理

D觸發器實現的原理

評論