取某個信號的上升沿或下降沿信號

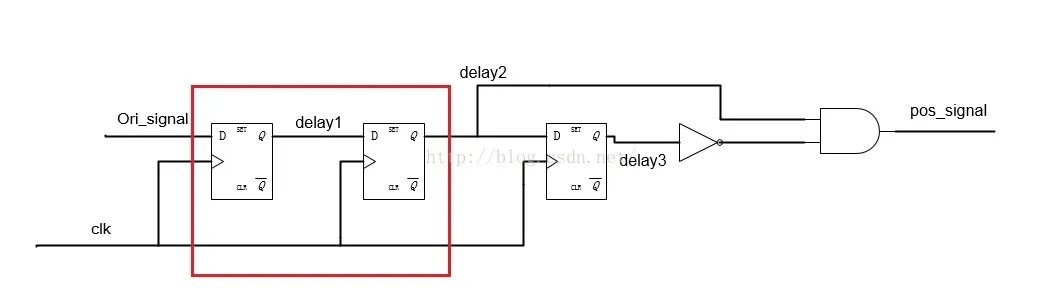

取一個信號的上升沿或下降沿信號,可以通過將信號delay后,然后將原信號和delay信號,通過不同的與非操作,獲取上升沿信號或下降沿信號: 階段一: reg delay; // delay信號 always @ ( posedge clk or negedge rstn ) if( !rstn ) delay <= 0; else delay <= orig;? ?// orig是原信號 wire pos_signal = orig && ( ~delay ); // 原信號上升沿位置處產生的pulse信號 wire neg_signal = ( ~orig ) && delay; // 原信號下降沿位置處產生的pulse信號 階段二: 上述操作會存在亞穩態問題,并且得到的上升沿信號pos_signal和下降沿信號neg_signal無法被原采樣時鐘clk采樣。正確做法是,先將原信號用采樣時鐘delay 2次(打兩拍),得到和采樣時鐘同時鐘域的信號delay2,然后再按上述方法獲取上升沿和下降沿信號,這時得到的上升沿或下降沿就可以被原采樣時鐘采樣。 例句如下: reg ori_signal;// 需取上升沿或下降沿的原信號 reg delay1; reg delay2; always @ ( posedge clk or negedge rstn ) if( !rstn ) delay1 <= 0; else delay1 <= ori_signal;? ? always @ ( posedge clk or negedge rstn ) if( !rstn ) delay2 <= 0; else delay2 <= delay1;? // delay2 已與clk同域 reg delay3; always @ ( posedge clk or negedge rstn ) if( !rstn ) delay3 <= 0; else delay3 <= delay2;? ? wire pos_signal = delay2 && ( ~delay3 ); // 原信號上升沿位置處產生的pulse信號 wire neg_signal = ( ~delay2 ) && delay3; // 原信號下降沿位置處產生的pulse信號 上升沿電路如下: ?

?

?

?注意:前兩個觸發器的運用就是起同步作用,將某個信號同步到采樣時鐘域,以后要重點注意使用。

階段三:

用階段二的語句會比較繁瑣,可以用下述語句簡化:

reg[2:0] delay;

always @ ( posedge clk or negedge rstn )

if( !rstn )

delay <= 0;

else

delay <= { delay[1:0], ori_signal} ; // ori_signal是原信號

wire pos_signal = delay[1] && ( ~delay[2] ); // 原信號上升沿位置處產生的pulse信號

wire neg_signal = ( ~delay[1] ) && delay[2]; // 原信號下降沿位置處產生的pulse信號

?

?

?

?注意:前兩個觸發器的運用就是起同步作用,將某個信號同步到采樣時鐘域,以后要重點注意使用。

階段三:

用階段二的語句會比較繁瑣,可以用下述語句簡化:

reg[2:0] delay;

always @ ( posedge clk or negedge rstn )

if( !rstn )

delay <= 0;

else

delay <= { delay[1:0], ori_signal} ; // ori_signal是原信號

wire pos_signal = delay[1] && ( ~delay[2] ); // 原信號上升沿位置處產生的pulse信號

wire neg_signal = ( ~delay[1] ) && delay[2]; // 原信號下降沿位置處產生的pulse信號

Verilog中clk為什么要用posedge,而不用negedge

posedge是上升沿,電平從低到高跳變

negedge是下降沿,電平從高到低跳變

對于典型的counter邏輯

always @(posedge sys_clk or negedge sys_rst_n) begin

if(!sys_rst_n)

counter <= 24'd0;//十進制0

else if(counter < led_time) begin

flag_counter = 1'b0;

counter <= counter + 1'b1;

end

else begin

counter <= 24'd0;

flag_counter = 1'b1;

end

end

clk為什么要用posedge,而不用negedge呢?

一般情況下,系統中統一用posedge,避免用negedge,降低設計的復雜度,可以減少出錯。

在ModelSim仿真中,時鐘是很嚴格的,但是在真實的晶振所產生的clock卻是不嚴格的,比如高電平和低電平的時間跨度不一樣,甚至非周期性的微小波動。如果只使用posedge,則整個系統的節拍都按照clock上升沿對齊,如果用到了negedge,則系統的節拍沒有統一到一個點上。上升沿到上升沿肯定是一個時鐘周期,但是上升沿到下降沿卻很可能不是半個周期。這都會出現問題。

FPGA特有的東西:Global CLK。FPGA內部有專門的CLK“線”,和一般的邏輯門的走法不一樣,目的是為了保證整個FPGA片內的時鐘一致,這個東西就叫GlobalCLK

審核編輯 :李倩

-

Verilog

+關注

關注

29文章

1367瀏覽量

112319 -

觸發器

+關注

關注

14文章

2039瀏覽量

62161 -

上升沿

+關注

關注

0文章

3瀏覽量

1875

原文標題:Verilog學習筆記

文章出處:【微信號:gh_9d70b445f494,微信公眾號:FPGA設計論壇】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

CANFD模塊中的CLK_GR5如何配置?

【高云GW5AT-LV60 開發套件試用體驗】點亮LED

尋找verilog高手,有報酬

Verilog中signed和$signed()的用法

Verilog中clk為什么要用posedge,而不用negedge

Verilog中clk為什么要用posedge,而不用negedge

評論