1、取反操作

如下所示,信號a取反賦值給信號b,底層邏輯是,如果a位寬少于b位寬,則a先高位補0,再進行取反,最后賦值給b。

wire [4:0] a;wire [5:0] b;assign b=~a ; 等價于 assign b= ~{1’b0,a[4:0]};wire [4:0] a;wire [6:0] b;assign b=~a ; 等價于 assign b= ~{1’b0,1’b0,a[4:0]};

2、取反位寬不匹配錯誤案例

如果賦值語句或者條件判斷中用到了取反操作,一定需要先將取反值賦值相同的位寬 或者 與取反值做運算的信號一定要與原值位寬相同。

wire [2:0] mty_in ;//invalid byte in total 8 bytewire [3:0] vld_byte ;//valid byte in total 8 byteif( (~mty_in) <= 4’d5 )data_updata_vld =1elsedata_updata_vld =0;

在上面的代碼中,data_updata_vld永遠為0,因為(~mty_in) <= 4’d5比較時,會默認(~mty_in) 是4bit信號,因此(~mty_in)本質(zhì)上是~{1’b0,a[2:0]},[3]bit為1 永遠大于4’d5.

3、如何檢查

此類問題

采用vcs仿真可以看出仿真結(jié)果不符合預(yù)期

采用是spyglass,會報warning/err,說明運算符作為位寬不匹配

IC設(shè)計錯誤案例:加法溢出導(dǎo)致的錯誤

1、加法溢出導(dǎo)致的功能錯誤

如下圖所示錯誤代碼中,當(dāng)byte_add+byte_save等于256的時候,我們期望的的信號more_than_64應(yīng)該為1,而實際上在錯誤代碼中(byte_add+byte_save)與8’d64比較,(byte_add+byte_save)可能會被理解為8’d0,即被理解成8bit信號,more_than_64等于0,功能錯誤。在芯片設(shè)計中,有可能因為EDA工具之間差異導(dǎo)致對(byte_add+byte_save)>8’d64的理解不一樣,導(dǎo)致VCS等工具RTL級仿真正確,而DC綜合后功能錯誤。例如:VCS將(byte_add+byte_save)理解為9bit的位寬,而綜合理解為8bit位寬。一旦綜合理解為8bit位寬,則會導(dǎo)致網(wǎng)表與我們預(yù)期功能不一致,而且網(wǎng)表仿真比較慢,一般很慢遍歷所有RTL級仿真用例,因此此類問題不容易發(fā)現(xiàn)。

2、如何避免加法溢出導(dǎo)致的功能錯誤

如下圖所示正確代碼中,將賦值給9bit的add_byte_total,并且將add_byte_total與9’d64比較,而不是8’d64比較,這樣就不會發(fā)生溢出截斷比較的情況。

code begin-------------------------//wire more_than_64 ;reg [7:0] byte_add ;reg [7:0] byte_save ;reg [7:0] byte_update;assign more_than_64 = ( (byte_add+byte_save) > 8'd64);always@(*)if(more_than_64)byte_update = (byte_add + byte_save ) - 8'd64 ;elsebyte_update = 8'd0;code end-------------------------//and recommended code begin----------------------//wire more_than_64 ;reg [7:0] byte_add ;reg [7:0] byte_save ;reg [7:0] byte_update;wire [8:0] add_byte_total ;assign add_byte_total=(byte_add+byte_save);assign more_than_64 = ( add_byte_total > 9'd64);always@(*)if(more_than_64)byte_update = (byte_add + byte_save ) - 8'd64 ;elsebyte_update = 8'd0;and recommended code end----------------------//

-

IC設(shè)計

+關(guān)注

關(guān)注

38文章

1350瀏覽量

105309 -

VCS

+關(guān)注

關(guān)注

0文章

80瀏覽量

9858

原文標(biāo)題:IC設(shè)計錯誤案例:信號取反、加法溢出導(dǎo)致的錯誤

文章出處:【微信號:IP與SoC設(shè)計,微信公眾號:IP與SoC設(shè)計】歡迎添加關(guān)注!文章轉(zhuǎn)載請注明出處。

發(fā)布評論請先 登錄

模擬IC與數(shù)字IC對比分析

iOS之友盟錯誤分析及解決辦法

實測案例分析CAN總線局部錯誤及全局通知

華秋PCB專業(yè)分析工具-獨家BOM錯誤分析

PCB專業(yè)分析工具-獨家BOM錯誤分析

Bash編程常見錯誤范例及原因分析

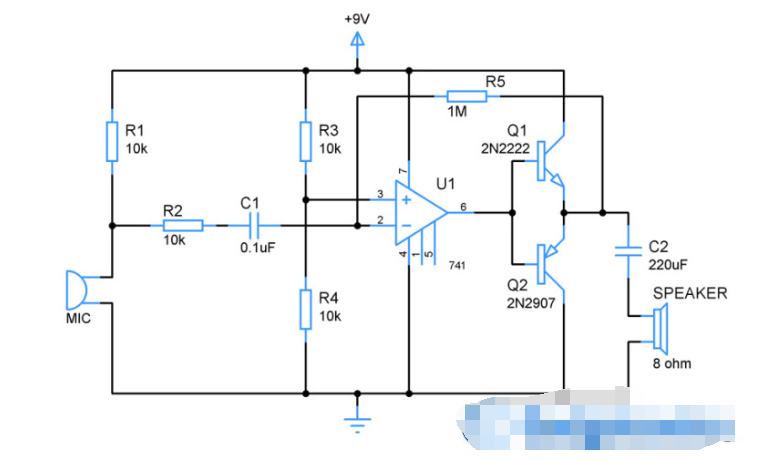

基于IC741構(gòu)建的簡單有線間諜錯誤電路

電橋電路的常見錯誤分析

基于Vector工具進行CAN協(xié)議錯誤幀的分析實踐

IC設(shè)計錯誤案例分析

IC設(shè)計錯誤案例分析

評論