早期集成電路設(shè)計(jì)中,工程師考慮的信號(hào)延遲主要產(chǎn)自于標(biāo)準(zhǔn)單元自身的延遲。然而從業(yè)界的主流工藝進(jìn)入深亞微米之后:

■繞線產(chǎn)生的信號(hào)延遲在總占比上越來(lái)越大

■信號(hào)噪聲對(duì)于芯片功能的影響也不斷增加

■在高頻電路中的頻率變化又會(huì)改變電阻、電感值的分配

這就對(duì)于寄生參數(shù)的計(jì)算精準(zhǔn)度有了更高的要求。伴隨著工藝的不斷升級(jí),芯片規(guī)模也在不斷擴(kuò)大,也對(duì)寄生參數(shù)提取的效率有了更高要求。

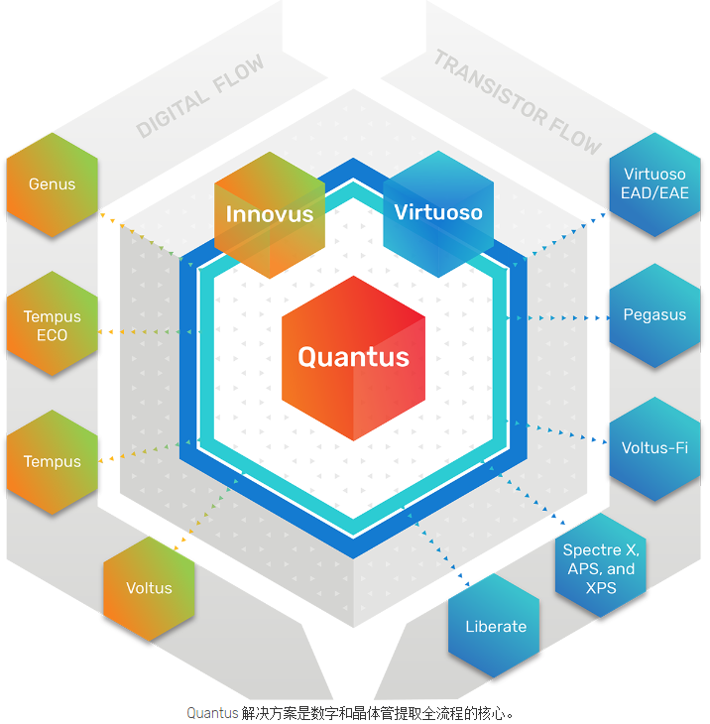

Quantus 是目前業(yè)界非常受信任的寄生參數(shù)抽取工具。在集成電路行業(yè)內(nèi),處于領(lǐng)先地位的制造廠商和設(shè)計(jì)公司都會(huì)大規(guī)模地應(yīng)用該工具,尤其在工藝制程步入深亞微米的先進(jìn)工藝領(lǐng)域(16 nm 及更先進(jìn)的制程),Quantus 在模擬電路和數(shù)字電路上的優(yōu)異表現(xiàn)都備受客戶的廣泛好評(píng)。

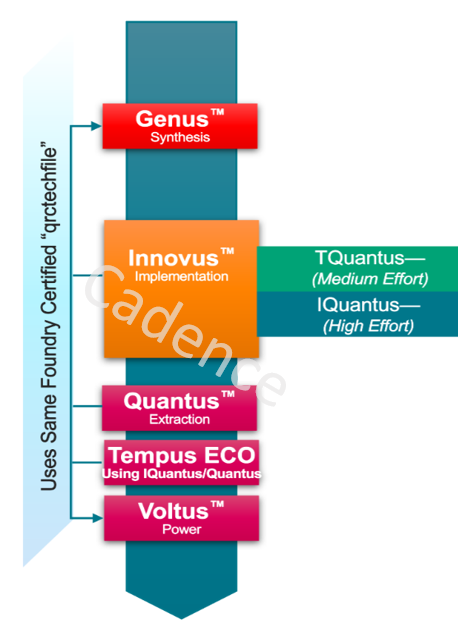

此外,Quantus 與 Cadence 的各類數(shù)字電路設(shè)計(jì)工具都有良好的集成,諸如 Genus&Innovus、Tempus、Voltus 等。工具與這些數(shù)字設(shè)計(jì)的平臺(tái)的深度綁定,為客戶提供了便捷和高效的體驗(yàn)。本文將簡(jiǎn)單介紹 Quantus 在數(shù)字電路設(shè)計(jì)上針對(duì)以上挑戰(zhàn)的一些解決方案和應(yīng)用實(shí)例。

Quantus 在數(shù)字電路設(shè)計(jì)中提取寄生的精度

Quantus 的運(yùn)行速度

Quantus 與 Cadence 其它工具平臺(tái)的深度集成和應(yīng)用

#1

Quantus 在數(shù)字電路設(shè)計(jì)中提取寄生的精度

從 2014 年開(kāi)始,Quantus 取得了具備各類先進(jìn)工藝制程的制造商的認(rèn)證:從最初的 16 nm、10 nm、7 nm,到目前行業(yè)內(nèi)最先進(jìn)的 3 nm 工藝,Quantus 在各個(gè)工藝節(jié)點(diǎn)上,不斷得到了各個(gè)知名芯片設(shè)計(jì)公司的肯定。

Quantus 抽取的寄生值與標(biāo)準(zhǔn)值的精度對(duì)比

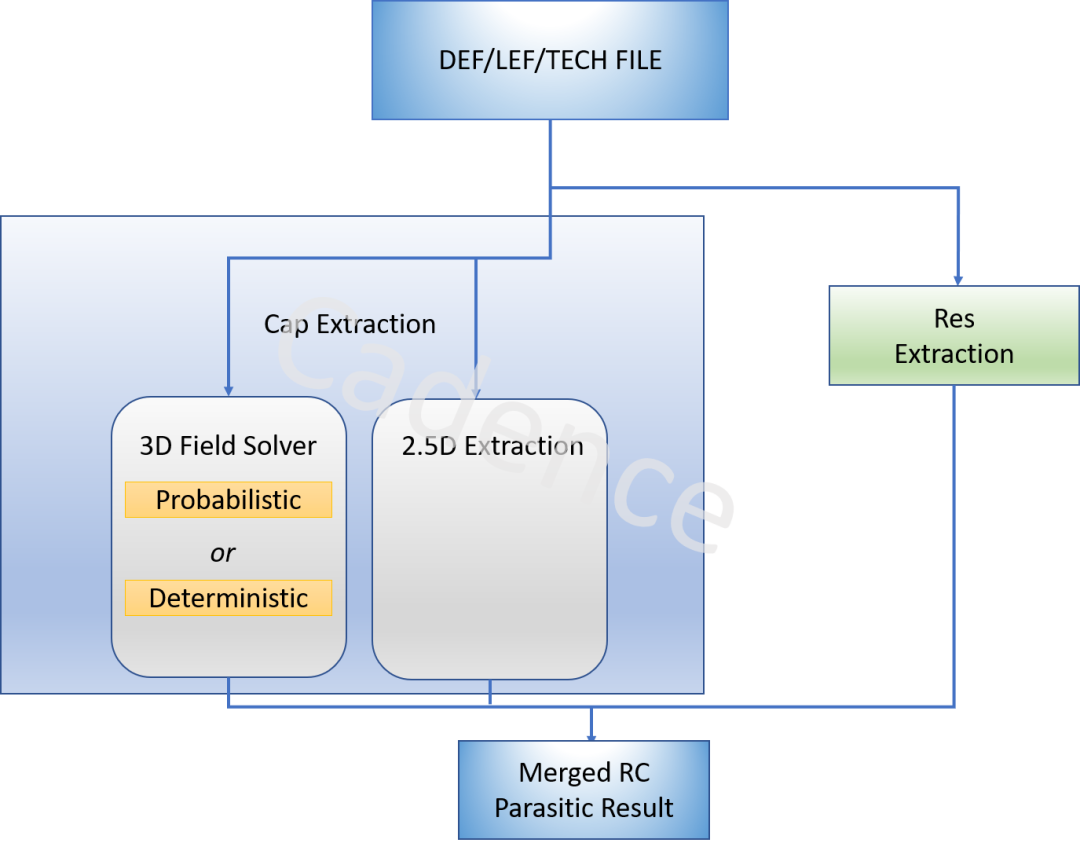

在寄生抽取中,電容的計(jì)算是最為繁瑣且復(fù)雜的,對(duì)此 Quantus 中內(nèi)嵌的 Random-Work Field Solver (3D)引擎,經(jīng)過(guò)先進(jìn)工藝芯片制造商的認(rèn)證,成為了寄生參數(shù)抽取中精度的標(biāo)準(zhǔn)值。不同于傳統(tǒng)的電容系數(shù)模型匹配(2.5D)方式,Quantus FS 引擎通過(guò) 3D 場(chǎng)效應(yīng)求解方式,直接依據(jù)版圖的形狀數(shù)據(jù)進(jìn)行計(jì)算,從而得到完全匹配真實(shí)芯片構(gòu)成的寄生電容數(shù)值。

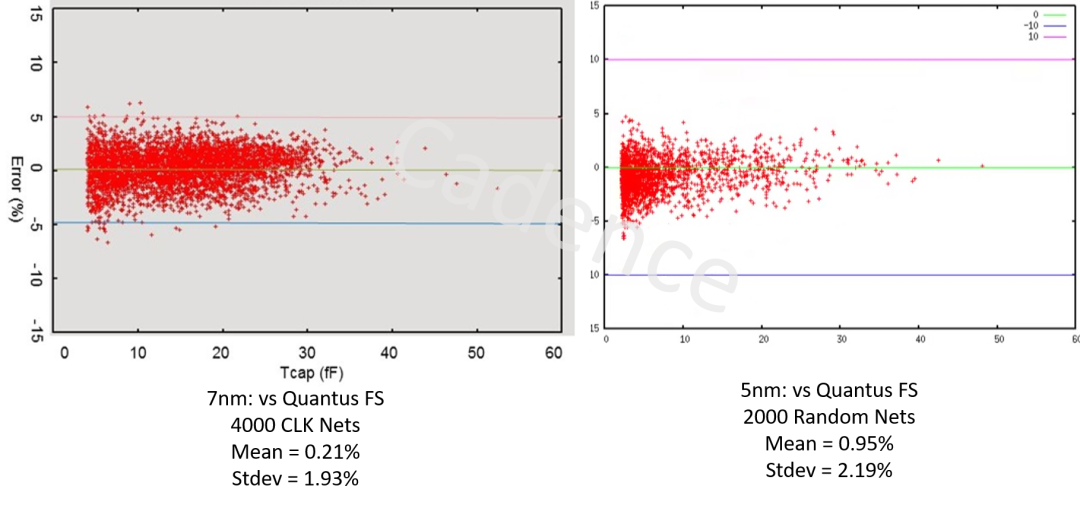

下圖為全球領(lǐng)先的美國(guó)集成電路芯片設(shè)計(jì)公司在 7 nm 和 5 nm 的工藝節(jié)點(diǎn)中,對(duì)于 Quantus 精度調(diào)研的例子:通過(guò)對(duì)比 Quantus 抽取的寄生電容數(shù)值和 Quantus FS 產(chǎn)生的標(biāo)準(zhǔn)值可以看到,Quantus 與標(biāo)準(zhǔn)值的誤差是處于制造商認(rèn)可的范圍內(nèi)的。

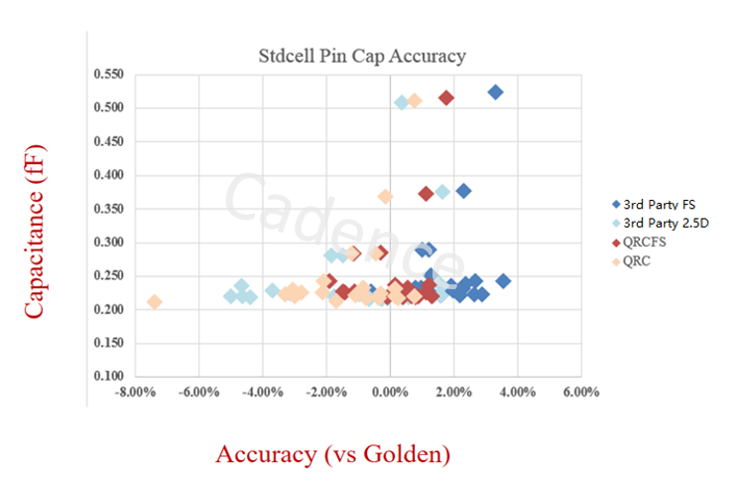

下圖是中國(guó)最大的通信設(shè)備制造廠商在 TSMC-OIP 2019 南京會(huì)議上做的寄生參數(shù)引擎抽取精度對(duì)比(7 nm)。可以看出 Quantus FS 和 Quantus 都有很好的收斂性。

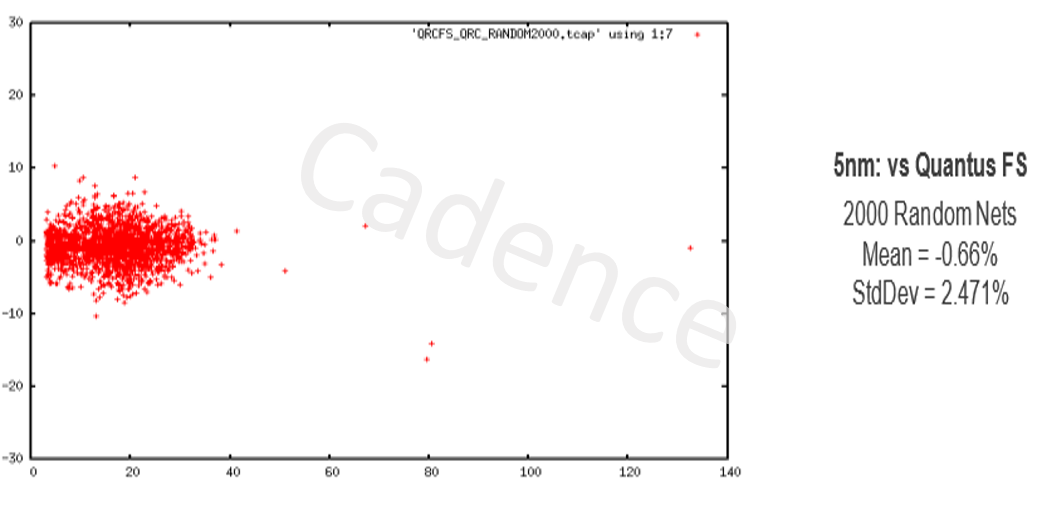

下圖是中國(guó)大陸移動(dòng)設(shè)備龍頭公司在 5 nm 工藝節(jié)點(diǎn)的實(shí)際案例中的精度對(duì)比:

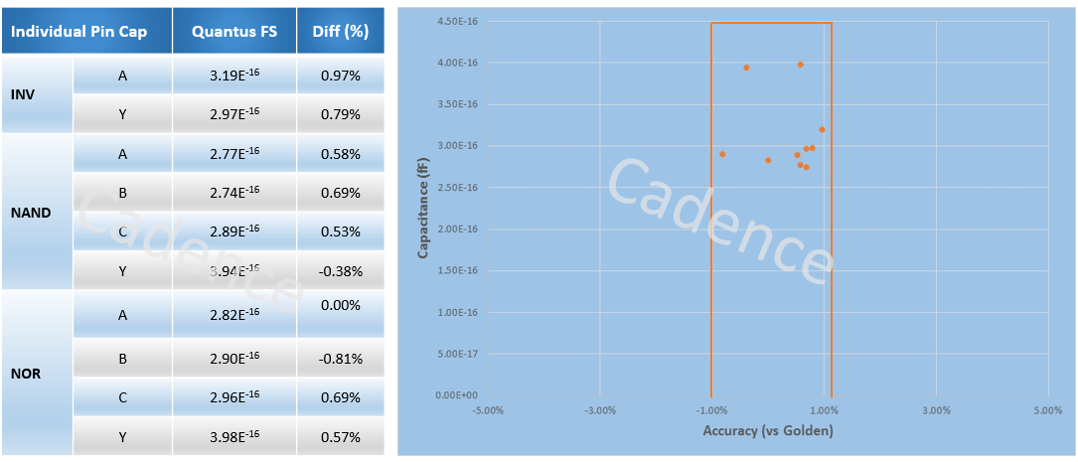

對(duì)于目前最先進(jìn)的 3 nm 制程,Quantus 在寄生抽取的精度上也有良好的表現(xiàn)。以下圖表展示的是全球最大工藝制造商在標(biāo)準(zhǔn)單元的實(shí)際分析中,對(duì)于 pin cap 的計(jì)算誤差,Quantus 也可以做到在正負(fù)百分之一以內(nèi)。

Quantus 在數(shù)字電路中的電感抽取

在高頻的數(shù)字電路設(shè)計(jì)中,考慮寄生電感對(duì)于芯片的可靠性分析造成的影響是相當(dāng)重要的。一般來(lái)說(shuō),如果時(shí)鐘線的頻率高于 1 GHz,單根高層時(shí)鐘線長(zhǎng)超過(guò) 1500 micron 的話,電感所造成的影響是不可忽視的,且其主要表現(xiàn)在以下兩個(gè)方面:過(guò)沖 / 下沖(overshoot / undershoot)和時(shí)鐘延遲。

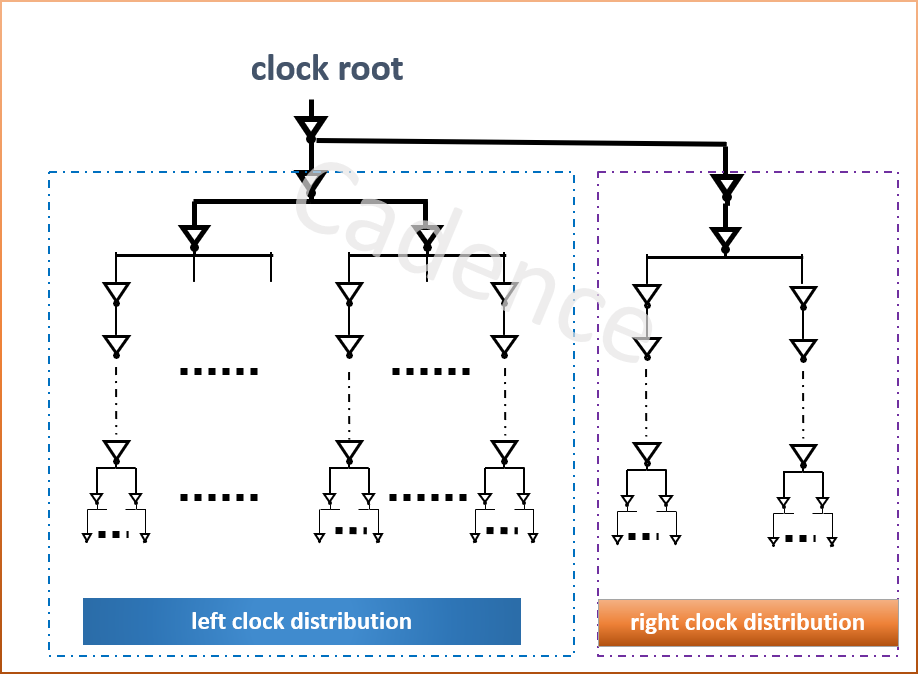

以下從客戶設(shè)計(jì)的實(shí)例入手分析,左側(cè)時(shí)鐘樹(shù)采用了更寬、更厚、更長(zhǎng)的繞線,可以得到更多的時(shí)鐘分布;右側(cè)時(shí)鐘樹(shù)的繞線更窄、更短,能夠使用的時(shí)鐘分布就會(huì)偏少。

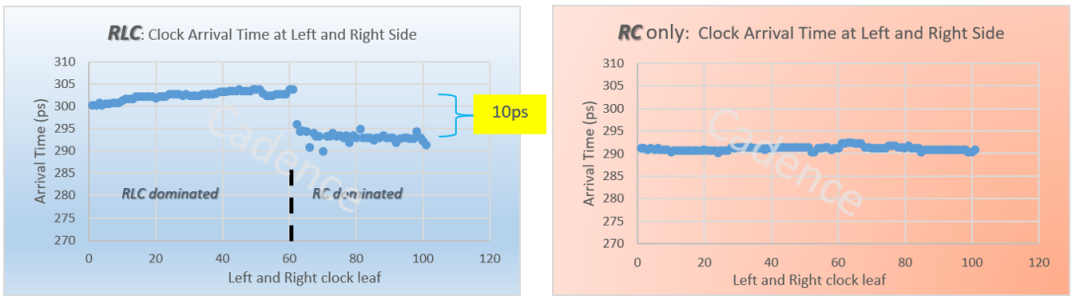

如果在分析寄生參數(shù)的時(shí)候不考慮電感效應(yīng)(RC only),那么兩邊的時(shí)鐘樹(shù)在到達(dá)時(shí)間上相差無(wú)幾。然而在實(shí)際分析中,客戶引入 Quantus 電感抽取(RLC)的解決方案后發(fā)現(xiàn):左側(cè)時(shí)鐘樹(shù)的到達(dá)時(shí)間會(huì)相比于右側(cè),有著顯著的延遲(見(jiàn)下圖對(duì)比)。因此,如果忽略了寄生電感的影響,則有可能造成芯片在時(shí)序上的失效。

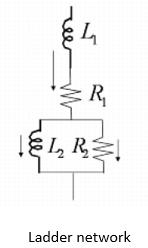

對(duì)于電感的計(jì)算可分為環(huán)路電感和區(qū)域電感,前者是人們熟知的電磁感應(yīng)模型,簡(jiǎn)單卻不具備通用性,而后者的計(jì)算雖然復(fù)雜,但是適用于網(wǎng)表中的二維節(jié)點(diǎn)分析,因此 Quantus 采用了后者的表達(dá)方式,將寄生電感引入到網(wǎng)表中。

此外,Quantus 可以支持自感和互感的抽取。采用 Partial Element Equivalent Circuit(區(qū)域電感等效模型 PEEC)的電感提取算法,可以得到區(qū)域電感的數(shù)值并融入到電路網(wǎng)表中,由此可以計(jì)算 90° 和 45° 的電感互聯(lián)。在數(shù)字電路的電感抽取中,推薦使用的另一種模型 Ladder Network 更是可以匹配因?yàn)橼吥w效應(yīng)和鄰近效應(yīng)等造成的寄生電感。

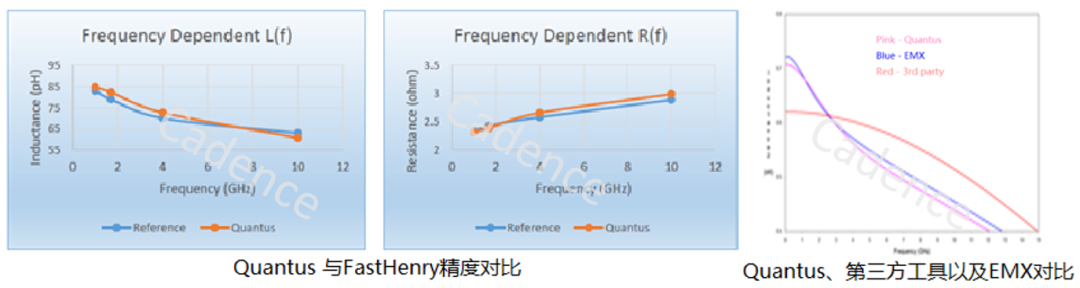

在電感提取中,業(yè)界通常認(rèn)為 FastHerny 和 EMX 的結(jié)果作為標(biāo)準(zhǔn)值。通過(guò)與 FastHenry 的對(duì)比可以發(fā)現(xiàn),Quantus 在高頻電路中,可以很好地模擬出寄生電阻和寄生電感隨著電路工作頻率的增加而產(chǎn)生的變化。Quantus 抽取的電感精度也從實(shí)驗(yàn)中得到了證實(shí):在工作頻率逐漸增加的電感值計(jì)算中,Quantus 和 EMX 的結(jié)果在擬合程度上是遠(yuǎn)勝于第三方工具的。

Customer Success Story—Top 10 Semiconductor Company

#2

Quantus 的運(yùn)行速度

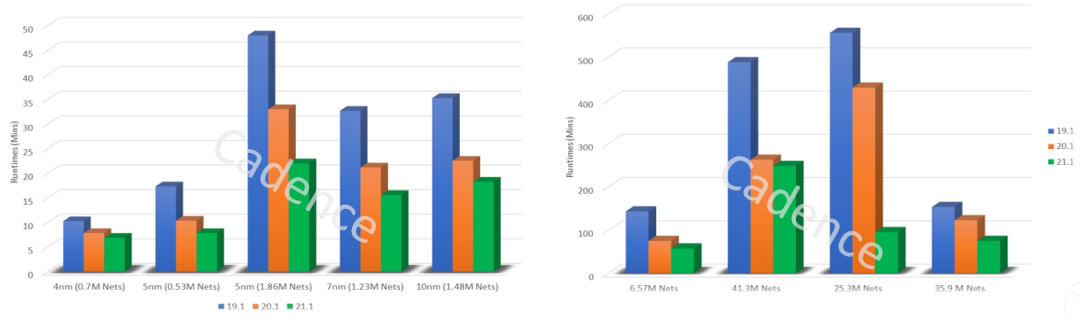

Quantus 每年發(fā)布的新版本都會(huì)比舊版本有很大的速度提升。無(wú)論是對(duì)于底層模塊設(shè)計(jì)還是對(duì)于頂層的設(shè)計(jì)。在最新的 21 版本中,Quantus 的平均抽取速度要比 20 版本提高了 50% 以上,而相較于 19 版本則有 2 倍多提升。

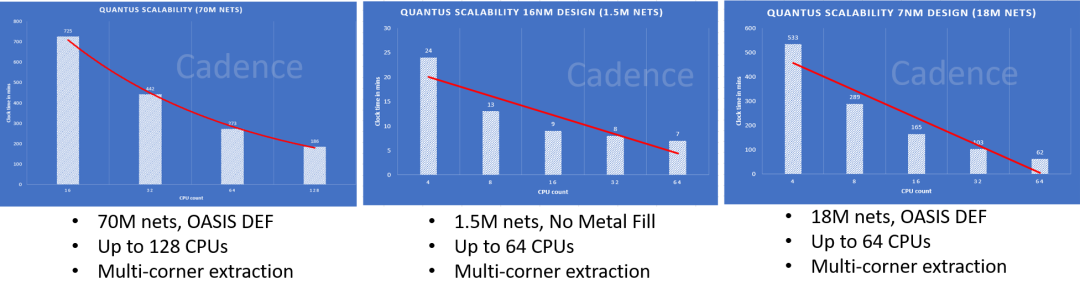

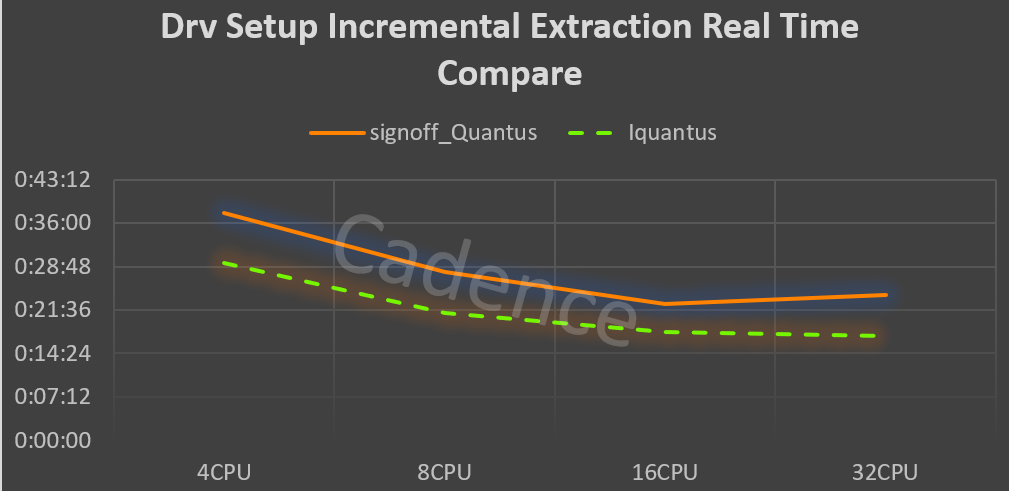

Quantus 的多核抽取方式,展現(xiàn)了良好的速度與線程數(shù)量的線性關(guān)系。以下為客戶在先進(jìn)制程中使用 Quantus 的實(shí)際例子。

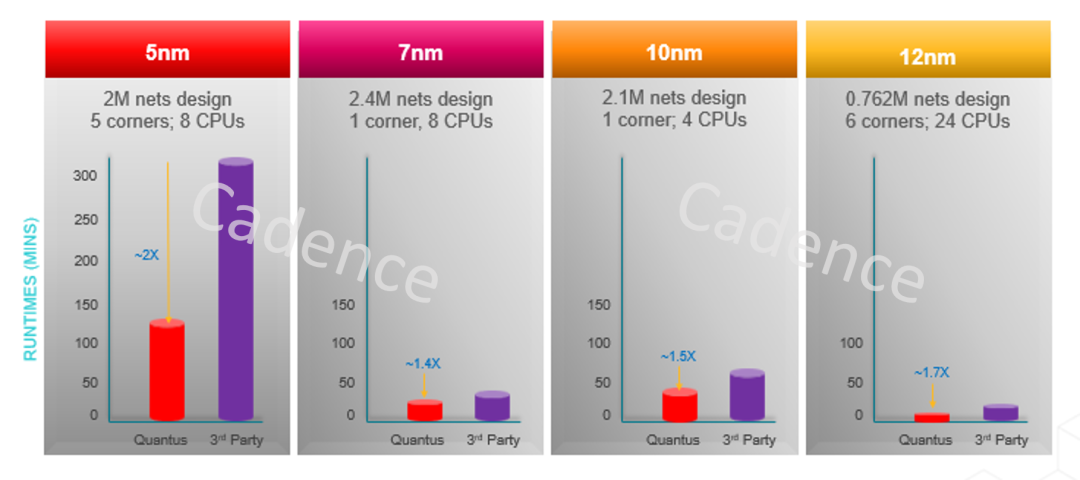

Quantus 與業(yè)內(nèi)的其它抽取工具相比,在速度上也有一定的優(yōu)勢(shì)。以下圖片展示了從 12 nm 到 5 nm 工藝制程的芯片設(shè)計(jì)中,Quantus 與某第三方工具的速度對(duì)比。

#3

Quantus 與 Cadence 其它工具平臺(tái)的深度集成和應(yīng)用

在后端驗(yàn)證工具的集成上,Quantus 與Innovus 和 Tempus 有著深度的綁定

對(duì)于 PR 工具 Innovus,時(shí)序的分析是驅(qū)動(dòng)整個(gè)流程的根本,并且在不同的分析階段,對(duì)于時(shí)序的精確度的需求也是大相徑庭的。對(duì)此,Quantus 有不同的抽取引擎來(lái)提供時(shí)序分析所需的寄生參數(shù):例如,在全局的 placement 階段, 僅需要粗略的計(jì)算可能的寄生對(duì)時(shí)序的影響,Quantus 有對(duì)應(yīng)的 TQuantus 引擎提供支持,可以快速地得到布局過(guò)程中所引起的寄生參數(shù)估計(jì);在繞線階段,需要依據(jù)繞線情況來(lái)提供較為精確的寄生信息,對(duì)此,Quantus 提供了 IQuantus 引擎,可以在有限的精度損失下,以較快的速度來(lái)支持 ECO 階段的迭代分析;對(duì)于最后的 Signoff 階段,需要使用 Quantus 的引擎來(lái)提供最精確的寄生參數(shù)分析。

在抽取引擎(preroute / postroute)的選擇中,如果選擇了 preroute ,則 RC 的抽取是基于繞線的密度和 net 的形狀(由 early GlobalRoute 和 Clock Tree Synthesis 提供)來(lái)進(jìn)行計(jì)算的,并且是不考慮耦合電容;如果選擇了 postroute,則 RC 的抽取是基于繞線的間距來(lái)進(jìn)行計(jì)算的,并且是考慮耦合電容的。

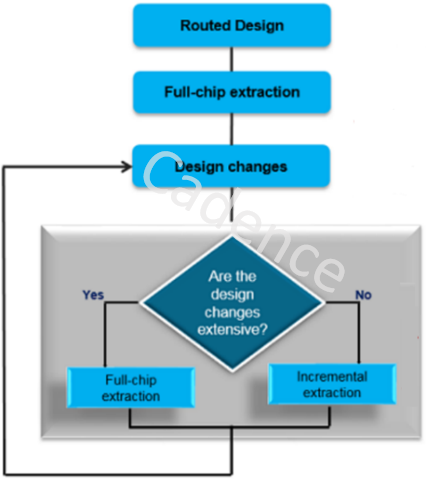

對(duì)于 IQRC 和 Signoff QRC 有兩種抽取模式:全局寄生抽取模式和增量寄生抽取模式。對(duì)低于一定閾值(基于 net 數(shù)量和面積)的改動(dòng),使用的是增量寄生抽取模式,反之則會(huì)觸發(fā)全局寄生抽取模式。

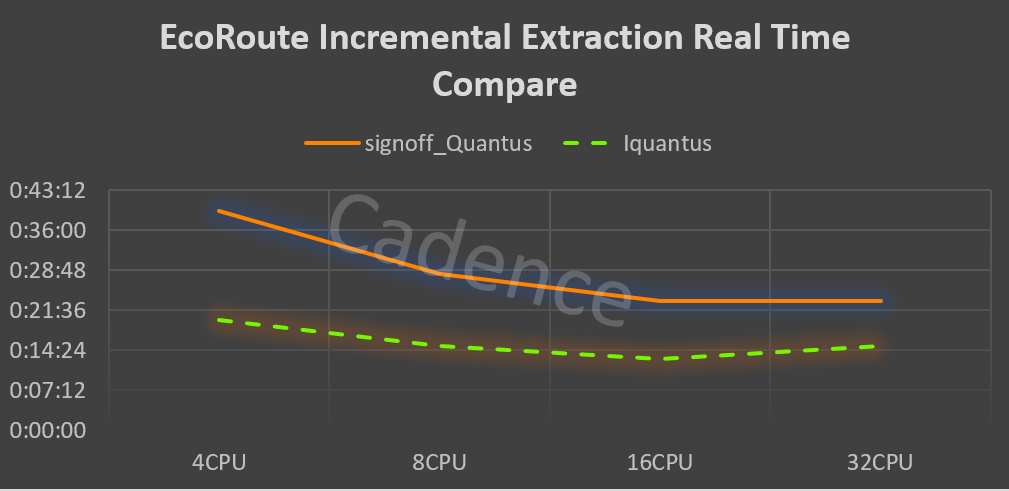

在 Innovus 中調(diào)用 Tempus 執(zhí)行 ECO 的階段,基于時(shí)序的考慮,需要對(duì)芯片設(shè)計(jì)中用到的緩沖器做優(yōu)化(替換)來(lái)滿足設(shè)計(jì)規(guī)則,對(duì)于這個(gè)階段的寄生參數(shù)信息,使用增量抽取模式是最為高效的。下圖比較了在該階段中,Quantus 與 IQuantus 在其中兩個(gè)步驟的運(yùn)行時(shí)間,一個(gè)考慮的是緩沖器變換所引起的寄生變化,另一個(gè)則是考慮了在緩沖器更換后重新布線所引起的寄生變化。從實(shí)驗(yàn)結(jié)果可以看出,在增量寄生的抽取中,IQRC 有著顯著的性能優(yōu)勢(shì),即在 CPU 資源有限的情況下可以更好地減少運(yùn)行時(shí)間。

左右滑動(dòng)查看更多

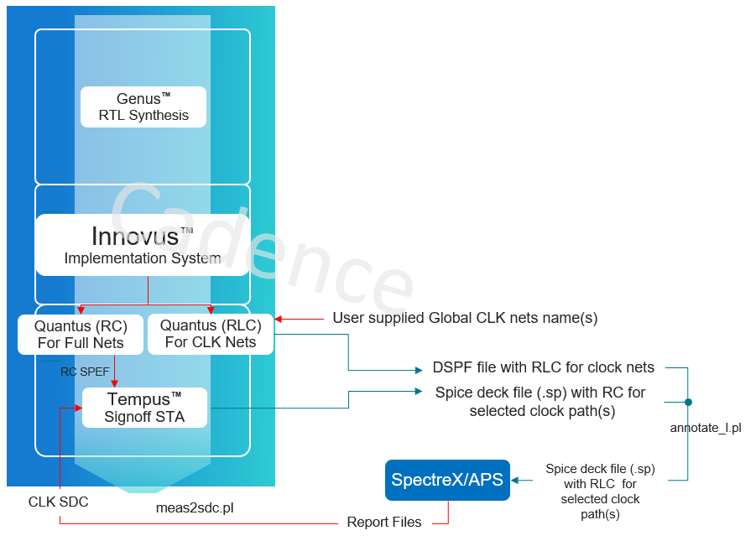

Quantus 與 Cadence 的其它平臺(tái)(Spectre、Tempus)在電感分析流程上有緊密聯(lián)系

用戶可以通過(guò)將 Quantus 產(chǎn)生的帶有電感寄生參數(shù)的 DSPF 網(wǎng)表和由 Tempus 產(chǎn)生的 SPICE 網(wǎng)表相結(jié)合,進(jìn)由 Spectre 仿真,從而判斷電感是否對(duì)設(shè)計(jì)造成了過(guò)沖 / 下沖 (overshoot / undershoot)的影響。同時(shí)在 Spectre 的報(bào)告文件中,可以提取出用于做靜態(tài)時(shí)序分析的 SDC 文件。通過(guò)使用這個(gè) SDC 文件,Tempus 可以做出同時(shí)基于電阻、電容、電感的靜態(tài)時(shí)序分析。

綜上所述,隨著芯片設(shè)計(jì)更加復(fù)雜、生產(chǎn)工藝更加先進(jìn),寄生參數(shù)的分析對(duì)于芯片的功能性甚至成敗發(fā)揮了更加重要的作用。為了解決寄生參數(shù)分析的精度以及抽取效率問(wèn)題,Quantus 提供了準(zhǔn)確、高效、完整的解決方案,為客戶的芯片設(shè)計(jì)保駕護(hù)航。

-

芯片

+關(guān)注

關(guān)注

459文章

52174瀏覽量

436139 -

集成電路

+關(guān)注

關(guān)注

5420文章

11950瀏覽量

367143 -

模擬電路

+關(guān)注

關(guān)注

125文章

1588瀏覽量

103675 -

數(shù)字電路

+關(guān)注

關(guān)注

193文章

1637瀏覽量

81581

原文標(biāo)題:淺析 Quantus 在 Cadence 數(shù)字設(shè)計(jì)平臺(tái)中的深度應(yīng)用

文章出處:【微信號(hào):gh_fca7f1c2678a,微信公眾號(hào):Cadence楷登】歡迎添加關(guān)注!文章轉(zhuǎn)載請(qǐng)注明出處。

發(fā)布評(píng)論請(qǐng)先 登錄

FPGA數(shù)字電路設(shè)計(jì)經(jīng)驗(yàn)分享

FPGA CPLFPGA CPLD 數(shù)字電路設(shè)計(jì)經(jīng)驗(yàn)分享

數(shù)字電路設(shè)計(jì)的基本方法有哪些

基于LabVIEW的數(shù)字電路設(shè)計(jì)和仿真

高速數(shù)字電路設(shè)計(jì)

數(shù)字電路設(shè)計(jì)

FPGA CPLD數(shù)字電路設(shè)計(jì)經(jīng)驗(yàn)分享.

Quantus在數(shù)字電路設(shè)計(jì)上面對(duì)的挑戰(zhàn)

Quantus在數(shù)字電路設(shè)計(jì)上面對(duì)的挑戰(zhàn)

評(píng)論