數字電路設計全流程解析來啦!

數字電路設計是數字電路最為關鍵及重要的一步,今天我們將從各個流程為大家介紹完整的數字電路設計!

1總述

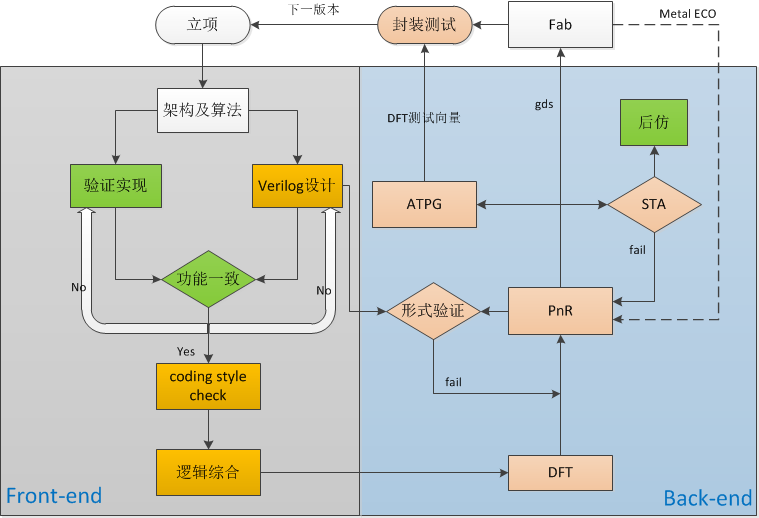

數字電路設計的基本流程如下圖。大致可以分為立項,架構和算法,設計/驗證,代碼風格檢查、綜合、DFT設計、后端PnR,靜態時序分析STA,后仿,流片,封裝測試。之后根據測試的結果又會反饋給下一代的項目形成一個良性的循環。

理論上,流片過程中必須的環節是Verilog設計、邏輯綜合和后端布局布線,因為只要有這三步,我們就能夠把一個行為級的Verilog代碼轉換成門級網表,再通過PnR轉換成版圖GDS(Fab所需的版圖二進制文件),再把版圖GDS release給Fab完成流片過程。除此之外其他所有的工序和步驟都是為了保證所設計代碼的功能和時序是符合要求的。畢竟在隨著制造工藝越來越先進到如今的3nm時代,一次流片的成本需要幾千萬美金。流片失敗的代價是非常大的。不僅錯過了產品的市場窗口,同時也對資金的損失非常大。所以我們需要越來越多額外的工序、需要越來越復雜的驗證方法學保證設計的正確性。

2數字電路設計流程分步驟解析

立項:從市場調研確定需要做一顆什么樣的芯片,芯片的功能是哪些。具體指標要達到什么程度,市面的競爭對手有哪些。成功流片能夠拿到多少市場份額,能夠對公司產生多少利潤,現金流等等

確定需要投入到這顆芯片的人力、物力和財力。規劃好芯片的流片時間,制定項目計劃和進度表。安排所有人員的工作以及schedule并隨時跟蹤

架構計算法:算法部門通過仿真建模確定每個部分的計算精度,量化控制,以及采用的計算方式等等

Architecture部門確定芯片的整體布局和架構,確定芯片最頂層的工作模式,子模塊之間如何聯動工作,芯片的性能,功耗,面積等各種參數

Verilog 設計:本課程的重點內容。

課程詳情及試聽課進入小程序查看:

通過Verilog這種硬件描述語言實現所需的各種功能。

注意設計中所有的代碼必須是可綜合代碼

驗證:另一門驗證課程的重點內容

課時介紹:

課程詳情及試聽課進入小程序查看:

如何用system Verilog以及UVM對被測RTL進行邏輯功能的驗證

主要集中考慮如何創建更多的測試用例保證所有的輸入組合都能夠遍歷到,同時在所有遍歷輸入時輸出都是符合預期的

通過代碼覆蓋率、功能覆蓋率等保證驗證的完備性

同時考慮驗證平臺的自動化,可移植性和可復用性等等

Coding Style check:一般采用spyglass工具。檢查電路中的代碼是否有潛在的問題。比如多個數相加導致的潛在溢出問題。異步復位信號又被當成邏輯信號使用,某一個信號即被當成異步復位,又被當成異步置位、賦值位寬對不上、實例化時信號對應不上等等

同時也會檢查設計中所有的異步設計是否有防止亞穩態傳播的電路

邏輯綜合:本課程后續會講解邏輯綜合的基本流程

目的是在時序和面積等約束下把RTL的行為級Verilog代碼轉換成對應工藝的門級網表。同時產生約束文件并一起給后端進行布局布線

DFT和ATPG:DFT和ATPG本身和芯片的功能是沒有任何相關性的。

目的主要是為了能夠檢查出Fab在制造過程中意外引入的缺陷。尤其是Fab良率不高時尤其重要

DFT的原理是通過把設計中的每一個觸發器轉換成帶掃描鏈端口的觸發器,從而能夠給設計中的每一個觸發器都賦一個初值。然后通過不同的初值能夠遍歷電路內部每一條線的狀態,從而確定版圖中的每一條在制造過程中是否有缺陷

ATPG則是根據DFT的掃描鏈產生出這些測試所需要的測試向量。并把測試向量以及期望輸出結果一起給ATE。ATE由此可以對每一個芯片進行篩選判斷其是否有制造缺陷

布局布線PnR:

課程詳情及試聽課進入小程序查看:

目的是在約束文件的控制下,把綜合產生的門級網表生成對應工藝的物理版圖。并完成版圖直接的連線

其中主要步驟有FloorPlan,CTS, Placement, Route, DFM等

一般由專門的后端人員負責。尤其是對于IP眾多,連線以及DRC規則復雜的芯片

形勢驗證:目的是比較兩個待測設計的邏輯是否完全一直

其中比較的點主要集中在所有的輸出端和觸發器端

常用case1:比較綜合后的網表和RTL網表是否一致,防止綜合工具引入的意外錯誤

常用case2:比較綜合后網表和后端網表是否一致,防止后端工具引入錯誤

常用case3:比較ECO后網表和同樣ECO后RTL功能是否一致,保證網表的ECO功能是符合預期的

靜態時序分析STA:主要應用于所有的同步電路設計,檢查其中時序是否符合要求,對異步電路是不起作用的。

實際的制造過程中離子注入摻雜等不可能完全均勻,芯片在工作中溫度和電壓也不可能完全不變,為了保證芯片的時序在合理范圍內都能正常。需要通過STA工具保證芯片在每一種PVT(工藝,電壓,溫度)組合下時序都能通過

同時STA工具在發現時序問題后還可以進行時序修復

后仿:速度非常慢,比前仿慢數十倍,所以一般只跑幾個典型的工作場景

理論上STA和形勢驗證已經能夠保證電路中所有同步電路都能正常工作,但有兩種情況還是需要后仿的輔助:一是設計中時序的約束意外寫錯了,只能通過后仿發現。二是設計中異步電路的問題也只能通過后仿才能發現

流片 Tape Out:把后端生成的GDS二進制文件發送給Fab

一般需要2~3個月完成

掩膜版是流片中最貴的部分。一般Fab會把制造過程大致分為兩個階段。第一階段是基礎Base layer掩膜版制造階段。此時若設計發現問題,可以通過修改metal解決,那么metal層的掩膜版可以直接用新的。節省資金。第二階段是metal層掩膜版制造。此時如果發現問題并可以通過修改metal解決,那么只能重新制造掩膜版,但相比完整重新流片還是可以節省不少時間和資金

ECO:如前所述,芯片在制造或者測試過程中發現問題,如果流程從頭開始走一遍來修復該問題,費時長同時消耗資金。

如果發現的問題比較簡單。能夠使用電路中預留的冗余單元,并修改一些金屬連線就能修復該問題,那么就可以極大的節省時間和開支

此過程修改只能直接基于網表,為了保證網表修改沒有錯誤,需要用形勢驗證工具保證修改后的網表功能和直接改RTL功能是一致的

封裝與測試:根據芯片的速度、功耗等要求可以進行Flip-chip,BGA等各種封裝

一般先由ATE進行芯片篩選。篩選后通過的片子再進行進一步的功能測試

測試發現的問題需要設計和驗證人員進行復現。確定能夠復現問題后再決定是否需要修改,或者可以在軟件層面繞過

審核編輯:湯梓紅

-

電路設計

+關注

關注

6701文章

2530瀏覽量

213437 -

Verilog

+關注

關注

29文章

1366瀏覽量

111966 -

數字電路

+關注

關注

193文章

1637瀏覽量

81660

原文標題:【干貨】數字電路設計全流程是什么樣的?

文章出處:【微信號:feifeijiehaha,微信公眾號:電路和微電子考研】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

數字電路設計的基本流程

數字電路設計的基本流程

評論