DDR4/DDR5 Interposer產(chǎn)品說明書

應(yīng)用場景:

支持DDR4 DDR5的芯片顆粒測試,符合JEDEC協(xié)會規(guī)范。

主要特點:

阻抗一致性優(yōu)越,體積緊湊。

極低的插入損耗。

搭配riser板可在所有硬件系統(tǒng)測試。

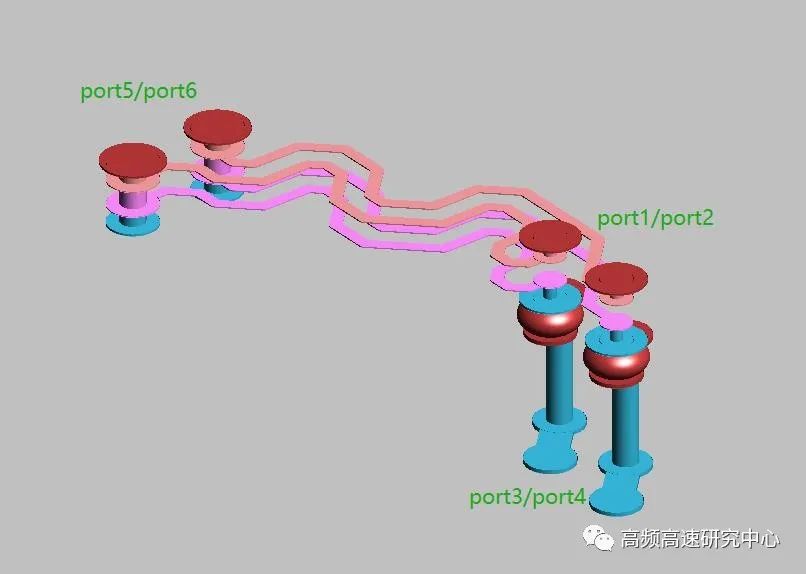

各通道skew差異小于±1ps。

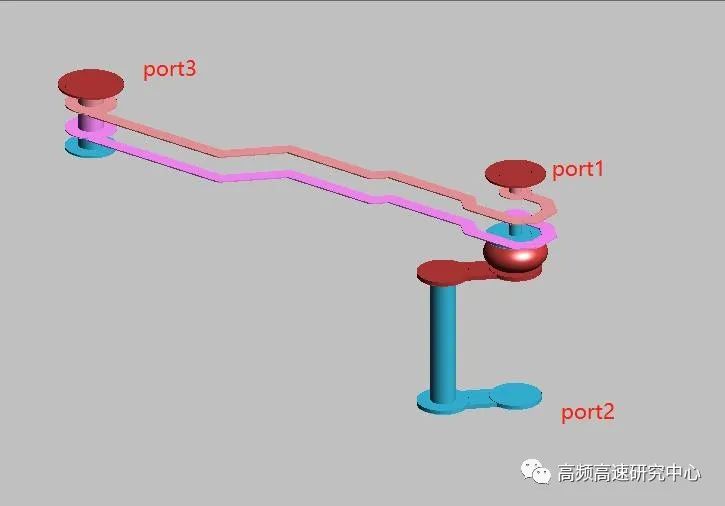

8層3階盲埋孔工藝,極限加工。

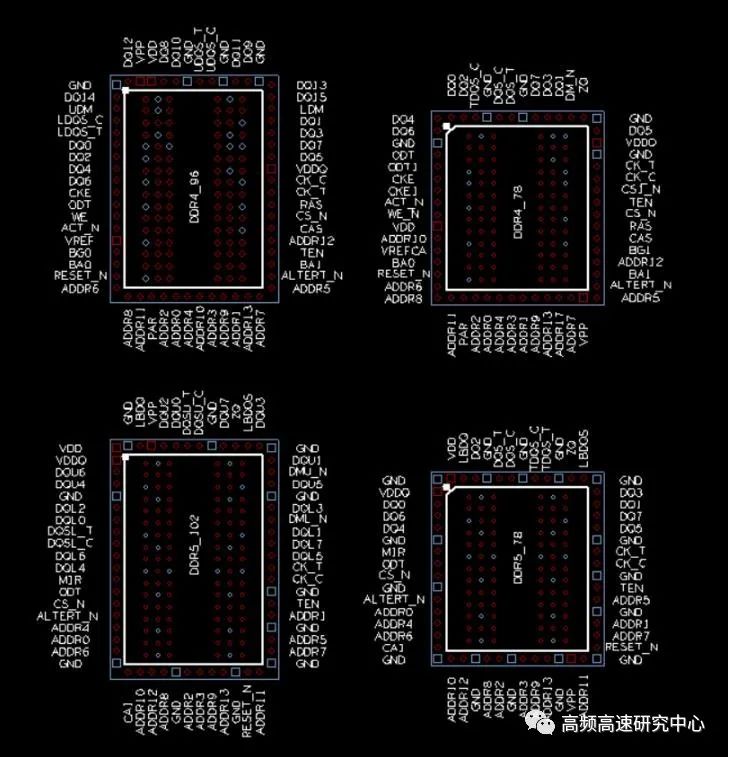

迪賽康DDR4/DDR5 Interposr測試板專門為內(nèi)存顆粒測試設(shè)計,阻抗一致性優(yōu)異,極低延遲,最高速率支持6.4Gbps,可以用于78pin和96pin/102pin封裝的DDR4和DDR5顆粒測試。

內(nèi)存芯片所有信號均引出板邊,包括電源和地,根據(jù)實際測試環(huán)境可選擇使用增高板(Riser)避開周邊干涉。

●因為走線空間狹小,所以要通過仿真精準(zhǔn)確定層疊和走線拓撲結(jié)構(gòu)

DDR顆粒的Interposer板測試一般是將DDR4或DDR5顆粒焊接在Interposer上再焊接在產(chǎn)品單板(根據(jù)實際情況決定是否需要增加riser板避開單板器件)后,上電可以正常開機,表示通過系統(tǒng)檢測,然后就可以通過測試探頭連接儀器對相關(guān)的信號進行測試。

審核編輯:劉清

-

連接器

+關(guān)注

關(guān)注

99文章

15067瀏覽量

138733 -

DDR

+關(guān)注

關(guān)注

11文章

719瀏覽量

66158

原文標(biāo)題:【迪賽康】DDR4/DDR5 Interposer產(chǎn)品說明書

文章出處:【微信號:si-list,微信公眾號:高頻高速研究中心】歡迎添加關(guān)注!文章轉(zhuǎn)載請注明出處。

發(fā)布評論請先 登錄

相關(guān)推薦

三大內(nèi)存原廠或?qū)⒂?025年停產(chǎn)DDR3/DDR4

DDR3、DDR4、DDR5的性能對比

DDR4內(nèi)存適合哪些主板

DDR5內(nèi)存與DDR4內(nèi)存性能差異

DDR5內(nèi)存的工作原理詳解 DDR5和DDR4的主要區(qū)別

如何選擇DDR內(nèi)存條 DDR3與DDR4內(nèi)存區(qū)別

DDR4時序參數(shù)介紹

什么是DDR4內(nèi)存的工作頻率

DDR4內(nèi)存頻率最高多少

什么是DDR4內(nèi)存模塊

DDR4內(nèi)存的常見問題有哪些

Introspect DDR5/LPDDR5總線協(xié)議分析儀

DDR5內(nèi)存條上的時鐘走線

0706線下活動 I DDR4/DDR5內(nèi)存技術(shù)高速信號專題設(shè)計技術(shù)交流活動

專門為內(nèi)存顆粒測試設(shè)計的DDR4/DDR5 Interposr測試板

專門為內(nèi)存顆粒測試設(shè)計的DDR4/DDR5 Interposr測試板

評論