RISC-V是當(dāng)下熱門的技術(shù),值得大家學(xué)習(xí),這里分享一份關(guān)于RISC-V指令的內(nèi)容給大家。

1. 指令集

1.1 指令集

指令集是一個CPU的基石,要實現(xiàn)CPU 計算和控制功能,就必須定義好一系列與硬件電路相匹配的指令系統(tǒng).

指令就是我們交代CPU 要執(zhí)行的操作,指令集就可以簡單理解為指令的集合。我們把cpu 能夠識別的指令匯總在一起就構(gòu)成了一個指令集。

不同的CPU 有不同的指令集,根據(jù)他們的繁簡程度可以分為兩種:復(fù)雜指令集CISC 和精簡指令集 RISC

1.2 指令集架構(gòu)

指令架構(gòu)(Instruction Set Architecture, 縮寫為ISA),是軟件和硬件的接口,不同的應(yīng)用需求,會有不同的指令架構(gòu)。要設(shè)計一款CPU 指令體系就是設(shè)計的出發(fā)點。

2. RISC-V 指令集架構(gòu)

RISC-V 指令有以下特點:

完全開放

指令簡單

模塊化設(shè)計,易于擴(kuò)展

| 名稱 | 類別 | 說明 |

|---|---|---|

| RV32I | 基礎(chǔ)指令 | 整數(shù)指令:包含算法、分支、邏輯、訪存指令,有32個32位寄存器。能尋址32位地址空間 |

| RV64I | 基礎(chǔ)指令 | 整數(shù)指令:包含算法、分支、邏輯、訪存指令,有32個64位寄存器。能尋址64位地址空間 |

| RV128I | 基礎(chǔ)指令 | 整數(shù)指令:包含算法、分支、邏輯、訪存指令,有32個128位寄存器。能尋址128位地址空間 |

| RV32E | 基礎(chǔ)指令 | 與RV32I一樣,只不過只使用前16個(0~15)32位寄存器 |

| M | 擴(kuò)展指令 | 包含乘法、除法、取模求余指令 |

| F | 擴(kuò)展指令 | 單精度浮點指令 |

| D | 擴(kuò)展指令 | 雙精度浮點指令 |

| Q | 擴(kuò)展指令 | 四倍精度浮點指令 |

| A | 擴(kuò)展指令 | 原子操作指令:比如比較并交換,讀改寫等指令 |

| C | 擴(kuò)展指令 | 壓縮指令:單指令長度為16位,主要用于改善程序大小 |

| P | 擴(kuò)展指令 | 單指令多數(shù)據(jù)(Packed-SIMD)指令 |

| B | 擴(kuò)展指令 | 位操作指令 |

| H | 擴(kuò)展指令 | 支持(Hypervisor)管理指令 |

| J | 擴(kuò)展指令 | 支持動態(tài)翻譯語言指令 |

| L | 擴(kuò)展指令 | 十進(jìn)制浮點指令 |

| N | 擴(kuò)展指令 | 用戶中斷指令 |

| G | 通用指令 | 包含I、M、A、F、D 指令 |

要滿足現(xiàn)在操作系統(tǒng)和應(yīng)用程序的基本運行,RV32G指令集或者RV64G指令集就夠了。RV32G和RV64G指令集只有寄存器位寬和尋址大小不同。這些指令按照功能可以分為如下幾類:

整數(shù)運算指令:算術(shù)、邏輯、比較等基礎(chǔ)運算功能。

分支轉(zhuǎn)移指令:實現(xiàn)條件轉(zhuǎn)移、無條件轉(zhuǎn)移操作

加載存儲指令:實現(xiàn)字節(jié)、半字(half word)、字(word)、雙字(RV64I)的加載,存儲操作,采用的都是寄存器相對尋址方式

控制與狀態(tài)寄存器訪問指令:實現(xiàn)對系統(tǒng)控制與系統(tǒng)狀態(tài)寄存器的原子讀-寫、原子讀-修改、原子讀-清零等操作

系統(tǒng)調(diào)用指令:實現(xiàn)系統(tǒng)調(diào)用功能。

原子指令:用于各種同步鎖

單雙浮點指令:實現(xiàn)浮點運算操作

從上表我們可以看到,RISC-V 指令集具有模塊化特點。這就允許我們根據(jù)自己的需求,選擇一個基礎(chǔ)指令集,加上若干個擴(kuò)展指令集靈活搭配,就可以得到我們想要的指令集架構(gòu),進(jìn)而根據(jù)這樣的指令架構(gòu),設(shè)計出貼合我們需求的CPU.

作為初學(xué)者,我們了解RISC-V 的核心即可。它的最核心部分是一個基礎(chǔ)指令集,叫做RV32I.

RV32I 包含的指令是固定不變的,這為編譯器設(shè)計人員,操作系統(tǒng)開發(fā)人員和匯編語言程序員提供了穩(wěn)定的基礎(chǔ)框架。

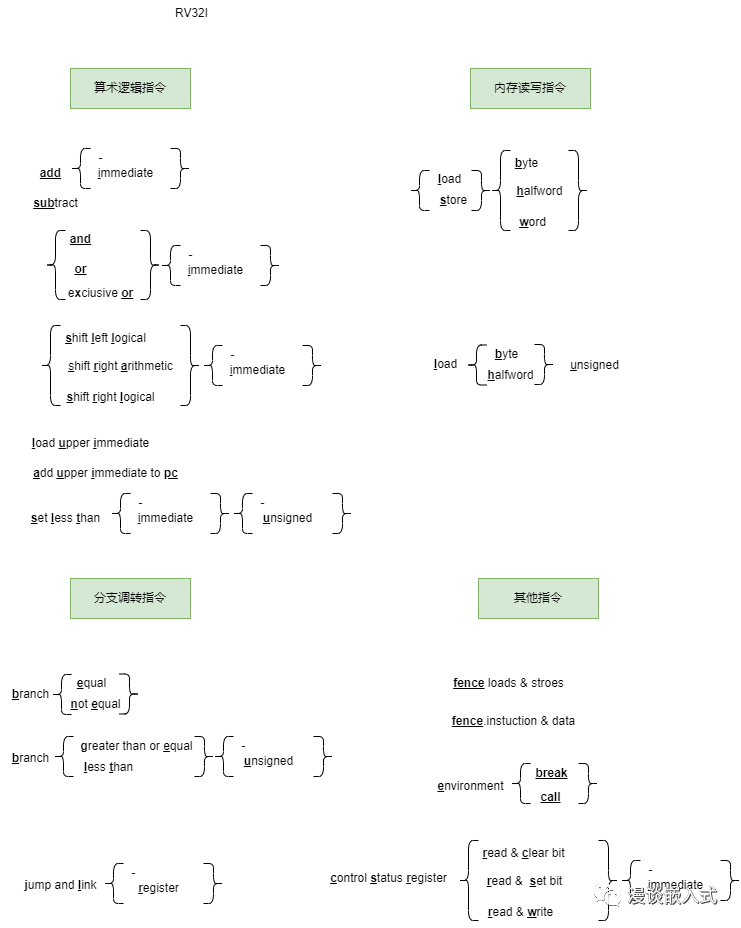

RV32I 指令集:

RV32I 指令集如圖所示,把帶下劃線的字母從左至右連接組合就是組成了RV32I指令。{}表示集合中垂直方向的每個項目指令不同變體。變體用下劃線字母或者下劃線表示表示,如果大括號里面只有下劃線,則表示對此變體不需要用字母表示

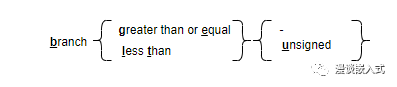

我們結(jié)合具體例子來看:下圖表示了bge、blt、bgeu、bltu四個指令。

3. 指令格式

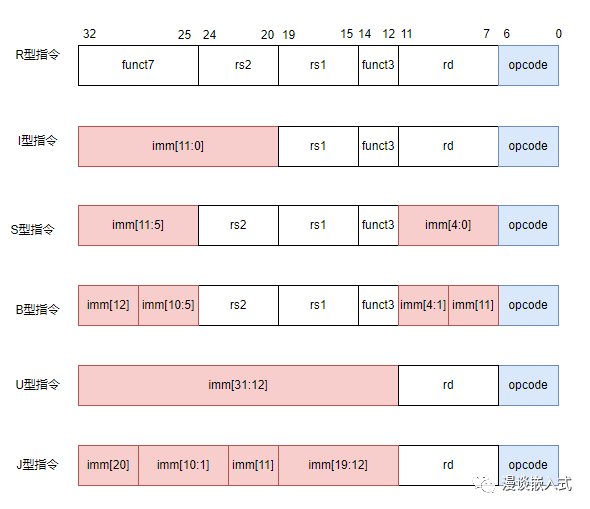

下圖是RISC-V 指令格式,從下圖可以看到RSIC-V共六種指令格式。

opcode :指令操作碼

imm:代碼立即數(shù)

func3和funct7:代表指令對應(yīng)的功能

rs1:源寄存器1

rs2:源寄存器2

rd:目標(biāo)寄存器(RSIC-V 一個指令可以提供三個寄存器操作)

六種指令格式作用如下:

| 序號 | 指令類型 | 作用 |

|---|---|---|

| 1 | R 型指令 | 用于寄存器和寄存器操作 |

| 2 | I 型指令 | 用于短立即數(shù)和內(nèi)存載入指令load操作 |

| 3 | S 型指令 | 用于內(nèi)存存儲store操作 |

| 4 | B 型指令 | 用于有條件跳轉(zhuǎn)操作 |

| 5 | U 型指令 | 用于長立即數(shù)操作 |

| 6 | J 型指令 | 用于無條件跳轉(zhuǎn)操作 |

4.寄存器

在RISC-V 的規(guī)范里面定義了32 個通用寄存器。其中31個是常規(guī)寄存器,1個恒為0值的x0寄存器。

0值寄存器是為了滿足匯編語言程序員和編譯器編寫者的使用需要,他們可以使用x0寄存器作為操作數(shù),來完成功能相同的操作。

addix0,x0,0;0=0+0,相當(dāng)于nop空指令

RSIC-V 寄存器說明

| 寄存器 | ABI 名稱 | 說明 |

|---|---|---|

| x0 | zero | 0值寄存器,硬編碼為0,寫入數(shù)據(jù)忽略,讀取數(shù)據(jù)為0 |

| x1 | ra | 用于返回地址(return address) |

| x2 | sp | 用于棧指針(stack pointer) |

| x3 | gp | 用于通用指針 (global pointer) |

| x4 | tp | 用于線程指針 (thread pointer) |

| x5 | t0 | 用于存放臨時數(shù)據(jù)或者備用鏈接寄存器 |

| x6~x7 | t1~t2 | 用于存放臨時數(shù)據(jù)寄存器 |

| x8 | s0/fp | 需要保存的寄存器或者幀指針寄存器 |

| x9 | s1 | 需要保存的寄存器 |

| x10~x11 | a0~a1 | 函數(shù)傳遞參數(shù)寄存器或者函數(shù)返回值寄存器 |

| x12~x17 | a2~a7 | 函數(shù)傳遞參數(shù)寄存器 |

| x18~x27 | s2-s11 | 需要保存的寄存器 |

| x28~x31 | t3~t6 | 用于存放臨時數(shù)據(jù)寄存器 |

5. RV32I 指令解讀

5.1 算術(shù)與邏輯指令

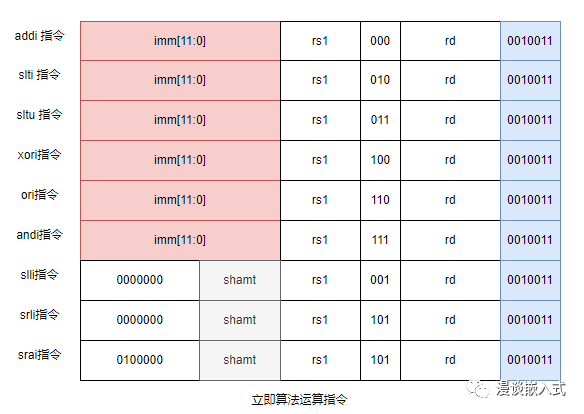

在RV32I 中包括算術(shù)指令(add/sub)、數(shù)值比較指令(slt)、邏輯指令(and/or/xor)以及移位指令(sll/srl/sra)這幾種指令。

這些指令和其他指令集差不多,它們從寄存器讀取兩個32位的值,并將32位運算結(jié)果再寫回到目標(biāo)寄存器。

I型指令:立即數(shù)算術(shù)運算

R型指令:寄存器與寄存器操作指令

需要指出的是,在寄存器與寄存器操作的算術(shù)指令中。必須要有減法指令。這和立即數(shù)操作指令不同。

5.2 Load 和 Store 指令

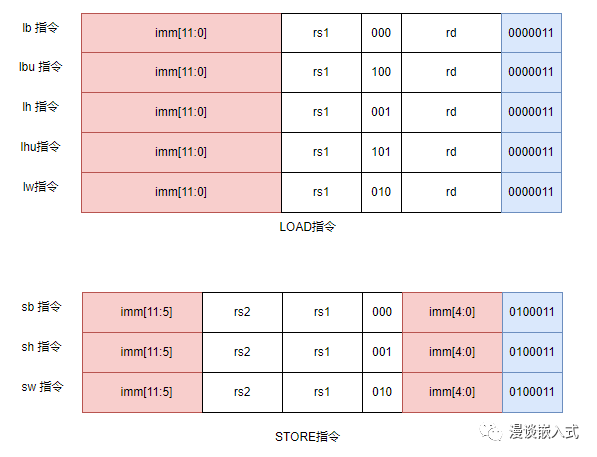

在RISC-V 指令集中,對內(nèi)存的讀寫只能通過LOAD 和 STORE 指令實現(xiàn)。而其他的指令只能以寄存器為操作對象。

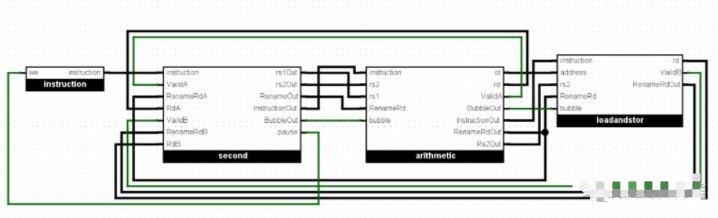

如上圖所示,load 和 store 的尋址模式只能是符號擴(kuò)展12位的立即數(shù),加上基地址寄存器得到訪存的存儲器地址。因為沒有了復(fù)雜的內(nèi)存尋址方式,這讓CPU 流水線可以對數(shù)據(jù)沖突提前做出判斷,并通過流水線各級轉(zhuǎn)送加以處理,而不需要加入空操作(NOP),極大的提高了代碼的執(zhí)行效率。

5.3 分支跳轉(zhuǎn)指令

5.3.1 有條件的分支跳轉(zhuǎn)

RV32I 中的條件跳轉(zhuǎn)就是通過比較兩個寄存器的值,進(jìn)行分支跳轉(zhuǎn):

beq:相等

bne:不相等

bge/bgeu:大于等于

blt/bltu:小于

5.3.2 無條件的分支跳轉(zhuǎn)

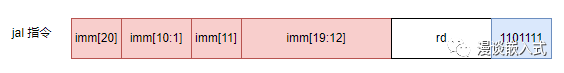

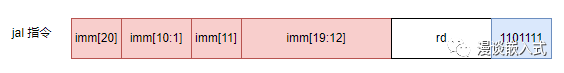

無條件跳轉(zhuǎn)指令可以細(xì)分為直接跳轉(zhuǎn)和間接跳轉(zhuǎn)。直接跳轉(zhuǎn)指令JAL 如下圖所示:

JAL 指令執(zhí)行過程是這樣的。它會把20位立即數(shù)做符號位擴(kuò)展。并左移一位,產(chǎn)生一個32位符號數(shù)。然后,將該32位符號數(shù)和PC相加來產(chǎn)生目標(biāo)地址(這樣,JAL 可以作為短跳轉(zhuǎn)指令,跳至PC+1MB的地址范圍內(nèi))

同時JAL 會把緊隨其后的那條指令地址,存入目標(biāo)寄存器中。這樣,如果目標(biāo)寄存器是零,則JAL就等同GOTO指令;如果目標(biāo)寄存器不為零,JAL可以實現(xiàn)函數(shù)調(diào)用功能。

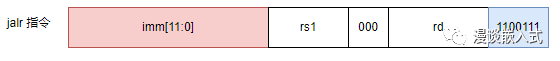

間接跳轉(zhuǎn)直接JALR如下:

JALR指令會把12位立即數(shù)和源寄存器相加,并把相加結(jié)果末位清零,作為新的跳轉(zhuǎn)地址。同時和JAL指令一樣,也會把緊隨其后的那條指令地址,存入目標(biāo)寄存器中。

5.4 其他指令

除了內(nèi)存地址空間和通用寄存器地址空間外,RISC-V 還定義了一個獨立的控制和狀態(tài)寄存器地址空間(Control Status Register)每個處理器實現(xiàn)的CSR會因設(shè)計目標(biāo)不同而有差異,但是這些CSR的訪問方式卻是一樣的,訪問這些CSR指令定義在了用戶指令集中(Zicsr指令集擴(kuò)展)

有了上圖這些CSR 指令,能夠讓我們輕松的訪問一些程序性能計數(shù)器。這些計數(shù)器包括系統(tǒng)時間、時間周期以及執(zhí)行的指令數(shù)目。

-

cpu

+關(guān)注

關(guān)注

68文章

11080瀏覽量

217145 -

接口

+關(guān)注

關(guān)注

33文章

9005瀏覽量

153778 -

指令集

+關(guān)注

關(guān)注

0文章

228瀏覽量

23818 -

RISC-V

+關(guān)注

關(guān)注

46文章

2574瀏覽量

48855

原文標(biāo)題:RISC-V 指令詳解

文章出處:【微信號:strongerHuang,微信公眾號:strongerHuang】歡迎添加關(guān)注!文章轉(zhuǎn)載請注明出處。

發(fā)布評論請先 登錄

正式的RISC-V基礎(chǔ)指令集架構(gòu)與特權(quán)架構(gòu)規(guī)范來了,RISC-V基金會已正式批準(zhǔn)

淺談RISC-V指令集架構(gòu)的來龍去脈

【RISC-V開放架構(gòu)設(shè)計之道|閱讀體驗】RISC-V基礎(chǔ)整數(shù)指令集

RISC-V指令集的特點總結(jié)

RISC-V和arm指令集的對比分析

RISC-V的指令集位寬的幾點學(xué)習(xí)心得

RISC-V架構(gòu)簡介

什么是RISC-V? RISC-V指令具有哪些特點應(yīng)用?

RISC-V指令集架構(gòu)微控制器相關(guān)知識

risc-v中國峰會直播:如何優(yōu)化RISC-V指令集架構(gòu)的代碼密度?

RISC-V指令集架構(gòu)特點

RISC-V指令集架構(gòu)特點

評論