FPGA發(fā)展到今天,SerDes(Serializer-Deserializer)基本上是標(biāo)配了。從PCI到PCI Express, 從ATA到SATA,從并行ADC接口到JESD204, 從RIO到Serial RIO,…等等,都是在借助SerDes來(lái)提高性能。SerDes是非常復(fù)雜的數(shù)模混合設(shè)計(jì),用戶(hù)手冊(cè)的內(nèi)容只是描述了森林里面的一棵小樹(shù),并不能夠解釋SerDes是怎么工作的。SerDes怎么可以沒(méi)有傳輸時(shí)鐘信號(hào)?什么是加重和均衡?抖動(dòng)和誤碼是什么關(guān)系?各種抖動(dòng)之間有什么關(guān)系?本篇小文試著從一個(gè)SerDes用戶(hù)的角度來(lái)理解SerDes是怎么設(shè)計(jì)的, 由于水平有限,一定有不夠準(zhǔn)確的地方,希望對(duì)剛開(kāi)始接觸SerDes的工程師有所幫助。

Contents 1.SerDes的價(jià)值 1.1并行總線接口 1.2 SerDes接口 1.3 中間類(lèi)型 2. SerDes結(jié)構(gòu)(architecture) 2.1串行器解串器(Serializer/Deserializer) 2.2發(fā)送端均衡器( Tx Equalizer) 2.3接收端均衡器( Rx Equalizer) 2.4時(shí)鐘數(shù)據(jù)恢復(fù)(CDR) 2.5公用鎖相環(huán)(PLL) 2.6 SerDes編解碼 2.7 SerDes收發(fā)Driver及差分接口轉(zhuǎn)換 2.8 SerDes環(huán)回和調(diào)試 3.抖動(dòng)和信號(hào)集成( Jitter, SI ) 3.1 時(shí)鐘的抖動(dòng)(clock jitter) 3.2. 數(shù)據(jù)的抖動(dòng)(data jitter) 4.信號(hào)集成(SI)及仿真 4.1信道channel 4.2 芯片封裝Package 4.3 SI仿真 5. 結(jié)尾

1.SerDes的價(jià)值

1.1并行總線接口

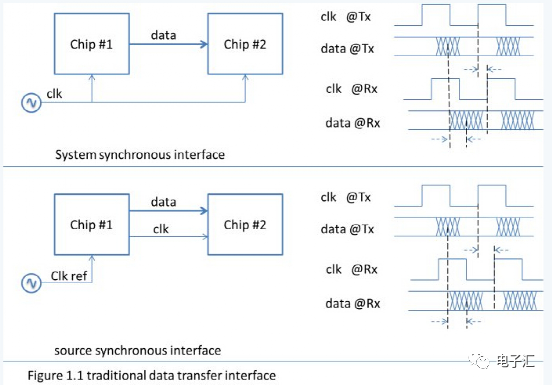

在SerDes流行之前,芯片之間的互聯(lián)通過(guò)系統(tǒng)同步或者源同步的并行接口傳輸數(shù)據(jù),圖1.1演示了系統(tǒng)和源同步并行接口。  隨著接口頻率的提高,在系統(tǒng)同步接口方式中,有幾個(gè)因素限制了 有效數(shù)據(jù)窗口寬度 的繼續(xù)增加。 時(shí)鐘到達(dá)兩個(gè)芯片的傳播延時(shí)不相等(clock skew) 并行數(shù)據(jù)各個(gè)bit的傳播延時(shí)不相等(data skew) 時(shí)鐘的傳播延時(shí)和數(shù)據(jù)的傳播延時(shí)不一致(skew between data and clock)

隨著接口頻率的提高,在系統(tǒng)同步接口方式中,有幾個(gè)因素限制了 有效數(shù)據(jù)窗口寬度 的繼續(xù)增加。 時(shí)鐘到達(dá)兩個(gè)芯片的傳播延時(shí)不相等(clock skew) 并行數(shù)據(jù)各個(gè)bit的傳播延時(shí)不相等(data skew) 時(shí)鐘的傳播延時(shí)和數(shù)據(jù)的傳播延時(shí)不一致(skew between data and clock)

雖然可以通過(guò)在目的芯片(chip #2)內(nèi)用PLL補(bǔ)償時(shí)鐘延時(shí)差(clock skew),但是PVT變化時(shí),時(shí)鐘延時(shí)的變化量和數(shù)據(jù)延時(shí)的變化量是不一樣的。這又進(jìn)一步惡化了數(shù)據(jù)窗口。 源同步接口方式中,發(fā)送側(cè)Tx把時(shí)鐘伴隨數(shù)據(jù)一起發(fā)送出去, 限制了clock skew對(duì)有效數(shù)據(jù)窗口的危害。通常在發(fā)送側(cè)芯片內(nèi)部,源同步接口把時(shí)鐘信號(hào)和數(shù)據(jù)信號(hào)作一樣的處理,也就是讓它和數(shù)據(jù)信號(hào)經(jīng)過(guò)相同的路徑,保持相同的延時(shí)。這樣PVT變化時(shí),時(shí)鐘和數(shù)據(jù)會(huì)朝著同一個(gè)方向增大或者減小相同的量,對(duì)skew最有利。 我們來(lái)做一些合理的典型假設(shè),假設(shè)一個(gè)32bit數(shù)據(jù)的并行總線, a)發(fā)送端的數(shù)據(jù)skew = 50 ps---很高的要求

b)pcb走線引入的skew = 50ps---很高的要求

c)時(shí)鐘的周期抖動(dòng)jitter = +/-50 ps ---很高的要求

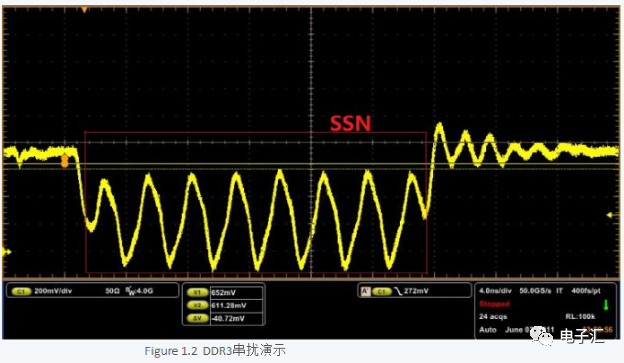

d)接收端觸發(fā)器采樣窗口 = 250 ps---Xilinx V7高端器件的IO觸發(fā)器 可以大致估計(jì)出并行接口的最高時(shí)鐘 = 1/(50+50+100+250) = 2.2GHz (DDR)或者1.1GHz (SDR)。 利用源同步接口,數(shù)據(jù)的有效窗口可以提高很多。通常頻率都在1GHz以下。在實(shí)際應(yīng)用中可以見(jiàn)到如SPI4.2接口的時(shí)鐘可以高達(dá)DDR 700MHz x 16bits位寬。DDR Memory接口也算一種源同步接口,如DDR3在FPGA中可以做到大約800MHz的時(shí)鐘。 要提高接口的傳輸帶寬有兩種方式,一種是提高時(shí)鐘頻率,一種是加大數(shù)據(jù)位寬。那么是不是可以無(wú)限制的增加數(shù)據(jù)的位寬呢?這就要牽涉到另外一個(gè)非常重要的問(wèn)題-----同步切換噪聲(SSN)。 這里不討論SSN的原理,直接給出SSN的公式 SSN = L *N* di/dt。L是芯片封裝電感,N是數(shù)據(jù)寬度,di/dt是電流變化的斜率。隨著頻率的提高,數(shù)據(jù)位款的增加,SSN成為提高傳輸帶寬的主要瓶頸。圖1.2是一個(gè)DDR3串?dāng)_的例子。圖中低電平的理論值在0V,由于SSN的影響,低電平表現(xiàn)為震蕩,震蕩噪聲的最大值達(dá)610mV,因此噪聲余量只有1.5V/2-610mV=140mV。

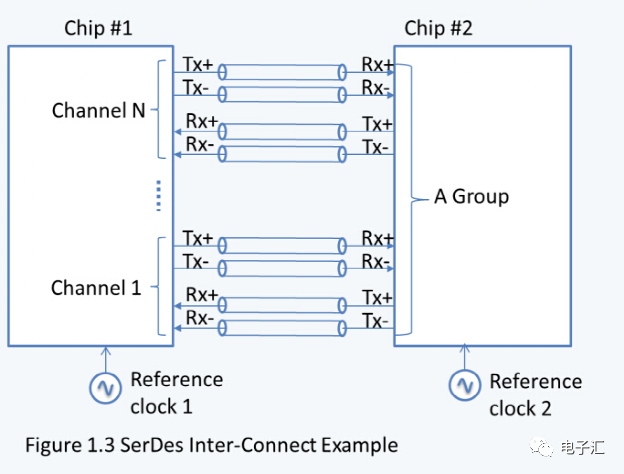

Figure 1.2DDR3串?dāng)_演示 因此也不可能靠無(wú)限的提高數(shù)據(jù)位寬來(lái)繼續(xù)增加帶寬。一種解決SSN的辦法是使用差分信號(hào)替代單端信號(hào),使用差分信號(hào)可以很好的解決SSN問(wèn)題,代價(jià)是使用更多的芯片引腳。使用差分信號(hào)仍然解決不了數(shù)據(jù)skew的問(wèn)題,很大位寬的差分信號(hào)再加上嚴(yán)格的時(shí)序限制,給并行接口帶來(lái)了很大的挑戰(zhàn)。 1.2 SerDes接口 源同步接口的時(shí)鐘頻率已經(jīng)遇到瓶頸,由于信道的非理想(channel)特性,再繼續(xù)提高頻率,信號(hào)會(huì)被嚴(yán)重?fù)p傷,就需要采用均衡和數(shù)據(jù)時(shí)鐘相位檢測(cè)等技術(shù)。這也就是SerDes所采用的技術(shù)。SerDes(Serializer-Deserializer)是串行器和解串器的簡(jiǎn)稱(chēng)。串行器(Serializer)也稱(chēng)為SerDes發(fā)送端(Tx),(Deserializer)也稱(chēng)為接收端Rx。Figure1.3是一個(gè)N對(duì)SerDes收發(fā)通道的互連演示,一般N小于4。

可以看到,SerDes不傳送時(shí)鐘信號(hào),這也是SerDes最特別的地方,SerDes在接收端集成了CDR(Clock Data Recovery)電路,利用CDR從數(shù)據(jù)的邊沿信息中抽取時(shí)鐘,并找到最優(yōu)的采樣位置。 SerDes采用差分方式傳送數(shù)據(jù)。一般會(huì)有多個(gè)通道的數(shù)據(jù)放在一個(gè)group中以共享PLL資源,每個(gè)通道仍然是相互獨(dú)立工作的。 SerDes需要參考時(shí)鐘(Reference Clock),一般也是差分的形式以降低噪聲。接收端Rx和發(fā)送端Tx的參考時(shí)鐘可以允許幾百個(gè)ppm的頻差(plesio-synchronous system),也可以是同頻的時(shí)鐘,但是對(duì)相位差沒(méi)有要求。 作個(gè)簡(jiǎn)單的比較,一個(gè)SerDes通道(channel)使用4個(gè)引腳(Tx+/-,Rx+/-), 目前的FPGA可以做到高達(dá)28Gbps。而一個(gè)16bits的DDR3-1600的線速率為1.6Gbps*16 = 25Gbps,卻需要50個(gè)引腳。此對(duì)比可以看出SerDes在傳輸帶寬上的優(yōu)勢(shì)。 相比源同步接口,SerDes的主要特點(diǎn)包括: l SerDes在數(shù)據(jù)線中時(shí)鐘內(nèi)嵌,不需要傳送時(shí)鐘信號(hào)。

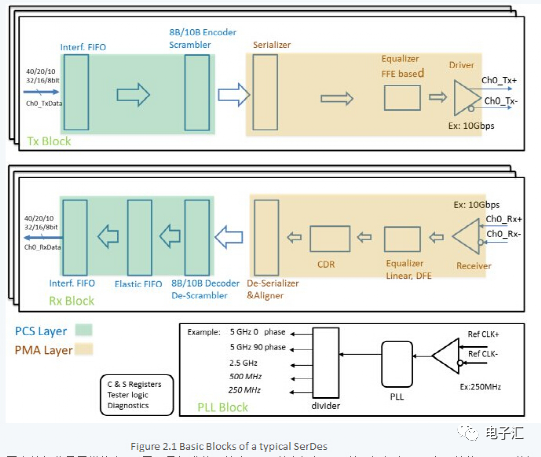

l SerDes通過(guò)加重/均衡技術(shù)可以實(shí)現(xiàn)高速長(zhǎng)距離傳輸,如背板。 lSerDes 使用了較少的芯片引腳 1.3中間類(lèi)型 也存在一些介于SerDes和并行接口之間的接口類(lèi)型,相對(duì)源同步接口而言,這些中間類(lèi)型的接口也使用串行器(Serializer)解串器(Deserializer),同時(shí)也傳送用于同步的時(shí)鐘信號(hào)。這類(lèi)接口如視頻顯示接口7:1 LVDS等。 2. SerDes結(jié)構(gòu)(architecture) SerDes的主要構(gòu)成可以分為三部分,PLL模塊,發(fā)送模塊Tx,接收模塊Rx。為了方便維護(hù)和測(cè)試,還會(huì)包括控制和狀態(tài)寄存器,環(huán)回測(cè)試,PRBS測(cè)試等功能。見(jiàn)圖2.1。

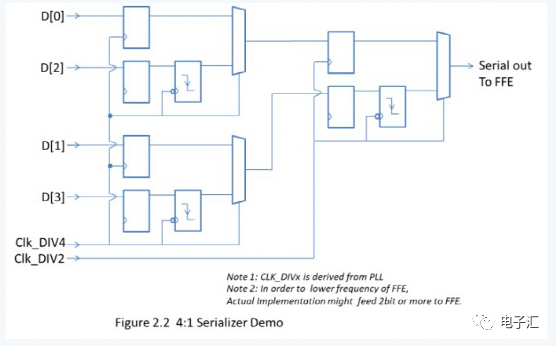

Figure 2.1 Basic Blocks of a typical SerDes 圖中藍(lán)色背景子模塊為PCS層,是標(biāo)準(zhǔn)的可綜合CMOS數(shù)字邏輯,可以硬邏輯實(shí)現(xiàn),也可以使用FPGA軟邏輯實(shí)現(xiàn),相對(duì)比較容易被理解。褐色背景的子模塊是PMA層,是數(shù)模混合CML/CMOS電路,是理解SerDes去別于并行接口的關(guān)鍵,也是本文要討論的內(nèi)容。 發(fā)送方向(Tx)信號(hào)的流向: FPGA軟邏輯(fabric)送過(guò)來(lái)的并行信號(hào),通過(guò)接口FIFO(Interface FIFO), 送給8B/10B編碼器(8B/10B encoder)或擾碼器(scambler),以避免數(shù)據(jù)含有過(guò)長(zhǎng)連零或者連1。之后送給串行器(Serializer)進(jìn)行 并->串 轉(zhuǎn)換。串行數(shù)據(jù)經(jīng)過(guò)均衡器(equalizer)調(diào)理,有驅(qū)動(dòng)器(driver)發(fā)送出去。 接收方向(Rx)信號(hào)的流向, 外部串行信號(hào)由線性均衡器(Linear Equalizer)或DFE (Decision Feedback Equalizer)結(jié)構(gòu)均衡器調(diào)理,去除一部分確定性抖動(dòng)(Deterministic jitter)。CDR從數(shù)據(jù)中恢復(fù)出采樣時(shí)鐘,經(jīng)解串器變?yōu)閷?duì)齊的并行信號(hào)。8B/10B解碼器(8B/10B decoder)或解擾器(de-scambler)完成解碼或者解擾。如果是異步時(shí)鐘系統(tǒng)(plesio-synchronous system),在用戶(hù)FIFO之前還應(yīng)該有彈性FIFO來(lái)補(bǔ)償頻差。 PLL負(fù)責(zé)產(chǎn)生SerDes各個(gè)模塊所需要的時(shí)鐘信號(hào),并管理這些時(shí)鐘之間的相位關(guān)系。以圖中線速率10Gbps為例,參考時(shí)鐘頻率250MHz。Serializer/Deserializer至少需要5GHz 0相位時(shí)鐘和5GHz 90度相位時(shí)鐘,1GHz(10bit并行)/1.25GHz(8bit并行)時(shí)鐘等。 一個(gè)SerDes通常還要具調(diào)試能力。例如偽隨機(jī)碼流產(chǎn)生和比對(duì),各種環(huán)回測(cè)試,控制狀態(tài)寄存器以及訪問(wèn)接口,LOS檢測(cè), 眼圖測(cè)試等。 2.1串行器解串器(Serializer/Deserializer) 串行器Serializer把并行信號(hào)轉(zhuǎn)化為串行信號(hào)。Deserializer把串行信號(hào)轉(zhuǎn)化為并行信號(hào)。一般地,并行信號(hào)為8 /10bit或者16/20bit寬度,串行信號(hào)為1bit寬度(也可以分階段串行化,如8bit->4bit->2bit->equalizerà1bit以降低equalizer的工作頻率)。采用擾碼(scrambled)的協(xié)議如SDH/SONET, SMPTE SDI使用8/16bit的并行寬度,采用8B/10B編碼的協(xié)議如PCIExpress,GbE使用10bits/20bits寬度。 一個(gè)4:1的串行器如圖xxx所示。8:1或16:1的串行器采用類(lèi)似的實(shí)現(xiàn)。實(shí)現(xiàn)時(shí),為了降低均衡器的工作頻率,串行器會(huì)先把并行數(shù)據(jù)變?yōu)?bits,送給均衡器equalizer濾波,最后一步再作2:1串行化,本文后面部分都按1bit串行信號(hào)解釋。

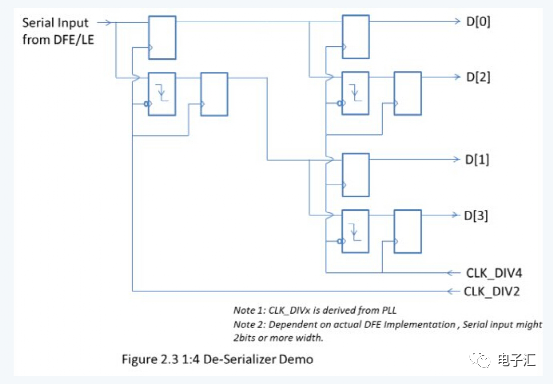

一個(gè)1:4的解串器如圖2.3所示,8:1或16:1的解串器采用類(lèi)似的實(shí)現(xiàn)。實(shí)現(xiàn)時(shí),為了降低均衡器(DFE based Equalizer)的工作頻率,DFE工作在DDR模式下,解串器的輸入是2bit或者更寬,本文后面部分都按1bit串行信號(hào)解釋。

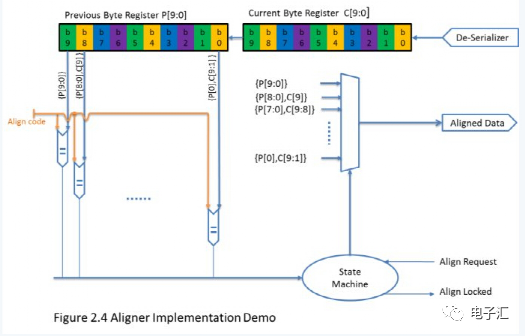

Serializer/Deserializer的實(shí)現(xiàn)采用雙沿(DDR)的工作方式,利用面積換速度的策略,降低了電路中高頻率電路的比例,從而降低了電路的噪聲。 接收方向除了Deserializer之外,一般帶有還有對(duì)齊功能邏輯(Aligner)。相對(duì)SerDes發(fā)送端,SerDes接收端起始工作的時(shí)刻是任意的,接收器正確接收的第一個(gè) bit可能是發(fā)送并行數(shù)據(jù)的任意bit位置。因此需要對(duì)齊邏輯來(lái)判斷從什么bit位置開(kāi)始,以組成正確的并行數(shù)據(jù)。對(duì)齊邏輯通過(guò)在串行數(shù)據(jù)流中搜索特征碼字(Alignment Code)來(lái)決定串并轉(zhuǎn)換的起始位置。比如8B/10B編碼的協(xié)議通常用K28.5(正碼10’b1110000011,負(fù)碼10’b0001111100)來(lái)作為對(duì)齊字。圖2.4為一個(gè)對(duì)齊邏輯的演示。通過(guò)滑窗,逐bit比對(duì),以找到對(duì)齊碼(Align-Code)的位置,經(jīng)過(guò)多次在相同的位置找到對(duì)齊碼之后,狀態(tài)機(jī)鎖定位置并選擇相應(yīng)的位置輸出對(duì)齊數(shù)據(jù)。

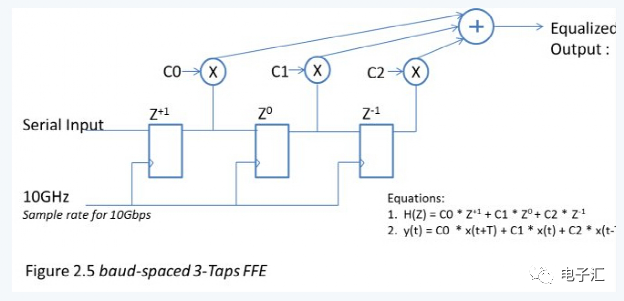

2.2發(fā)送端均衡器( Tx Equalizer) SerDes信號(hào)從發(fā)送芯片到達(dá)接收芯片所經(jīng)過(guò)的路徑稱(chēng)為信道(channel),包括芯片封裝,pcb走線,過(guò)孔,電纜,連接器等元件。從頻域看,信道可以簡(jiǎn)化為一個(gè)低通濾波器(LPF)模型,如果SerDes的速率大于信道(channel)的截止頻率,就會(huì)一定程度上損傷(distort)信號(hào)。均衡器的作用就是補(bǔ)償信道對(duì)信號(hào)的損傷。 發(fā)送端的均衡器采用FFE(Feed forward equalizers)結(jié)構(gòu),發(fā)送端的equalizer也稱(chēng)作加重器(emphasis)。加重(Emphasis)分為去加重(de-emphasis)和預(yù)加重(pre-emphasis)。De-emphasis降低差分信號(hào)的擺幅(swing)。Pre-emphasis增加差分信號(hào)的擺幅。FPGA大部分使用de-emphasis的方式,加重越強(qiáng),信號(hào)的平均幅度會(huì)越小。 發(fā)送側(cè)均衡器設(shè)計(jì)為一個(gè)高通濾波器(HPF),大致為信道頻響H(f)的反函數(shù)H-1(f),F(xiàn)FE的目標(biāo)是讓到達(dá)接收端的信號(hào)為一個(gè)干凈的信號(hào)。FFE的實(shí)現(xiàn)方式有很多,一個(gè)典型的例子如圖2.5所示。

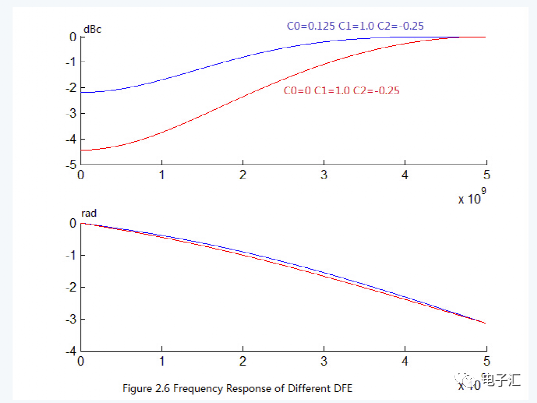

調(diào)節(jié)濾波器的系數(shù)可以改變?yōu)V波器的頻響,以補(bǔ)償不同的信道特性,一般可以動(dòng)態(tài)配置。以10Gbps線速率為例,圖2.5為DFE頻率響應(yīng)演示。可以看到,對(duì)于C0=0,C1=1.0,C2=-0.25的配置,5GHz處高頻增益比低頻區(qū)域高出4dB,從而補(bǔ)償信道對(duì)高頻頻譜的衰減。

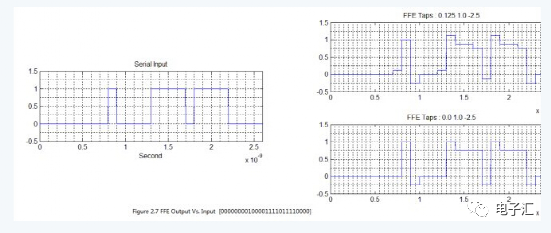

采樣時(shí)鐘的頻率限制了這種FFE最高只能補(bǔ)償?shù)紽s/2(例子中Fs/2=5GHz)。根據(jù)采樣定理,串行數(shù)據(jù)里的信息都包含在5GHz以?xún)?nèi),從這個(gè)角度看也就足夠了。如果要補(bǔ)償Fs/2以上的頻率,就要求FFE高于Fs的工作時(shí)鐘,或者連續(xù)時(shí)間域?yàn)V波器(Continuous Time FFE)。 圖2.7為DFE時(shí)域?yàn)V波效果的演示,以10Gbps線速率為例,一個(gè)UI=0.1 nS=100ps。演示的串行數(shù)據(jù)碼流為二進(jìn)制[00000000100001111011110000]。  2.3接收端均衡器( Rx Equalizer) 2.3.1?線形均衡器(Linear Equalizer) www.blog.sina.com.cn/fpgatalk 接收端均衡器的目標(biāo)和發(fā)送均衡器是一致的。對(duì)于低速(<5Gbps)SerDes,通常采用連續(xù)時(shí)間域,線性均衡器實(shí)現(xiàn)如尖峰放大器(peaking amplifier),?均衡器對(duì)高頻分量的增益大于對(duì)低頻分量的增益。圖2.8為一個(gè)線性均衡器的頻域特性。通常工廠會(huì)對(duì)均衡特性封裝為數(shù)種級(jí)別,可以動(dòng)態(tài)設(shè)置,以適應(yīng)不同的信道特性,如High/Med/Low等。

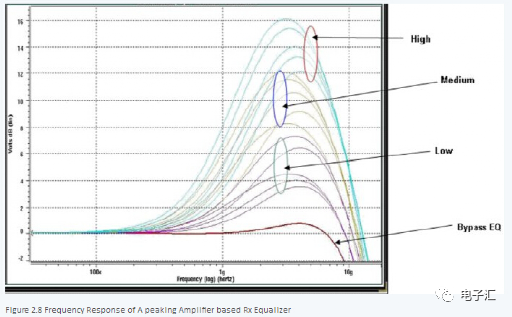

2.3接收端均衡器( Rx Equalizer) 2.3.1?線形均衡器(Linear Equalizer) www.blog.sina.com.cn/fpgatalk 接收端均衡器的目標(biāo)和發(fā)送均衡器是一致的。對(duì)于低速(<5Gbps)SerDes,通常采用連續(xù)時(shí)間域,線性均衡器實(shí)現(xiàn)如尖峰放大器(peaking amplifier),?均衡器對(duì)高頻分量的增益大于對(duì)低頻分量的增益。圖2.8為一個(gè)線性均衡器的頻域特性。通常工廠會(huì)對(duì)均衡特性封裝為數(shù)種級(jí)別,可以動(dòng)態(tài)設(shè)置,以適應(yīng)不同的信道特性,如High/Med/Low等。

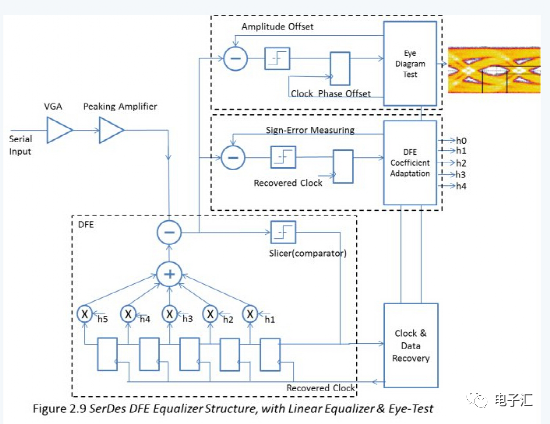

Figure 2.8 Frequency Response of A peaking Amplifier based Rx Equalizer 2.3.2 DFE均衡器(Decision Feedback Equalizer) 對(duì)于高速(>5Gbps)SerDes,由于信號(hào)的抖動(dòng)(如ISI相關(guān)的確定性抖動(dòng))可能會(huì)超過(guò)或接近一個(gè)符號(hào)間隔(UI, Unit Interval), 單單使用線性均衡器不再適用。線性均衡器對(duì)噪聲和信號(hào)一起放大,并沒(méi)有改善SNR或者說(shuō)BER。對(duì)于高速SerDes,采用一種稱(chēng)作DFE (Decision Feedback Equalizer)的非線性均衡器。DFE通過(guò)跟蹤過(guò)去多個(gè)UI的數(shù)據(jù)(history bits)來(lái)預(yù)測(cè)當(dāng)前bit的采樣門(mén)限。DFE只對(duì)信號(hào)放大,不對(duì)噪聲放大,可以有效改善SNR。 圖2.9演示了一個(gè)典型的5階DFE。接收的串行數(shù)據(jù)由比較器(slicer)來(lái)判決0或者1,然后數(shù)據(jù)流由一個(gè)濾波器來(lái)預(yù)測(cè)碼間干擾(ISI),再?gòu)妮斎氲脑夹盘?hào)中減掉碼間干擾(ISI),從而的到一個(gè)干凈的信號(hào)。為了讓DFE均衡器的電路工作在電路線形范圍內(nèi),串行信號(hào)先經(jīng)過(guò)VGA自動(dòng)控制進(jìn)入DFE的信號(hào)幅度。  ? 為了理解DFE的工作原理,先來(lái)看一個(gè)10Gbps背板的脈沖響應(yīng),這個(gè)背板模型是matlab給出的一個(gè)基于實(shí)測(cè)的模型,具有典型特性。

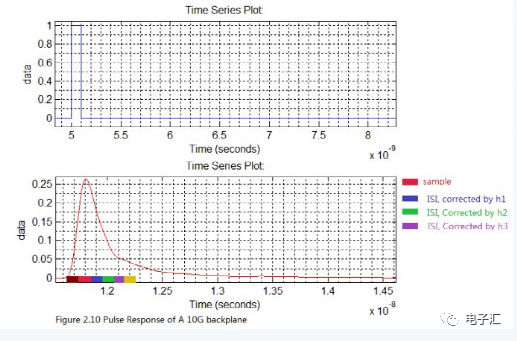

? 為了理解DFE的工作原理,先來(lái)看一個(gè)10Gbps背板的脈沖響應(yīng),這個(gè)背板模型是matlab給出的一個(gè)基于實(shí)測(cè)的模型,具有典型特性。 圖2.10中,一橫格代表一個(gè)UI的時(shí)間。可以看出,一個(gè)UI( 0.1nS = 1/10GHz )的脈沖信號(hào),通過(guò)背板后,泄漏到前后多個(gè)相鄰的UI里面,從而對(duì)其他UI的數(shù)據(jù)產(chǎn)生干擾。采樣點(diǎn)后面的干擾叫做post-cursor干擾,采樣點(diǎn)前面的叫做pre-cursor干擾。DFE的第一個(gè)系數(shù) h1(此例中0.175)矯正第一個(gè)post-cursor, 第二個(gè)系數(shù) h2(此例中0.075)矯正第二個(gè)post-cursor。DFE的階數(shù)越多,能夠校正的post-cursor也越多。 ?

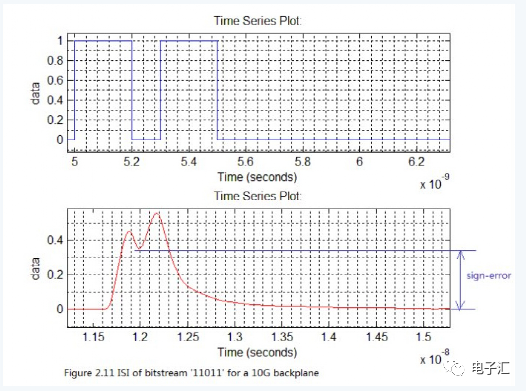

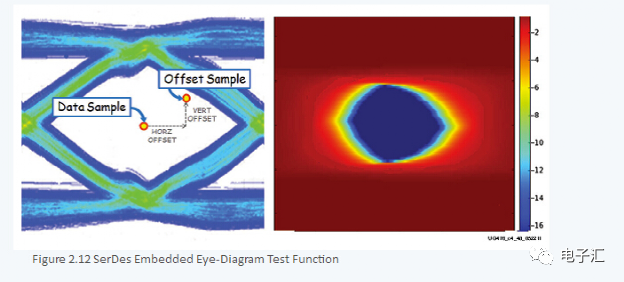

圖2.10中,一橫格代表一個(gè)UI的時(shí)間。可以看出,一個(gè)UI( 0.1nS = 1/10GHz )的脈沖信號(hào),通過(guò)背板后,泄漏到前后多個(gè)相鄰的UI里面,從而對(duì)其他UI的數(shù)據(jù)產(chǎn)生干擾。采樣點(diǎn)后面的干擾叫做post-cursor干擾,采樣點(diǎn)前面的叫做pre-cursor干擾。DFE的第一個(gè)系數(shù) h1(此例中0.175)矯正第一個(gè)post-cursor, 第二個(gè)系數(shù) h2(此例中0.075)矯正第二個(gè)post-cursor。DFE的階數(shù)越多,能夠校正的post-cursor也越多。 ?  用上述的背板傳輸一個(gè)11011的碼流,由于post-cursor和pre-cursor的泄漏,如果沒(méi)有均衡,將會(huì)導(dǎo)致’0’不能識(shí)別,見(jiàn)圖2.11。假定有一個(gè)2階的DFE,?那么‘0’bit處的幅度應(yīng)該減去第一個(gè)’1’bit的h2,第二個(gè)’1’bit的h1,?得到0.35-0.075-0.175 =0.1,?足夠被識(shí)別為0。 可見(jiàn),DFE計(jì)算歷史bits的post-cursor干擾,在當(dāng)前bit中把干擾減去,從而得到干凈的信號(hào)。由于DFE只能能夠校正post-cursor ISI,?所以DFE前面一般會(huì)帶有LE。只要DFE的系數(shù)接近信道(channel)的脈沖相應(yīng),就可以到的比較理想的結(jié)果。但是信道是一個(gè)時(shí)變的媒介,比如溫度電壓工藝的慢變化等因素會(huì)改變信道channel的特性。因此DFE的系數(shù)需要自適應(yīng)算法,自動(dòng)撲獲和跟隨信道的變化。DFE系數(shù)自適應(yīng)算法非常學(xué)術(shù),每個(gè)廠商的算法都是保密的,不對(duì)外公布。對(duì)于NRZ碼,典型的算法準(zhǔn)則是基于sign-error驅(qū)動(dòng)的算法。Sign-error是均衡后信號(hào)的幅度和期望值的誤差,算法以sign-error均方差最小為優(yōu)化目標(biāo),逐次優(yōu)化h1/h2/h3…。因?yàn)閟ign-error和采樣位置是耦合在一起相互影響,因此也可以sign-error和眼圖寬度兩個(gè)準(zhǔn)則為目標(biāo)進(jìn)行DFE系數(shù)的預(yù)測(cè)。也因此,采用DFE結(jié)構(gòu)的SerDes通常都會(huì)帶有內(nèi)嵌眼圖測(cè)試電路,如圖2.9所示。眼圖測(cè)試電路通過(guò)垂直方向上平移信號(hào)的幅度,水平方向上平移采樣位置,計(jì)算每一個(gè)平移位置上的誤碼率BER,從而得到每一個(gè)偏移位置與誤碼率關(guān)系的”眼圖”,見(jiàn)圖2.12。

用上述的背板傳輸一個(gè)11011的碼流,由于post-cursor和pre-cursor的泄漏,如果沒(méi)有均衡,將會(huì)導(dǎo)致’0’不能識(shí)別,見(jiàn)圖2.11。假定有一個(gè)2階的DFE,?那么‘0’bit處的幅度應(yīng)該減去第一個(gè)’1’bit的h2,第二個(gè)’1’bit的h1,?得到0.35-0.075-0.175 =0.1,?足夠被識(shí)別為0。 可見(jiàn),DFE計(jì)算歷史bits的post-cursor干擾,在當(dāng)前bit中把干擾減去,從而得到干凈的信號(hào)。由于DFE只能能夠校正post-cursor ISI,?所以DFE前面一般會(huì)帶有LE。只要DFE的系數(shù)接近信道(channel)的脈沖相應(yīng),就可以到的比較理想的結(jié)果。但是信道是一個(gè)時(shí)變的媒介,比如溫度電壓工藝的慢變化等因素會(huì)改變信道channel的特性。因此DFE的系數(shù)需要自適應(yīng)算法,自動(dòng)撲獲和跟隨信道的變化。DFE系數(shù)自適應(yīng)算法非常學(xué)術(shù),每個(gè)廠商的算法都是保密的,不對(duì)外公布。對(duì)于NRZ碼,典型的算法準(zhǔn)則是基于sign-error驅(qū)動(dòng)的算法。Sign-error是均衡后信號(hào)的幅度和期望值的誤差,算法以sign-error均方差最小為優(yōu)化目標(biāo),逐次優(yōu)化h1/h2/h3…。因?yàn)閟ign-error和采樣位置是耦合在一起相互影響,因此也可以sign-error和眼圖寬度兩個(gè)準(zhǔn)則為目標(biāo)進(jìn)行DFE系數(shù)的預(yù)測(cè)。也因此,采用DFE結(jié)構(gòu)的SerDes通常都會(huì)帶有內(nèi)嵌眼圖測(cè)試電路,如圖2.9所示。眼圖測(cè)試電路通過(guò)垂直方向上平移信號(hào)的幅度,水平方向上平移采樣位置,計(jì)算每一個(gè)平移位置上的誤碼率BER,從而得到每一個(gè)偏移位置與誤碼率關(guān)系的”眼圖”,見(jiàn)圖2.12。

Figure 2.12 SerDes Embedded Eye-Diagram Test Function 2.4時(shí)鐘數(shù)據(jù)恢復(fù)(CDR) CDR的目標(biāo)是找到最佳的采樣時(shí)刻,這需要數(shù)據(jù)有豐富的跳變。CDR有一個(gè)指標(biāo)叫做 最長(zhǎng)連0或連1長(zhǎng)度 容忍(Max Run Length或者Consecutive Identical Digits)能力。如果數(shù)據(jù)長(zhǎng)時(shí)間沒(méi)有跳變,CDR就無(wú)法得到精確的訓(xùn)練,CDR采樣時(shí)刻就會(huì)漂移,可能采到比真實(shí)數(shù)據(jù)更多的1或者0。而且當(dāng)數(shù)據(jù)重新恢復(fù)跳變的時(shí),有可能出現(xiàn)錯(cuò)誤的采樣。比如有的CDR采用PLL實(shí)現(xiàn),如果數(shù)據(jù)長(zhǎng)時(shí)間停止跳變,PLL的輸出頻率就會(huì)漂移。實(shí)際上,SerDes上傳輸?shù)臄?shù)據(jù)要么利用加擾,要么利用編碼的方法來(lái)保證Max Run Length在一定的范圍內(nèi)。 8B/10B編碼的方法可以保證Max Run Length不超過(guò)5個(gè)UI。

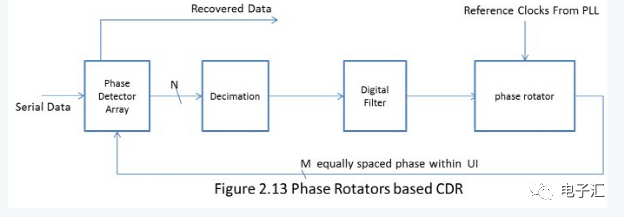

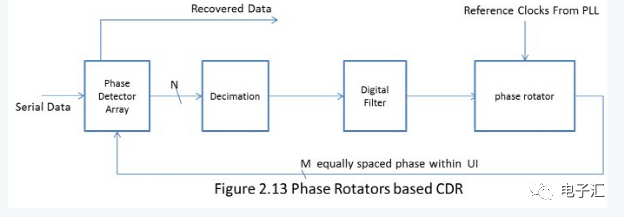

64B/66B編碼的方法可以保證Max Run Length不超過(guò)66個(gè)UI SONET/SDH加擾得方法可以保證Max Run Length不超過(guò)80個(gè)UI(BER<10^-12) 在點(diǎn)到點(diǎn)的連接中,大部分SerDes協(xié)議采用連續(xù)模式(continuous-mode),線路上數(shù)據(jù)流是持續(xù)而沒(méi)有中斷的。在點(diǎn)到多點(diǎn)的連接中,往往采用突發(fā)模式(burst-mode)如PON。很顯然Burst-Mode對(duì)SerDes鎖定時(shí)間有苛刻的要求。 Continuous-Mode的協(xié)議如SONET/SDH則要求容忍較長(zhǎng)的連0, 而且對(duì)CDR的抖動(dòng)傳輸性能也有嚴(yán)格的要求(因?yàn)閘oop timing)。 如果收(Rx)發(fā)(Tx)是異步模式(asynchronous mode),或者頻譜擴(kuò)展(SSC)應(yīng)用中,則要求CDR有較寬的相位跟蹤范圍以跟蹤Rx/Tx頻率差。 根據(jù)應(yīng)用場(chǎng)景的不同需求,CDR的實(shí)現(xiàn)也有非常多種架構(gòu)。FPGA SerDes常常采用的基于數(shù)字PLL的CDR,和基于相位插值器的CDR。這兩種CDR在環(huán)路中采用數(shù)字濾波器,相對(duì)模擬charge pump加模擬濾波器的結(jié)構(gòu)更節(jié)省面積。  ? 圖2.13是基于相位插值器的CDR。鑒相器陣列對(duì)輸入的串行數(shù)據(jù)與M個(gè)等相位間隔的時(shí)鐘在多個(gè)UI的跨度上進(jìn)行相位比較,得到多個(gè)UI跨度上的相位誤差信號(hào)。相位誤差信號(hào)的頻率很高,寬度也很寬,經(jīng)過(guò)抽取器降速并平滑后,送給數(shù)字濾波器。數(shù)字濾波器的性能會(huì)影響環(huán)路的帶寬,穩(wěn)定性,反應(yīng)速度等。經(jīng)數(shù)字濾波器平滑后的誤差信號(hào)送給相位插值器(phase rotators)修正時(shí)鐘相位。最終環(huán)路鎖定時(shí),理論上相位誤差為零,90度偏移的時(shí)鐘作為恢復(fù)時(shí)鐘采樣串行輸入。

? 圖2.13是基于相位插值器的CDR。鑒相器陣列對(duì)輸入的串行數(shù)據(jù)與M個(gè)等相位間隔的時(shí)鐘在多個(gè)UI的跨度上進(jìn)行相位比較,得到多個(gè)UI跨度上的相位誤差信號(hào)。相位誤差信號(hào)的頻率很高,寬度也很寬,經(jīng)過(guò)抽取器降速并平滑后,送給數(shù)字濾波器。數(shù)字濾波器的性能會(huì)影響環(huán)路的帶寬,穩(wěn)定性,反應(yīng)速度等。經(jīng)數(shù)字濾波器平滑后的誤差信號(hào)送給相位插值器(phase rotators)修正時(shí)鐘相位。最終環(huán)路鎖定時(shí),理論上相位誤差為零,90度偏移的時(shí)鐘作為恢復(fù)時(shí)鐘采樣串行輸入。 圖2.14是基于DPLL的CDR, 分為兩個(gè)環(huán)路,對(duì)數(shù)據(jù)鎖相的環(huán)路(phase tracking loop)和圖2.13的CDR工作原理類(lèi)似。鑒相器陣列對(duì)輸入的串行數(shù)據(jù)與M個(gè)等相位間隔的時(shí)鐘進(jìn)行相位比較(也可能是在多個(gè)UI的跨度上),得到相位誤差信號(hào)。相位誤差信號(hào)送給數(shù)字濾波器。數(shù)字濾波器的性能會(huì)影響環(huán)路的帶寬,穩(wěn)定性,反應(yīng)速度等。經(jīng)數(shù)字濾波器平滑后的誤差信號(hào)送給VCO修正時(shí)鐘相位。最終環(huán)路鎖定時(shí),理論上相位誤差為零,90度偏移的時(shí)鐘作為恢復(fù)時(shí)鐘采樣串行輸入。 基于DPLL的CDR多了一個(gè)頻率跟蹤環(huán)路(Frequency Tracking Loop)。這是為了減小CDR的鎖定時(shí)間,減少對(duì)環(huán)路濾波器的設(shè)計(jì)約束。只有當(dāng) 頻率跟蹤環(huán)路 鎖定后,才會(huì)切換到數(shù)據(jù) 相位跟蹤環(huán)路。相位跟蹤環(huán)路失鎖時(shí),再自動(dòng)切換到頻率跟蹤環(huán)路。N倍參考時(shí)鐘(Reference Clock)頻率 和 線路速率接近相等,因此兩個(gè)環(huán)路的VCO穩(wěn)態(tài)控制電壓是接近相等的。借助 頻率跟蹤環(huán)路,減小了 相位跟蹤環(huán)路 的捕獲時(shí)間。

圖2.14是基于DPLL的CDR, 分為兩個(gè)環(huán)路,對(duì)數(shù)據(jù)鎖相的環(huán)路(phase tracking loop)和圖2.13的CDR工作原理類(lèi)似。鑒相器陣列對(duì)輸入的串行數(shù)據(jù)與M個(gè)等相位間隔的時(shí)鐘進(jìn)行相位比較(也可能是在多個(gè)UI的跨度上),得到相位誤差信號(hào)。相位誤差信號(hào)送給數(shù)字濾波器。數(shù)字濾波器的性能會(huì)影響環(huán)路的帶寬,穩(wěn)定性,反應(yīng)速度等。經(jīng)數(shù)字濾波器平滑后的誤差信號(hào)送給VCO修正時(shí)鐘相位。最終環(huán)路鎖定時(shí),理論上相位誤差為零,90度偏移的時(shí)鐘作為恢復(fù)時(shí)鐘采樣串行輸入。 基于DPLL的CDR多了一個(gè)頻率跟蹤環(huán)路(Frequency Tracking Loop)。這是為了減小CDR的鎖定時(shí)間,減少對(duì)環(huán)路濾波器的設(shè)計(jì)約束。只有當(dāng) 頻率跟蹤環(huán)路 鎖定后,才會(huì)切換到數(shù)據(jù) 相位跟蹤環(huán)路。相位跟蹤環(huán)路失鎖時(shí),再自動(dòng)切換到頻率跟蹤環(huán)路。N倍參考時(shí)鐘(Reference Clock)頻率 和 線路速率接近相等,因此兩個(gè)環(huán)路的VCO穩(wěn)態(tài)控制電壓是接近相等的。借助 頻率跟蹤環(huán)路,減小了 相位跟蹤環(huán)路 的捕獲時(shí)間。

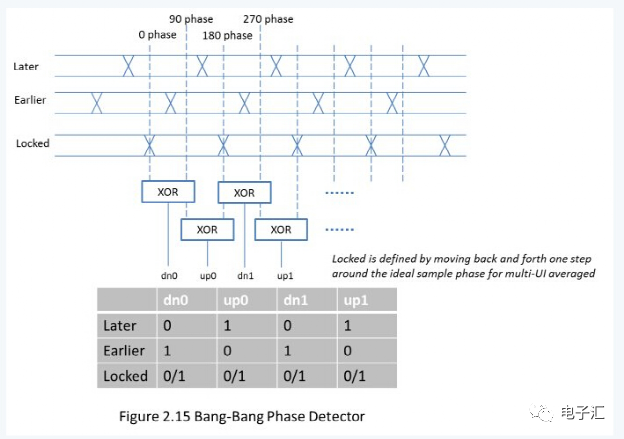

相位跟蹤環(huán)路鎖定時(shí),頻率跟蹤環(huán)路不會(huì)影響相位環(huán)路。因此SerDes接收側(cè)對(duì)參考時(shí)鐘的抖動(dòng)沒(méi)有很高的要求。 基于相位插值器的CDR的參考時(shí)鐘可以是收發(fā)公用的PLL,也可以是每個(gè)通道獨(dú)立的PLL。這種結(jié)構(gòu)的參考時(shí)鐘抖動(dòng)會(huì)直接影響恢復(fù)時(shí)鐘的抖動(dòng)以及接收誤碼率。 鑒相器(PD) 鑒相器用來(lái)比較相位誤差,相位誤差以UP或者DN的信號(hào)表示, UP/DN持續(xù)的時(shí)間正比于相位誤差。一個(gè)bang-bang結(jié)構(gòu)鑒相器的例子如圖2.15。例子中只用了四個(gè)相位的恢復(fù)時(shí)鐘作為例子。  ? 抽取器和濾波器 抽取器是為了讓濾波器在較低的頻率下工作。抽取的步長(zhǎng),平滑的方法都會(huì)影響環(huán)路的性能。數(shù)字濾波器有比例分支(Proportion)和積分分支(Integral)構(gòu)成,分別跟蹤相位誤差和頻率誤差。另外數(shù)字濾波器的處理延時(shí)也不能太大,如果處理延時(shí)過(guò)大,就會(huì)導(dǎo)致環(huán)路不能跟蹤相位和頻率的快速變化,導(dǎo)致誤碼。

? 抽取器和濾波器 抽取器是為了讓濾波器在較低的頻率下工作。抽取的步長(zhǎng),平滑的方法都會(huì)影響環(huán)路的性能。數(shù)字濾波器有比例分支(Proportion)和積分分支(Integral)構(gòu)成,分別跟蹤相位誤差和頻率誤差。另外數(shù)字濾波器的處理延時(shí)也不能太大,如果處理延時(shí)過(guò)大,就會(huì)導(dǎo)致環(huán)路不能跟蹤相位和頻率的快速變化,導(dǎo)致誤碼。

CDR的結(jié)構(gòu)不限于以上兩種,還有其他很多變種。基本上都是一個(gè)鎖相環(huán)路。環(huán)路的跟隨性能,穩(wěn)定性(STABILITY),帶寬(bandwidth)/增益(gain)性能分析是一個(gè)非常學(xué)術(shù)的問(wèn)題,用小信號(hào)線形模型分析,有非常多的書(shū)籍和資料解釋了環(huán)路的量化性能。CDR環(huán)路有一些的特點(diǎn)總結(jié)如下: 環(huán)路帶寬 1.頻率低于環(huán)路帶寬的相位抖動(dòng)會(huì)透過(guò)CDR轉(zhuǎn)移到恢復(fù)時(shí)鐘上。換句話說(shuō),頻率低于環(huán)路帶寬的抖動(dòng)可以被CDR跟蹤,不會(huì)引起誤碼。高頻的抖動(dòng)分量根據(jù)抖動(dòng)幅度的大小,可能會(huì)引起誤碼。

2.環(huán)路帶寬越大,鎖定時(shí)間越短,恢復(fù)時(shí)鐘的抖動(dòng)也越大。反之則鎖定時(shí)間越長(zhǎng),恢復(fù)時(shí)鐘的抖動(dòng)也越小。作為CDR,我們希望環(huán)路帶寬大一點(diǎn),這樣可以有更大的抖動(dòng)容忍能力,但是對(duì)于loop timing的應(yīng)用如SONET/SDH對(duì)恢復(fù)時(shí)鐘的抖動(dòng)有限制,又不能太大。

3. 開(kāi)關(guān)電源的開(kāi)關(guān)頻率一般小于環(huán)路帶寬,可以被CDR跟蹤。但是,一方面開(kāi)關(guān)電源耦合到VCO(Digital to Multi-Phase Convertor)上的噪聲不能被環(huán)路跟蹤,低成本Ring VCO尤其對(duì)電源噪聲敏感。另一方面開(kāi)關(guān)電源的諧波可能超出環(huán)路帶寬。 一些協(xié)議提供了CDR增益模板,如SDH/SONET。兼容這些協(xié)議需要計(jì)算輸入和輸出的抖動(dòng)預(yù)算。

2.5 公用鎖相環(huán)(PLL)

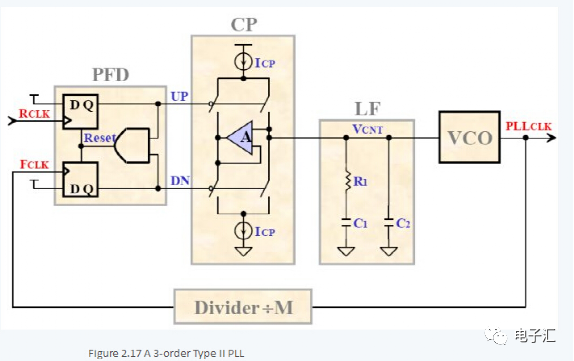

SerDes需要一個(gè)工作在數(shù)據(jù)波特率上的內(nèi)部時(shí)鐘,或者1/2數(shù)據(jù)波特率的內(nèi)部時(shí)鐘,工作在DDR模式。片外提供給SerDes的參考時(shí)鐘頻率遠(yuǎn)遠(yuǎn)低于數(shù)據(jù)波特率,PLL用來(lái)倍頻產(chǎn)生內(nèi)部高頻時(shí)鐘。FPGA的SerDes PLL一般有8x,16x,10x,20x,40x模式,以支持常用的SerDes接口協(xié)議。比如PCIExpress工作在5Gbps, 在40x模式下需要提供125MHz的片外參考時(shí)鐘,20x模式下需要提供250MHz的片外參考時(shí)鐘。 一個(gè)三階PLL電路如圖2.17,輸入信號(hào)的相位和VCO反饋信號(hào)的相位由鑒相器比較,相位誤差有charge pump轉(zhuǎn)化為電壓或電流信號(hào),經(jīng)過(guò)Loop Filter平滑后產(chǎn)生控制電壓,修正VCO的相位,最終使相位誤差趨于零。

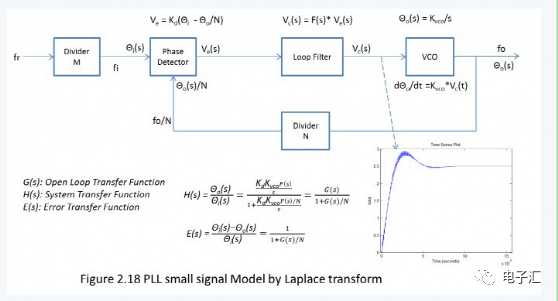

Figure 2.17 A 3-order Type II PLL PLL的工作過(guò)程分為入鎖過(guò)程和跟蹤過(guò)程。在入鎖過(guò)程,環(huán)路的模型可以用一個(gè)非線性微分方程表示,可以評(píng)估捕獲時(shí)間,捕獲帶寬等指標(biāo)。入鎖后,在小信號(hào)范圍內(nèi),PLL的模型是一個(gè)常系數(shù)線性方程,可以在拉普拉斯變換域研究PLL的帶寬,增益,穩(wěn)定性等性能,圖2.18是小信號(hào)數(shù)學(xué)模型。

PLL以傳輸函數(shù)極點(diǎn)(分母的根)個(gè)數(shù)命名環(huán)路的階數(shù)。VCO對(duì)相位有積分作用(Kvco/s),因此不帶濾波器的環(huán)路稱(chēng)為一階環(huán)。帶一階濾波器的環(huán)路稱(chēng)為二階環(huán)。一階環(huán)和二階環(huán)是無(wú)條件的穩(wěn)定系統(tǒng)。然而高階環(huán)路有更多的極點(diǎn)和零點(diǎn)可以獨(dú)立的調(diào)整帶款,增益,穩(wěn)定性,捕獲帶,捕捉時(shí)間等性能。 PLL的頻域傳輸函數(shù)特性主要有環(huán)路濾波器F(s)|s=jw決定, 一個(gè)通用的PLL頻域傳輸曲線如圖2.19所示。有兩個(gè)重要特征,環(huán)路帶款和jitter peaking。過(guò)大的peaking會(huì)放大jitter, 大的阻尼系數(shù)(damping factor)可以限制peaking, 但是會(huì)增加環(huán)路的如鎖時(shí)間, 影響滾降的速度和固有頻率(natural frequency)。 當(dāng)環(huán)路鎖定后,固定相位差: Kdc為環(huán)路的直流開(kāi)環(huán)增益,Δω為VCO中心頻率和受控頻率的差。對(duì)于charge pump + passive filter結(jié)構(gòu)的PLL相位誤差為零。 當(dāng)環(huán)路鎖定后,只有固定相位差,兩個(gè)輸入信號(hào)頻率相等。

fr/M = fo/N 對(duì)于輸入端的噪聲,環(huán)路是一個(gè)低通濾波器,可以抑制高于環(huán)路截止頻率的噪聲或干擾。作為SerDes的PLL, 希望帶寬的小一些,以抑制參考時(shí)鐘上的干擾和噪聲。 對(duì)于VCO噪聲,環(huán)路是一個(gè)高通濾波器的作用。只有低于環(huán)路截止頻率的VCO噪聲得到了抑制。過(guò)量的VCO高頻噪聲會(huì)惡化時(shí)鐘的抖動(dòng)。低速SerDes(<5Gbps)的VCO出于成本考慮采用Ring結(jié)構(gòu)的VCO,噪聲大且對(duì)電源敏感。高速SerDes的VCO采用噪聲小較小的LC結(jié)構(gòu)VCO。 ? 3.抖動(dòng)和信號(hào)集成 (Jitter, SI) 抖動(dòng)是指信號(hào)的跳邊時(shí)刻偏離其理想(ideal)或者預(yù)定(expected)時(shí)刻的現(xiàn)象。噪聲,非理想的信道,非理想的電路都是產(chǎn)生抖動(dòng)的原因。 3.1 時(shí)鐘的抖動(dòng) (clock jitter)

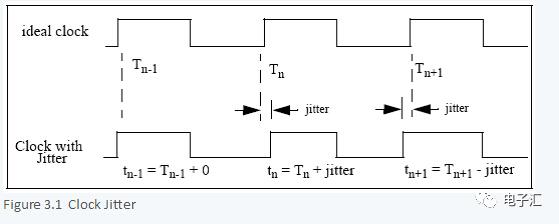

Figure 3.1Clock Jitter 對(duì)于時(shí)鐘信號(hào),根據(jù)應(yīng)用場(chǎng)景的不同,對(duì)抖動(dòng)的定義也不一樣。比如數(shù)字邏輯計(jì)算時(shí)序余量的時(shí)候,關(guān)心的是周期抖動(dòng)。而時(shí)鐘設(shè)計(jì)人員更喜歡相位抖動(dòng),因?yàn)榭梢岳妙l譜評(píng)估相位抖動(dòng),并可以用頻譜來(lái)評(píng)估具體的干擾對(duì)總相位抖動(dòng)的貢獻(xiàn)。

參考圖3.1,介紹一下幾種抖動(dòng)的定義。 相位抖動(dòng)(phase jitter)

Jphase(n)= tn– n*T。理想時(shí)鐘的每個(gè)周期T都是相等的,沒(méi)有抖動(dòng)。真實(shí)時(shí)鐘的跳邊沿相對(duì)于理想時(shí)鐘的偏離稱(chēng)作相位抖動(dòng)。 周期抖動(dòng)(period jitter) Jperiod(n)= (tn- tn-1)– T。周期抖動(dòng)是實(shí)際時(shí)鐘的周期相對(duì)于理想周期的偏離(deviation)。顯然Jperiod(n) = Jphase(n) - Jphase(n-1)。 Cycle-to-Cycle jitter Jcycle(n) = (tn- tn-1) - (tn-1- tn-2)。前后相鄰的兩個(gè)周期的偏差是Cycle-Cycle抖動(dòng)。顯然Jcycle(n)= Jperiod(n) – Jperiod(n-1)。 假設(shè)相位抖動(dòng)的最大值為 +/-Jp,而且抖動(dòng)的頻率fjitter= 0.5fclock= 0.5/T,也就是, tn-2時(shí)刻的相位抖動(dòng)為最大值+Jp,tn-1時(shí)刻的相位抖動(dòng)為最小值-Jp tn時(shí)刻的相位抖動(dòng)為最大值+Jp, tn+1時(shí)刻的相位抖動(dòng)為最小值-Jp 那么,周期抖動(dòng)最大值Jperiod=+/- 2* Jp 那么,Cycle-Cycle抖動(dòng)最大值Jcycle=+/- 4* Jp 3.2.數(shù)據(jù)的抖動(dòng)(data jitter) 在高速SerDes領(lǐng)域每個(gè)人都在說(shuō)抖動(dòng),因?yàn)槎秳?dòng)直接和誤碼率(BER)相關(guān)。 SerDes發(fā)送端的一個(gè)重要要求是抖動(dòng)(jitter generation)----針對(duì)特定的碼型(pattern),速率和負(fù)載情況下,發(fā)送端所生成的抖動(dòng)。

信號(hào)經(jīng)過(guò)信道(channel)到達(dá)接收端時(shí),又會(huì)進(jìn)一步放大抖動(dòng),不同的碼型(pattern)包含的頻率成分也不一樣,信道對(duì)不同頻率成分的傳輸延時(shí)也不一樣(非線性相位), 產(chǎn)生和數(shù)據(jù)pattern相關(guān)的確定性抖動(dòng)。阻抗不連續(xù)產(chǎn)生的反射,相鄰信號(hào)的串?dāng)_和噪聲都會(huì)引起數(shù)據(jù)抖動(dòng)。

SerDes接收端的一個(gè)重要指標(biāo)是抖動(dòng)容忍能力(Jitter Tolerance)----針對(duì)特定的碼型和誤碼率要求(BER<10-12),SerDes接收端能夠容忍的抖動(dòng)大小。對(duì)抖動(dòng)評(píng)估時(shí),會(huì)使用眼圖(eye-diagram),浴缸曲線(bath curve),抖動(dòng)分布柱狀圖(PDF),抖動(dòng)頻譜(jitter spectrum)等圖形手段。 有一點(diǎn)需要說(shuō)明,在談?wù)摳咚賁erDes的數(shù)據(jù)抖動(dòng)時(shí)(Tj,Rj,Dj etc.),是不包括低頻率抖動(dòng)的。這是因?yàn)榈皖l率的抖動(dòng)被認(rèn)為是一種wander,可以被CDR跟蹤,不會(huì)引起誤碼。在用示波器(SDA)測(cè)量數(shù)據(jù)抖動(dòng)的時(shí)候,可以設(shè)置示波器內(nèi)嵌的CDR環(huán)路帶寬,示波器測(cè)量的抖動(dòng)數(shù)據(jù)已經(jīng)濾掉了低頻抖動(dòng)。 根據(jù)抖動(dòng)產(chǎn)生的原因和概率密度函數(shù),常常將抖動(dòng)分為幾類(lèi)。對(duì)抖動(dòng)進(jìn)行分類(lèi)的意義在于某些類(lèi)型的抖動(dòng)可以被校正,而其他類(lèi)型的不能被校正。經(jīng)典的,總抖動(dòng)Tj(Total Jitter)被分類(lèi)為確定性抖動(dòng)Dj (deterministic jitter)和隨機(jī)抖動(dòng)Rj (random jitter)。抖動(dòng)以UI或者ps為單位,可以是均方根值,或者峰峰值。

3.2.1 Dj

Dj被進(jìn)一步細(xì)分, DCD(Duty cycle distortion) 占空比失真抖動(dòng)。差分信號(hào)的正端負(fù)端的偏置電壓不一致,或者上升沿和下降沿時(shí)間不一致會(huì)導(dǎo)致占空比失真。因?yàn)镈CD和數(shù)據(jù)pattern相關(guān),是可以被校正的抖動(dòng)。 DDJ(Data dependent jitter) 數(shù)據(jù)碼型相關(guān)的抖動(dòng),也稱(chēng) 碼間干擾ISI(intersymbol interference)。DDJ是由于不理想的信道導(dǎo)致。是可以被均衡器校正的抖動(dòng)。 Pj(Periodic jitter) 周期性抖動(dòng)。Pj由電路上周期性干擾源導(dǎo)致。比如開(kāi)關(guān)電源的開(kāi)關(guān)頻率,時(shí)鐘信號(hào)的串?dāng)_等。雖然電源的開(kāi)關(guān)頻率一般在CDR的跟蹤范圍內(nèi),但是低次諧波成分可能會(huì)落在環(huán)路帶寬外,或者jitter peaking區(qū)域, 更重要的是電源諧波對(duì)CDR內(nèi)VCO的干擾是不能被抑制和跟蹤的,所以對(duì)于基于Ring VCO的CDR一定要盡可能的使用LDO供電。Pj不能被均衡器校正. BUJ(Bounded uncorrelated jitter) BUJ由非時(shí)鐘的干擾源引起。如果干擾源aggressor和victim是異步的,抖動(dòng)的概率分布為有界的高斯分布,此時(shí)也稱(chēng)作CBGJ(Correlated Bounded Gaussian Jitter)。BUJ/CBGJ不能被校正。

3.2.2 Rj

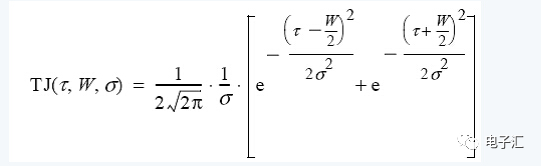

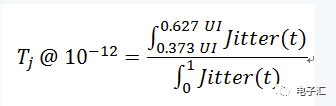

Rj有半導(dǎo)體本身的噪聲引起,一個(gè)重要特征就是Rj的概率密度函數(shù)是高斯分布的,沒(méi)有邊界,且和數(shù)據(jù)pattern無(wú)關(guān)。只有在一定誤碼率約束下,才可以被認(rèn)為是有界的。 3.2.3 Tj 數(shù)學(xué)意義上,抖動(dòng)的概率分布函數(shù)可以近視為高斯分布和雙底拉克分布的卷積。 對(duì)高斯分布有貢獻(xiàn)的抖動(dòng)為: Rj為高斯分布 大量Pj疊加的效果也為高斯分布 部分BUJ也為高斯分布 對(duì)雙底拉克分布有貢獻(xiàn)的抖動(dòng)為: DCD被近視為雙底拉克概率分布 高斯分布和雙底拉克分布的卷積:  其中,W被認(rèn)為是確定性抖動(dòng)的峰峰值,δ是高斯分布的均方差。見(jiàn)圖3.2, 可以看到,隨著確定性抖動(dòng)W的增加,概率密度分布曲線的頂部出現(xiàn)了雙峰。一般來(lái)講頂部曲線反映了確定性抖動(dòng)的大小程度。

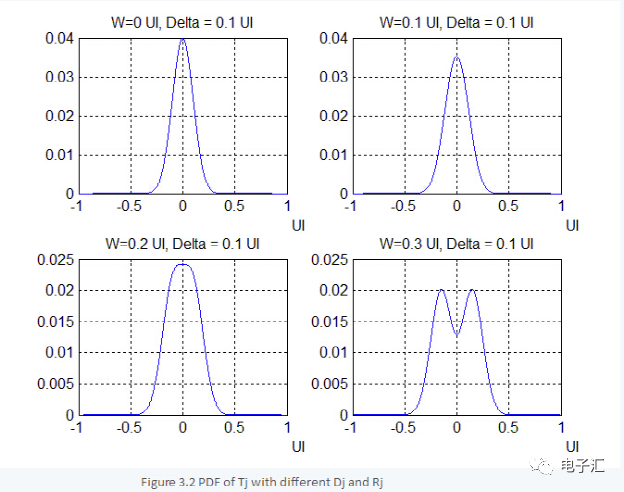

其中,W被認(rèn)為是確定性抖動(dòng)的峰峰值,δ是高斯分布的均方差。見(jiàn)圖3.2, 可以看到,隨著確定性抖動(dòng)W的增加,概率密度分布曲線的頂部出現(xiàn)了雙峰。一般來(lái)講頂部曲線反映了確定性抖動(dòng)的大小程度。 ???????????Figure 3.2 PDF of Tj with different Dj and Rj 把一個(gè)UI內(nèi)的兩個(gè)跳變沿處(0 UI處和1UI處)的概率分布函數(shù)放在一張圖中,就是抖動(dòng)的浴缸曲線(bathtub curve)。因?yàn)閷?duì)數(shù)的寬動(dòng)態(tài)范圍,Y坐標(biāo)以對(duì)數(shù)顯示。圖3.3為確定性抖動(dòng)W=0.05UI, 高斯抖動(dòng)方差0.05UI的浴缸曲線。

???????????Figure 3.2 PDF of Tj with different Dj and Rj 把一個(gè)UI內(nèi)的兩個(gè)跳變沿處(0 UI處和1UI處)的概率分布函數(shù)放在一張圖中,就是抖動(dòng)的浴缸曲線(bathtub curve)。因?yàn)閷?duì)數(shù)的寬動(dòng)態(tài)范圍,Y坐標(biāo)以對(duì)數(shù)顯示。圖3.3為確定性抖動(dòng)W=0.05UI, 高斯抖動(dòng)方差0.05UI的浴缸曲線。

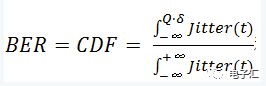

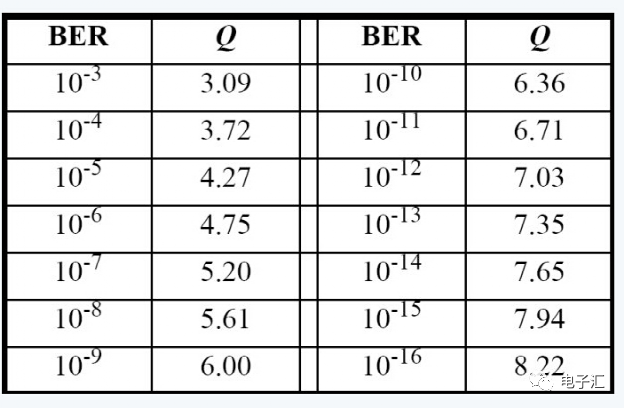

Figure 3.3Bathtub Curve of Tj with 0.05 Dj peak and 0.05 Rj RMS 浴缸曲線還會(huì)標(biāo)出對(duì)應(yīng)的誤碼率BER坐標(biāo),比如圖中BER=10^-12的峰峰值抖動(dòng)為T(mén)j(p-p)=0.373*2 = 0.746 UI。曲線下面的面積占總面積的比率就是誤碼率。比如圖中,  ?浴缸曲線的頂部主要為確定性抖動(dòng)Dj的貢獻(xiàn),越靠近底部,高斯抖動(dòng)的貢獻(xiàn)越大,并以高斯曲線的斜率衰減,也因此常利用高斯分布的特性進(jìn)行估算。下表為高斯分布和均方差關(guān)系。

?浴缸曲線的頂部主要為確定性抖動(dòng)Dj的貢獻(xiàn),越靠近底部,高斯抖動(dòng)的貢獻(xiàn)越大,并以高斯曲線的斜率衰減,也因此常利用高斯分布的特性進(jìn)行估算。下表為高斯分布和均方差關(guān)系。

在規(guī)定的BER內(nèi),利用該表可以快速估算均方差值和峰峰值之間的關(guān)系。比如高斯抖動(dòng)的均方根0.05UI,誤碼率要求為10^-12 BER,查表可知Q=7,那么高斯抖動(dòng)的峰峰值要求是0.05UI*7*2 = 0.7UI。 如前所述,W=0.05UI,Rj=0.05UI計(jì)算出的總抖動(dòng)Tj=0.746UI;

利用高斯特性估算的高斯抖動(dòng)為0.7UI。

如果按Tj = Rj(0.7UI)+Dj(0.05UI)計(jì)算得到0.75U,基本是一致的,差異是因?yàn)楫?huà)圖程序有量化誤差。

4.信號(hào)集成(SI)及仿真

4.1信道channel

SerDes信道關(guān)注的頻率范圍是0Hz到奈奎斯特頻率,也就是2倍的信號(hào)基頻。信號(hào)的基頻是信號(hào)線速率的一半,也就是說(shuō)信號(hào)的奈奎斯特頻率就是線速率。信道對(duì)信號(hào)的損傷包括插入損失(insertion loss),反射 (reflection),串?dāng)_(crosstalk)等。這些損傷可以用S-parameter信道模型來(lái)表達(dá)。S-parameter可以有矢量網(wǎng)絡(luò)分析儀測(cè)量(Vector Network Analyzer)得到。信道不是一個(gè)純阻性網(wǎng)絡(luò),還包括容性和感性。這樣對(duì)不同頻率里成分的時(shí)延也不一樣,從而產(chǎn)生和data pattern相關(guān)的抖動(dòng)。 信道上的每一個(gè)不連續(xù)阻抗點(diǎn)都會(huì)產(chǎn)生反射,根據(jù)反位置的不同,反射信號(hào)會(huì)以不同的相位疊加在原始信號(hào)上,增加或者減小信號(hào)的幅度。 SerDes信號(hào)為差分形式,對(duì)共模干擾有較強(qiáng)的抑制。如果在+/-端上的干擾有差異,就會(huì)引入串?dāng)_。通常外部PCB可以保證SerDes數(shù)據(jù)和干擾源保持足夠的距離,但是芯片內(nèi)部由于考慮到經(jīng)濟(jì)性,很難保證SerDes信號(hào)和干擾源足夠的隔離距離,尤其是一個(gè)通道自己的發(fā)送信號(hào)干擾自己的接收信號(hào)。

4.2芯片封裝Package

封裝package也是信道的一部分。芯片外部的信道可以通過(guò)VNA測(cè)量的到,而封裝的S-parameter通常有芯片制造商提供,仿真時(shí)可以把兩者級(jí)聯(lián)起來(lái)。封裝package由于距離較短,insertion loss通常不是主要問(wèn)題,主要考慮的是阻抗匹配問(wèn)題。

4.3 SI仿真

信號(hào)集成性(SI)仿真可以通過(guò)把SerDes發(fā)送端SPICE模型,封裝和信道的S-parameter模型,接收端SPICE模型級(jí)聯(lián)起來(lái)搭建仿真平臺(tái),利用仿真工具對(duì)不同的激勵(lì)在不同的測(cè)試條件作電路仿真。通過(guò)測(cè)量SerDes接收端的眼圖來(lái)評(píng)估是否滿(mǎn)足設(shè)計(jì)需求。也可以通過(guò)實(shí)測(cè)接收端眼圖,檢驗(yàn)是否滿(mǎn)足接收端的眼圖模板,或者協(xié)議規(guī)定的眼圖模板。圖4.1為一個(gè)實(shí)測(cè)的3.125Gbps信號(hào)的眼圖及模板,同時(shí)也包含了浴缸曲線和統(tǒng)計(jì)圖。

Figure 4.1 Rx-end Eye-diagram of A 3.125Gbps SerDes 對(duì)于高速SerDes(>5Gbps),這種傳統(tǒng)的電路仿真方法已經(jīng)不能滿(mǎn)足設(shè)計(jì)的需求。首先,過(guò)量的碼間干擾ISI導(dǎo)致接收端眼圖完全閉合,但是通過(guò)芯片內(nèi)的DFE均衡后,眼圖可能是很好的。其次,電路仿真(SPICE)的速度非常慢,即使是有辦法把DFE均衡加入仿真,由于DFE仿真需要足夠長(zhǎng)時(shí)間的bits來(lái)訓(xùn)練,此時(shí),電路仿真的仿真時(shí)間是不可接受的。 對(duì)于高速SerDes的仿真需要借助統(tǒng)計(jì)分析 (statistical analysis) 的方法。統(tǒng)計(jì)分析的方法把發(fā)送端-信道-接收端的連接近視為線性系統(tǒng),計(jì)算系統(tǒng)脈沖響應(yīng)h(t),加入噪聲源來(lái)模擬抖動(dòng),然后用激勵(lì)對(duì)脈沖響應(yīng)進(jìn)行卷積,得到接收端的信號(hào),這種方法可以把廠家私有的FFE,DFE自適應(yīng)算法加入仿真。 統(tǒng)計(jì)分析 (statistical analysis)方法不能仿真電路的非線性和時(shí)變特性,所以高速SerDes往往要兩者結(jié)合起來(lái)仿真SI。更多關(guān)于統(tǒng)計(jì)分析 (statistical analysis)方法可以參考。

5.結(jié)尾

有人講過(guò),現(xiàn)在的汽車(chē)是如此復(fù)雜,以至于雖然每一個(gè)零件都有人懂,但是合起來(lái)作為整車(chē)卻沒(méi)人能夠全懂。近些年來(lái),F(xiàn)PGA變的越來(lái)越復(fù)雜,對(duì)工程師的要求也越來(lái)越高。要成為一個(gè)合格的FPGA應(yīng)用工程師,不僅要擅長(zhǎng)數(shù)字電路的設(shè)計(jì),還要懂得高速SerDes, 信號(hào)集成SI, DSP算法, 多核CPU, 嵌入式操作系統(tǒng)等。每一項(xiàng)技術(shù)背后都是一個(gè)專(zhuān)業(yè)領(lǐng)域,一個(gè)人不會(huì)在每一個(gè)領(lǐng)域內(nèi)都是專(zhuān)家,只要比別人多學(xué)習(xí)一點(diǎn),關(guān)鍵時(shí)候就會(huì)突出你的價(jià)值。本篇主要介紹了SerDes的基本結(jié)構(gòu)和用好SerDes需要掌握一些的知識(shí),希望對(duì)你的工作有所幫助。

-

接口

+關(guān)注

關(guān)注

33文章

8961瀏覽量

153271 -

觸發(fā)器

+關(guān)注

關(guān)注

14文章

2033瀏覽量

61916 -

SerDes

+關(guān)注

關(guān)注

7文章

211瀏覽量

35617 -

時(shí)鐘信號(hào)

+關(guān)注

關(guān)注

4文章

466瀏覽量

29100

原文標(biāo)題:最全的FPGA的SerDes接口

文章出處:【微信號(hào):電子匯,微信公眾號(hào):電子匯】歡迎添加關(guān)注!文章轉(zhuǎn)載請(qǐng)注明出處。

發(fā)布評(píng)論請(qǐng)先 登錄

GMII、SGMII和SerDes的差異總結(jié)

請(qǐng)問(wèn)6678中的srio的serdes和以太網(wǎng)的serdes是共用還是各自有自己的serdes?

SERDES作用和SerDes結(jié)構(gòu)

高速SERDES接口在網(wǎng)絡(luò)方面有哪些應(yīng)用?

Nautilus UDI方案是如何實(shí)現(xiàn)高速SerDes測(cè)試的?

SerDes是怎么工作的

SERDES的優(yōu)勢(shì) SERDES演變的看法

什么是SerDes?SerDes的應(yīng)用場(chǎng)景又是什么呢?

SerDes是怎么設(shè)計(jì)的?(一)

為什么我們需要SERDES?SERDES的優(yōu)點(diǎn)有哪些?

簡(jiǎn)單認(rèn)識(shí)串行解串器

什么是SerDes?SerDes有哪些應(yīng)用?

SerDes的基本結(jié)構(gòu)

SerDes的基本結(jié)構(gòu)

評(píng)論