作者:李 楊,蘇和平,張 丹,許喬

摘要:針對現有的千兆以太網通信接口設計中存在的價格昂貴、不能勝任多路以太網傳輸等問題,提出并實現一種基于 FPGA+ARM 的多路千兆以太網通信接口模塊。該設計分為 ARM 和 FPGA 兩個部分,通過 STM32 微處理器帶有的靈活靜態存儲控制器(FSMC)接口進行數據交換。ARM 部分通過發送函數、接收函數實現對以太網接口控制以及對數據的處理;FPGA 部分采用自頂向下的設計方法,通過時序轉換模塊、打包解包模塊以及 MAC 控制模塊實現以太網接口功能,并且定義了兩個自定義協議,分別用于 ARM 與 FPGA 通信以及 FPGA 內部打解包模塊與 MAC 控制模塊的通信。搭建了硬件測試驗證平臺對設計進行了全面驗證。硬件測試驗證結果表明該設計能夠正確實現以上功能。該方案成本低廉、擴展性強、支持多通道傳輸且支持網絡風暴抑制,適用于對成本要求較高且需多通道以太網傳輸的場景。

引 言

隨著人工智能、大數據和物聯網等新興技術的發展,原始數據井噴式地涌現出來,這也對接口提出了更高的要求[1?2],高速、可靠的傳輸接口往往是整個項目的技術關鍵。

近年來,國內對于以太網接口的研究取得了顯著進步。文獻[3?4]采用 Zynq?7000 芯片,利用 ARM+FPGA 架構在芯片內搭建了千兆以太網模塊,傳輸速度分別為640 Mb/s 和 870 Mb/s。文獻[5]采用國產 FPGA 芯片,自行研發了 SGMII core與 MAC core,實現了千兆以太網口的設計。文獻[6]采用 DSP+FPGA 架構形式,搭建了多路串口、以太網通信系統,實現 40 路 RS 422/RS 485 通信功能。文獻[7]采用 ARM 和 FPGA 芯片,利用 FSMC 實現兩個芯片通信,采集多路光柵數據。文獻[8]采用 FPGA設計實現了一種UDP 網絡 IP 核,兼容GMII、RGMII以及SGMII接口,且移植性較強。

但是上述設計存在價格昂貴、不能勝任多路以太網傳輸任務、不支持風暴抑制等不足。而網絡風暴抑制[9?11]的功能一般在軟件層面,這會消耗大量資源算力。為此本文采用 ARM+FPGA 架構,通過 FSMC 總線進行芯片間通信,充分發揮 ARM 在控制方面及 FPGA 善于擴展和并行處理的優點,實現一種多通道、擴展性強、成本低廉且支持風暴抑制的千兆以太網接口模塊。

1 整體結構

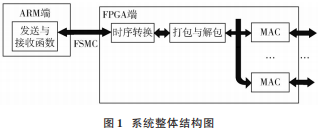

基于 FPGA+ARM 的多路千兆以太網通信系統的整體結構如圖 1 所示。外部數據通過千兆網口進入 FPGA進行解包,然后通過 FSMC 總線[12]傳遞給 ARM 進行處理;下行數據由 ARM 發出,通過 FSMC 總線進入 FPGA中進行打包,根據命令從相應通道的千兆以太網口向外發送。

FPGA 與 ARM 之間通過 FSMC 總線連接,如圖 2 所示。FSMC 總線包含 6 位地址總線、16 位數據總線以及控制總線。

2 FPGA 設計

FPGA 芯 片 選 用 Altera 公 司 的 EP4CE10F17C8 芯片,其擁有 10 320 個邏輯單元,可以滿足本系統功能要求。ARM 處理器選用 ST 公司的 STM32F407IG,具有Cortex?M4處理器內核,1 MB FLASH 且具有 FSMC。

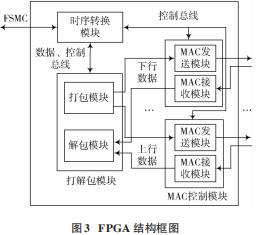

FPGA 用 Verilog語言開發,FPGA 結構框圖如圖 3所示,由時序轉換模塊、打包解包模塊和 MAC 控制模塊三部分組成,其中可以接多個 MAC接收模塊。

2.1 時序轉換模塊

時序轉換模塊將 FSMC 復雜時序轉換為較簡單時序,同時將一路 FSMC轉換多路內部總線,其中包括傳遞數據的總線和各個模塊的控制總線。其中轉換出來的控制總線使能各個模塊功能,訪問各個模塊的寄存器。

2.2 打包模塊和解包模塊

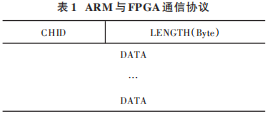

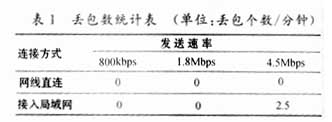

打包解包模塊約定了 ARM 與 FPGA 通信的協議,如表 1 所示。在要發送的數據前添加要發通道號以及待發送數據的字節長度,以便于打包模塊知道數據應當發送到哪個 MAC 和解包模塊,以及數據包來自哪個 MAC,同時將一路內部數據總線又分為多路數據總線,與多個MAC相連。

發送功能:當檢測到發送開始寄存器操作后,將發送數據寄存器的數據寫入前級 FIFO 緩存,直到檢測到發送完成寄存器操作,停止向前級 FIFO 緩存,接著開始檢查保存包是否正確并產生接收完成信號,若當前包不正確,讀出當前包同時丟棄,正確則保留。根據表 1 協議判斷當前包要發送到的 MAC,待其可以接收數據時向其發送。

接收功能:4 個通道的數據首先進入 4 個通道 FIFO中,隨后通道掃描器會依次循環掃描這 4 個通道 FIFO,若該通道使能且有數據,就將該通道數據緩存到前級FIFO 并產生接收完成信號,等待 ARM 讀取數據,待ARM 讀取完繼續循環之前操作。

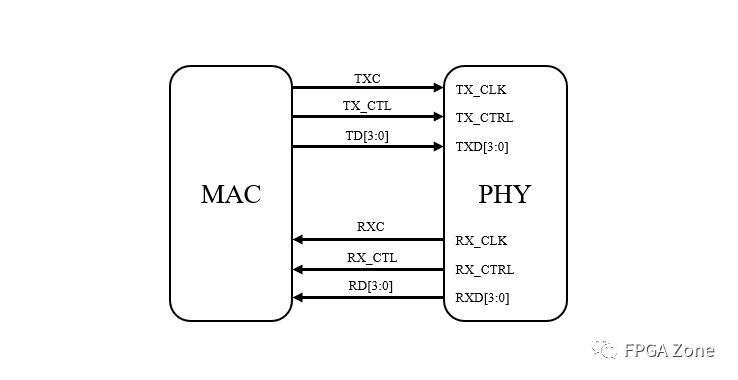

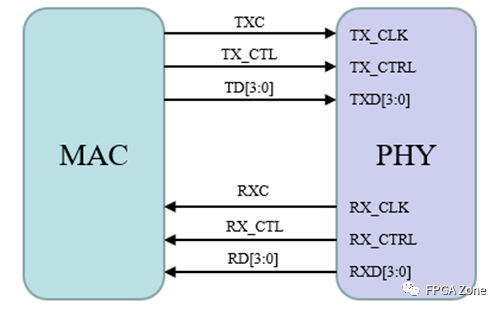

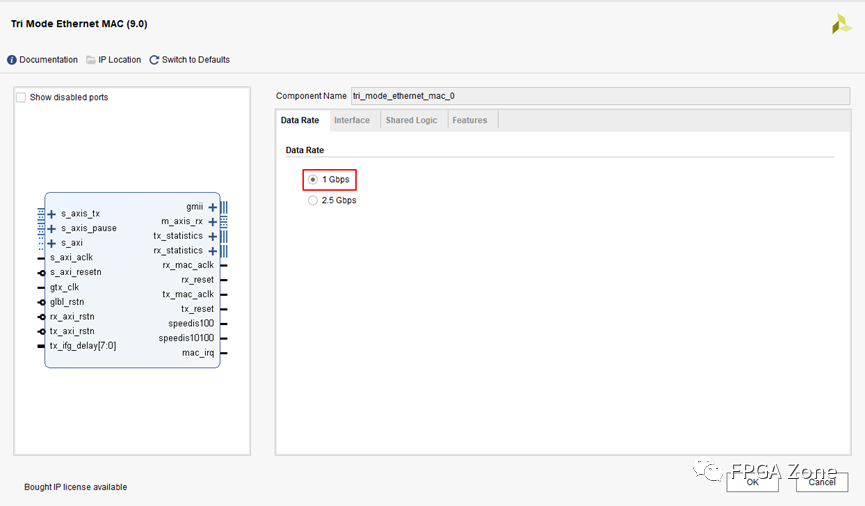

2.3 MAC模塊

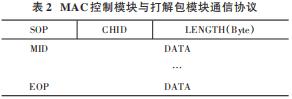

MAC 控制模塊實現以太網的數據鏈路層協議,同時定義了與打解包模塊的通信協議,如表 2 所示。這個協議是在表 1 通信協議的基礎上,在包頭添加包頭標志SOP,包中部添加中部標志 MID,在包尾添加包尾標志EOP,以便于以數據包的形式進行傳輸和處理。設計功能:速率為 1 000 Mb/s,幀間隔可配,支持自動填充,支持 CRC 校驗,支持廣播/組播風暴抑制,支持 MAC 地址白名單。

MAC 發送的邏輯:首先有 MAC 數據幀待 MAC 模塊發出,等待設定的幀間隔時間結束,接著發送前導碼和幀定界符,然后發送待發送 MAC 數據幀,若長度小于60 B則用零填充至 60 B,最后發送循環校驗序列。

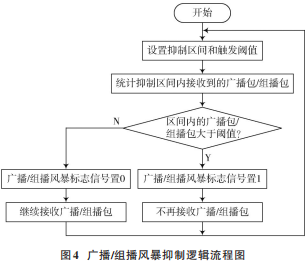

廣播/組播風暴抑制邏輯如圖 4 所示。根據設定時間以及設定的廣播包閾值,如果在設定的時間內接收的廣播包數量超過閾值,進行廣播包抑制。同理,組播風暴抑制邏輯和廣播風暴抑制邏輯相同。

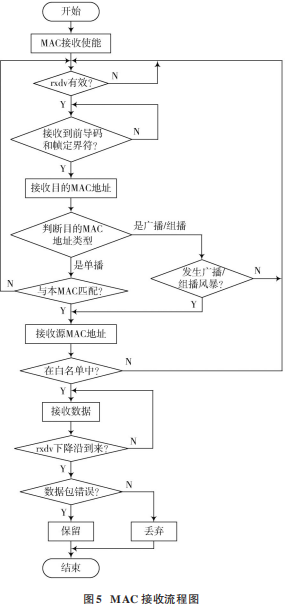

MAC 接收的邏輯流程圖如圖 5 所示。接收使能MAC 模塊開始接收,若 rxdv 信號有效且接收到前導碼和幀定界符,則進行下一步的目的 MAC 地址接收。接下來進行廣播/組播/單播的類型判斷,廣播或組播的處理類似,會判斷是否已經發生廣播/組播風暴,發生則不再接收數據,沒有就繼續;單播的話不需要考慮抑制,所以這步跳過。接下來接收源 MAC 地址,僅單播需要判斷是否源 MAC 地址在 MAC 地址白名單中,不在白名單則停止操作,在就接收數據,直到 rxdv 變為低電平。最后判斷接收是否錯誤,包括長度和 CRC校驗。

2.4 ARM 系統軟件設計

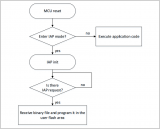

ARM 端程序是運行在 μCOSⅢ操作系統[13]之上的,ARM 程序使用 C 語言編寫,ARM 程序分為兩個模塊,即發送程序和接收程序。

當任務調用發送函數,向發送開始寄存器寫操作,接著向發送數據寄存器發送通道號以及數據長度,然后向發送數據寄存器發送待發送數據,發送數據完成后,向發送完成寄存器寫操作。

當有 ARM 檢測到接收中斷時,ARM 查詢中斷狀態寄存器,確定是接收中斷,同時清除該中斷標志,然后進行讀取操作。同時接收過程也支持輪詢寄存器,方法與中斷接收類似,不再贅述。

3 驗 證

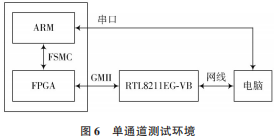

測試內容包括單通道和多通道功能驗證。單通道驗證通過如圖 6 所示的測試環境驗證,多通道的驗證通過 ModelSim 仿真驗證。

3.1 單通道驗證

單通道測試環境如圖 6 所示。待測試設計模塊外接一個 RTL8211EG?VB 芯片的擴展板,然后通過網線與電腦相連。用 Wireshark 軟件抓取 ARM 發來的數據幀,驗證本系統的發送功能;采用科來數據包生成器生成驗證接收功能所需的各種數據幀,使用科來數據包播放器從電腦端向本接口發送數據幀,并用串口助手查看本接口接收到的包數。

測試項目分為兩部分:發送功能測試和接收功能測試。發送功能測試需要驗證發送內容是否正確,需要填充的數據幀是否填充。接收功能測試需要驗證正確接收、MAC地址白名單功能以及廣播/組播風暴抑制功能。

3.1.1 發送功能驗證

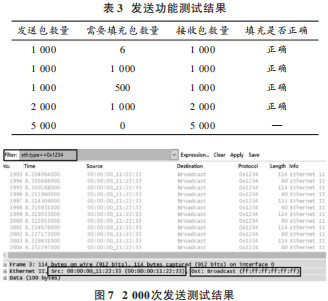

測試工具為 Wireshark。測試內容:ARM 端生成一些待發送數據,統計電腦接收數據包個數,以及檢查要填充的數據包是否填充。測試結果見表 3。其中,圖 7是 2 000 次發送測試的 Wireshark 抓包圖。為了不影響抓取,固定 MAC幀類型為 0x1234,設計系統的 MAC地址為00:00:00:11:22:33,以廣播的形式發包進行測試。

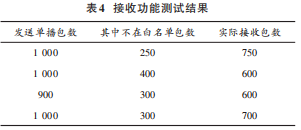

3.1.2 接收功能驗證

1)正常接收驗證

測試工具:科來數據包生成器、科來數據包播放器、串口調試助手。向設計接口發送不在白名單中的單播包,驗證接口的接收功能以及地址白名單功能。具體測

2) 廣播包/組播包風暴抑制

測試工具:科來數據包生成器、科來數據包播放器、串口調試助手。測試中固定風暴抑制區間間隔為65 ms。設置不同的廣播包接收的抑制閾值,構造廣播包與單播包各不同的組合,將其循環向設計接口發送。測試結果見表 5,其中理論接收包數等于發包總數乘以一次循環中不會發生風暴的比例。

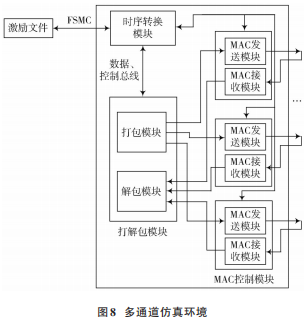

3.2 多通道驗證

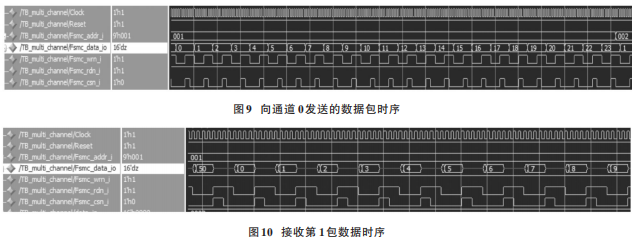

仿真環境如圖 8所示,例化 3個 MAC 模塊,將這 3個模塊的 MAC 發送端口和接收端口相連構成回環。激勵文件模擬 FSMC 時序,通過 FSMC 接口分別向通道 0,1,2各發送一包數據。這三包的構成一致都是從 0 開始遞增,且結尾為固定值 1,他們的長度分別是 50 B,46 B,60 B。圖 9是這三包數據中的第一包數據。

根據表 1 所示的協議,經過回環得到的數據包頭部是該數據包的長度與通道號。要驗證多通道功能的正確性,需保證接收的數據包頭部的長度和通道號正確且后面數據部分正確。仿真測試中將包頭的[15:14]位表示通道,[10:0]位表示數據部分長度,單位為字節。如圖 10所示,按照協議解析,表示通道 0,長度為 50 B。其余兩包內容類似,由于篇幅原因就不附上,同時核對各包實際數據部分也與對應發送包相同。

經過以上一系列測試,數據發送和接收功能正常,傳輸時不丟包,且能穩定可靠工作,滿足設計要求。

4 結 語

本文針對多路以太網通信需求,基于 ARM 和 FPGA特點,綜合兩者的優勢提出一種基于 ARM+FPGA 的多路千兆以太網通信系統。實現了 MAC 幀發送和接收、廣播/組播風暴抑制、幀間隔配置、MAC 白名單和錯誤檢測。從驗證結果來看,系統運行穩定可靠,滿足設計需求。本設計只針對千兆以太網進行設計,在實際應用中可以做成 10M/100M/1 000M 自協商,以適應市場需求。本文設計的以太網接口相比其他設計,具有多通道和硬件風暴抑制的功能,適合多通道的以太網傳輸。由于日益緊張的國際形勢,使得國內對于芯片國產化的觀念日趨強烈,下一步將考慮實現此接口在國產化芯片上的移植應用。

審核編輯:郭婷

-

FPGA

+關注

關注

1643文章

21983瀏覽量

614618 -

ARM

+關注

關注

134文章

9321瀏覽量

375417 -

以太網

+關注

關注

40文章

5594瀏覽量

174973

原文標題:論文速覽 | 基于FPGA+ARM多路千兆以太網通信接口設計

文章出處:【微信號:現代電子技術,微信公眾號:現代電子技術】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

基于Xilinx FPGA的千兆以太網控制器的開發

FPGA+DSP;FPGA+ARM硬件設計

TM1300芯片的以太網通信接口的設計和實現

LPC23xx的自適應以太網通信接口設計

基于FPGA的UDP RGMII千兆以太網通信方案

基于FPGA的UDP RGMII千兆以太網設計

基于FPGA+ARM多路千兆以太網通信接口設計

基于FPGA+ARM多路千兆以太網通信接口設計

評論