GOF ECO介紹

GOF ECO是一款芯片網(wǎng)表功能ECO的軟件。在項(xiàng)目中后期或流片之后,發(fā)現(xiàn)邏輯功能有BUG或者設(shè)計(jì)需求有變更時(shí),不需要重走“綜合 -> DFT -> APR”的完整流程,利用GOF ECO即可自動(dòng)分析新舊兩個(gè)版本的差異,并對(duì)APR網(wǎng)表進(jìn)行局部修改。GOF ECO不僅大大縮短了芯片ECO的Turn-around時(shí)間,還大大提升了芯片復(fù)雜邏輯ECO的成功率。

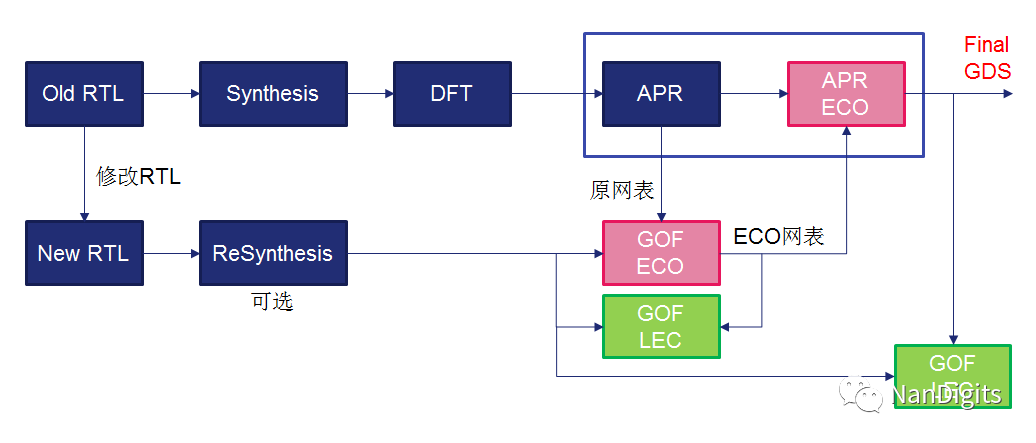

GOF ECO流程

如上圖所示,當(dāng)我們?cè)O(shè)計(jì)(RTL)上有改動(dòng),并充分仿真驗(yàn)證確認(rèn)功能正確后,就可以開(kāi)始網(wǎng)表ECO工作了。大致分為以下幾個(gè)步驟:

首先,我們需要收集老設(shè)計(jì)的文件,并確認(rèn)文件的完整性和準(zhǔn)確性。

其次,對(duì)設(shè)計(jì)重新做綜合,得到重新綜合的網(wǎng)表(這一步可選)。

再次,用GOF LEC分析新設(shè)計(jì)與老設(shè)計(jì)的差異,確認(rèn)這些差異是否合理。

然后,用GOF ECO做網(wǎng)表的ECO,并調(diào)整ECO方案和約束來(lái)獲得最佳結(jié)果。

最后,在后端工具里實(shí)現(xiàn)ECO Place和ECO Route,完成邏輯功能ECO。

下面將詳細(xì)描述和解釋每一個(gè)步驟的實(shí)現(xiàn)方法和注意事項(xiàng)。

一、準(zhǔn)備工作

準(zhǔn)備工作的目的?

這些文件通常來(lái)自于不同的部門或組,我們要確保ECO所需文件的準(zhǔn)確性,防止用錯(cuò)文件版本,確保后續(xù)ECO工作正常開(kāi)展。

需要準(zhǔn)備哪些文件?

需要提前收集的文件如下:

老設(shè)計(jì)

老RTL

老綜合網(wǎng)表

老DFT網(wǎng)表和DFT約束文件

老APR網(wǎng)表(我們的ECO目標(biāo))

并對(duì)老設(shè)計(jì)做邏輯等價(jià)性檢查(LEC),來(lái)確保收集到的文件和版本是正確的:

RTL vs 綜合網(wǎng)表

綜合網(wǎng)表 vs DFT網(wǎng)表

DFT網(wǎng)表 vs APR網(wǎng)表

二、重新綜合(可選)

這一步是可選的,但我們建議做,因?yàn)樾翿TL與老APR網(wǎng)表中間經(jīng)過(guò)了很多次優(yōu)化,這些優(yōu)化使得網(wǎng)表結(jié)構(gòu)發(fā)生了巨大的變化,而這些變化會(huì)加大邏輯功能ECO的難度和準(zhǔn)確性。對(duì)于超大規(guī)模設(shè)計(jì),重新綜合一次需要兩三天或者一周,這個(gè)時(shí)候我們建議可以先忽略這一步。

一般來(lái)說(shuō),這一步我們用原有的綜合腳本重新跑一次即可。

三、一致性檢查

邏輯一致性檢查結(jié)果的正確性和合理性是保證網(wǎng)表ECO效果的前提。GOF ECO正是利用一致性檢查的技術(shù)來(lái)分析兩個(gè)設(shè)計(jì)的差異,來(lái)找到應(yīng)該修理的地方。如果一致性檢查有虛假的不等價(jià),GOF ECO就很可能會(huì)做一些無(wú)用的修改,會(huì)或多或少影響補(bǔ)丁的大小和ECO的成功率。

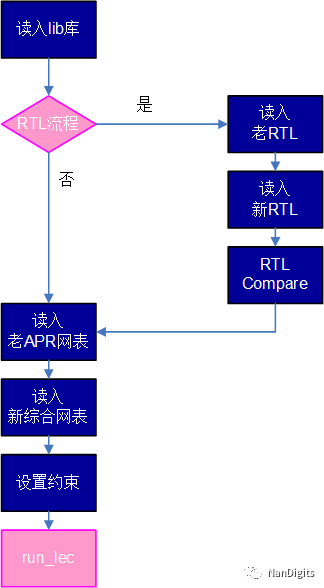

用GOF做一致性檢查的流程如下:

下面是參考代碼:

# gof_lec.pl use strict; # 讀入lib庫(kù) read_library("art.5nm.lib"); read_library("sram.lib"); read_library("analog.lib"); # RTL流程 my $rtl_flow = 1; if($rtl_flow){ # 設(shè)置define和include set_define("SYNTHESIS"); set_define("NO_SIM"); set_inc_dirs("/project/nd900/vlib/include", "/project/nd900/IPS/include"); # 讀入老RTL my @rtl_old = ("ref0.sv", "ref1.sv", "ref2.sv"); read_rtl('-ref', @rtl_old); # 讀入新RTL my @rtl_new = ("imp0.sv", "imp1.sv", "imp2.sv"); read_rtl('-imp', @rtl_new); # 設(shè)置頂層模塊 set_top("topmod"); # 對(duì)比RTL rtl_compare; } # 讀入重新綜合的網(wǎng)表 read_design("-ref", "reference.gv"); # 讀入老的APR網(wǎng)表 read_design("-imp", "implementation.gv"); # 設(shè)置頂層 set_top("topmod"); # 設(shè)置DFT約束 set_ignore_output("scan_out*"); set_pin_constant("scan_enable", 0); set_pin_constant("scan_mode", 0); # 做一致性檢查 run_lec();

運(yùn)行g(shù)of_lec.pl的腳本,分析不等價(jià)的點(diǎn)是否合理:

gof -run gof_lec.pl

先確認(rèn)log里unmapped點(diǎn)是否合理。當(dāng)設(shè)計(jì)里新加了dff或者輸出端口,GOF LEC就會(huì)分析出這些新加的點(diǎn)并報(bào)出來(lái)。

如果有不合理的點(diǎn)報(bào)出來(lái),就要debug找到原因:

首先,可以與formality或者conformal的LEC結(jié)果做對(duì)比,來(lái)排除用錯(cuò)文件、約束設(shè)置錯(cuò)誤等問(wèn)題。

然后,可以用GOF的電路圖的方式來(lái)調(diào)試:

用start_gui來(lái)啟動(dòng)GUI

在網(wǎng)表里找到不等價(jià)的點(diǎn),右擊在電路圖上顯示

也可以按ctrl-g來(lái)快速加載

常見(jiàn)的電路圖調(diào)試方法:

在電路圖中顯示老設(shè)計(jì)和新設(shè)計(jì)的fanin,查看fanin是否一樣,這是最容易發(fā)現(xiàn)問(wèn)題的地方

然后,同時(shí)選中兩個(gè)設(shè)計(jì)的時(shí)鐘pin或復(fù)位pin,查看兩個(gè)設(shè)計(jì)的時(shí)鐘和復(fù)位是否等價(jià)

再排查scan enable pin的設(shè)置

最后,逐步trace出兩個(gè)設(shè)計(jì)的邏輯錐的電路,從后向前,尋找不等價(jià)的點(diǎn)。

四、PreMask網(wǎng)表ECO

在確認(rèn)一致性檢查報(bào)出的不等價(jià)的點(diǎn)都是合理的情況下,就可以正式開(kāi)始ECO了。

參考腳本如下:

# gof_eco.pl

use strict;

undo_eco(); #<-- 撤銷之前的改動(dòng)

setup_eco("eco20221102"); #<-- 設(shè)計(jì)ECO的名字,GOF ECO輸出網(wǎng)表中新加的cell和連線會(huì)自動(dòng)加上這個(gè)前綴

# 讀入lib庫(kù)

read_library("art.5nm.lib");

read_library("sram.lib");

read_library("analog.lib");

# RTL流程

my $rtl_flow = 1;

if($rtl_flow){

# 設(shè)置define和include

set_define("SYNTHESIS");

set_define("NO_SIM");

set_inc_dirs("/project/nd900/vlib/include", "/project/nd900/IPS/include");

# 讀入老RTL

my @rtl_old = ("ref0.sv", "ref1.sv", "ref2.sv");

read_rtl('-ref', @rtl_old);

# 讀入新RTL

my @rtl_new = ("imp0.sv", "imp1.sv", "imp2.sv");

read_rtl('-imp', @rtl_new);

# 設(shè)置頂層模塊

set_top("topmod");

# 對(duì)比RTL

rtl_compare;

}

# 讀入重新綜合的網(wǎng)表

read_design("-ref", "reference.gv");

# 讀入老的APR網(wǎng)表

read_design("-imp", "implementation.gv");

# 設(shè)置頂層

set_top("topmod");

# 設(shè)置DFT約束

set_ignore_output("scan_out*");

set_pin_constant("scan_enable", 0);

set_pin_constant("scan_mode", 0);

# 不需要再次做一致性檢查

# run_lec();

# 執(zhí)行ECO

fix_design();

report_eco();

# 確認(rèn)eco后的等價(jià)性,如果等價(jià),邏輯ECO就基本結(jié)束了

run_lec();

# 寫出eco網(wǎng)表和腳本

write_verilog("eco.gv");

write_soce2("eco.tcl");

運(yùn)行g(shù)of_lec.pl的腳本,分析不等價(jià)的點(diǎn)是否合理:

gof -run gof_eco.pl

前面大部分的設(shè)置與一致性檢查的腳本是相同的,只是把最后run_lec()換成fix_design()。在fix_design的時(shí)候,GOF ECO會(huì)先自動(dòng)做一次LEC,分析出不等價(jià)的點(diǎn),然后對(duì)不等價(jià)的點(diǎn)做eco修改。

在ECO結(jié)束后,通過(guò)report_eco來(lái)確認(rèn)改動(dòng)大小,可以看到哪些模塊增加了多少cell、刪除了多少cell、改動(dòng)多少根連線。我們需要根據(jù)ECO report來(lái)判斷本次ECO的改動(dòng)是否后端能夠?qū)崿F(xiàn)。

再通過(guò)run_lec()確認(rèn)一下修改之后是否完全等價(jià),以防止遇到一些特殊情況,GOF ECO沒(méi)有能完全修復(fù)。當(dāng)然,也需要用業(yè)界認(rèn)可的LEC工具,如formality或者conformal,來(lái)確認(rèn)最終的ECO是否正確。如果不等價(jià),可以用GOF電路圖的方式來(lái)進(jìn)一步分析和解決。

最后,寫出ECO網(wǎng)表和腳本。

五、PostMask網(wǎng)表ECO

當(dāng)流片回來(lái)測(cè)試后發(fā)現(xiàn)有問(wèn)題時(shí),就需要進(jìn)行PostMask ECO。這時(shí)只能利用提前放置Spare Cells來(lái)改金屬層。與PreMask的流程區(qū)別如下:

#read_library

# read_design

# run_lec

#fix_design

my $postmask = 1;

if($postmask){

# Postmask時(shí)讀入def文件

read_def("topmod.def");

# 設(shè)置sparecell列表

get_spare_cells("spr_1/spr_gate*");

# 設(shè)置約束

set_constraints("-num", "and<3,or<3");

# 映射到sparecell

map_spare_cells();

# 查看ECO報(bào)告

report_eco();

}

# 寫出eco網(wǎng)表和腳本

write_verilog("eco.gv");

write_soce2("eco.tcl");

在做postmask常常遇到附近資源不夠或者連線比較擁擠,這時(shí)可以調(diào)整set_constraints()的設(shè)置,多嘗試幾種方案。

六、后端工具里工作

后端工具里的操作和流程不屬于這份入門教程的范圍,但我們有一些有用的建議:

在PreMask ECO流程里,后端工具盡量可以讓插入新的Cell,這樣ECO時(shí)所有類型的stdcell都可以用,可以簡(jiǎn)化網(wǎng)表修改,也有利用于時(shí)序和DRC收斂。

在PostMask ECO時(shí),應(yīng)該盡可能地前后端工程師多溝通,一起確定最終的ECO方案。

在遇到資源緊張時(shí),應(yīng)當(dāng)與客戶、產(chǎn)品經(jīng)理、項(xiàng)目經(jīng)理等人員多溝通,給ECO條目排一排優(yōu)先級(jí),優(yōu)先解決更重要的問(wèn)題。并適當(dāng)?shù)胤艞壱恍?fù)雜的、困難的ECO。

審核編輯:劉清

-

RTL

+關(guān)注

關(guān)注

1文章

388瀏覽量

60720 -

DFT

+關(guān)注

關(guān)注

2文章

233瀏覽量

23258 -

GUI

+關(guān)注

關(guān)注

3文章

677瀏覽量

40799

原文標(biāo)題:NanDigits GOF ECO入門教程

文章出處:【微信號(hào):ExASIC,微信公眾號(hào):ExASIC】歡迎添加關(guān)注!文章轉(zhuǎn)載請(qǐng)注明出處。

發(fā)布評(píng)論請(qǐng)先 登錄

RTC實(shí)時(shí)時(shí)鐘詳細(xì)描述

Proteus仿真單片機(jī)串口的注意事項(xiàng)和實(shí)物調(diào)試注意事項(xiàng)

光伏系統(tǒng)設(shè)計(jì)思路及注意事項(xiàng)

PowerPCB到Allegro的轉(zhuǎn)換步驟與注意事項(xiàng)

全自動(dòng)端子機(jī)操作步驟_注意事項(xiàng)及保養(yǎng)

EMC現(xiàn)場(chǎng)測(cè)試的一般步驟和注意事項(xiàng)有哪些?

java中equals()方法的注意事項(xiàng)

測(cè)絕緣電阻的正確方法,有哪些步驟和注意事項(xiàng)

使用示波器探頭的步驟、技巧和注意事項(xiàng)

鉗形電流表的使用方法和注意事項(xiàng)

現(xiàn)場(chǎng)總線的使用方法與注意事項(xiàng)

profinet網(wǎng)關(guān)的接線步驟和注意事項(xiàng)

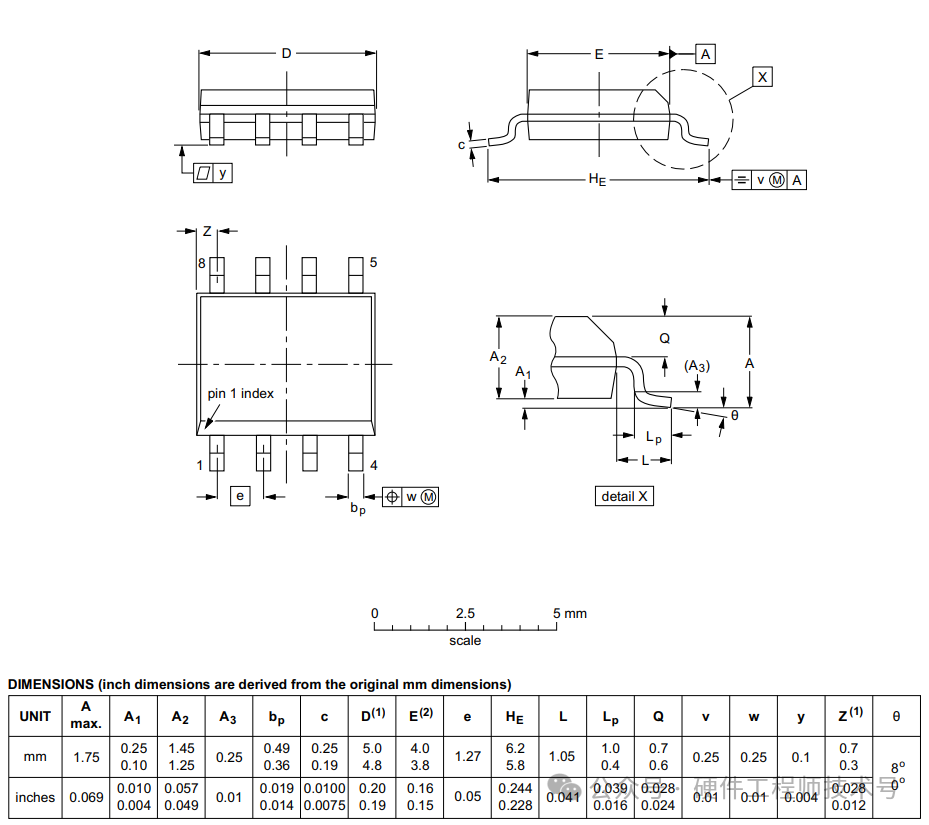

設(shè)計(jì)SO-8封裝的詳細(xì)步驟和注意事項(xiàng)

詳細(xì)描述和解釋GOF ECO每一個(gè)步驟的實(shí)現(xiàn)方法和注意事項(xiàng)

詳細(xì)描述和解釋GOF ECO每一個(gè)步驟的實(shí)現(xiàn)方法和注意事項(xiàng)

評(píng)論