傳統PCB制作流程有兩種:正片圖電流程和負片直蝕流程,兩種流程對線路圖形的設計要求各不相同。特別是正片流程,如果外層線路設計不合理,如有大的空曠獨立線路,會在圖電時產生夾膜問題,導致蝕刻時短路。

為什么正片圖電流程空曠區這種小間隙的位置會更容易產生蝕刻不凈短路,首先要了解一下正片圖電流程的生產過程:前工序--à沉銅/板電--à線路圖形轉移--à圖電(鍍銅鍍錫)--à退錫蝕刻--à后工序。

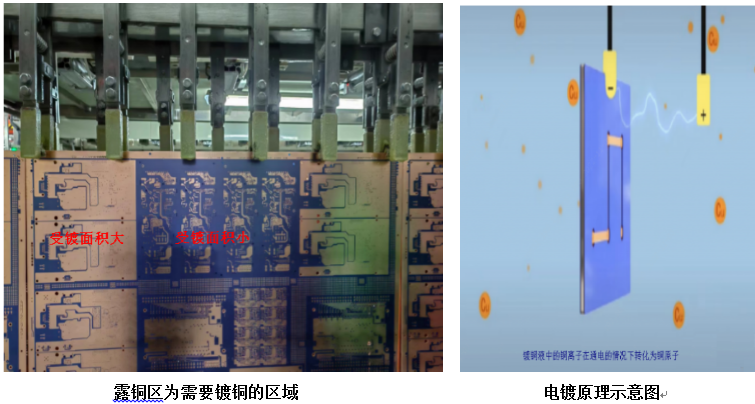

電鍍的原理是將生產大板并排夾在一條銅條飛靶上,再把板子放到含有銅離子的電鍍槽液中,電流通過銅條飛靶傳遞到板子上,板子上露出銅面的地方在電流的作用下,會吸附電鍍槽液中的銅的離子,并還原成銅原子。

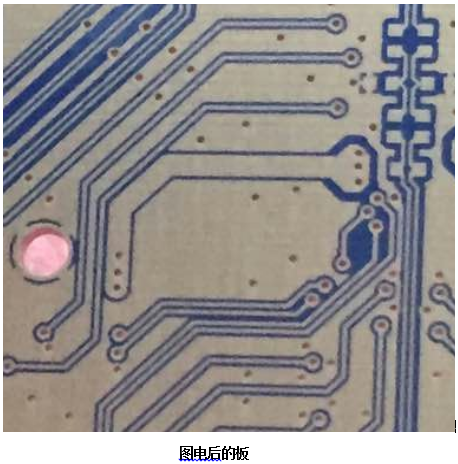

下圖藍色為干膜,白色為圖電后的線路及銅面,圖電為先鍍銅,后鍍錫,蝕刻時用錫來保護走線及銅面的,所以圖電后板面有一層白色的錫,蝕刻前需板藍色的干膜先退洗掉,露出銅面過行蝕刻,蝕刻后再把錫退先掉,就得到我們想要線路圖形了。

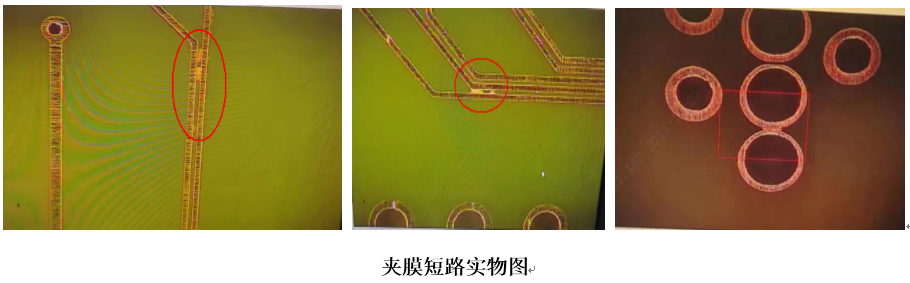

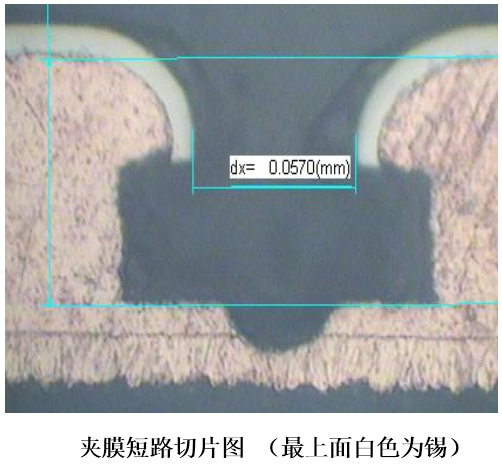

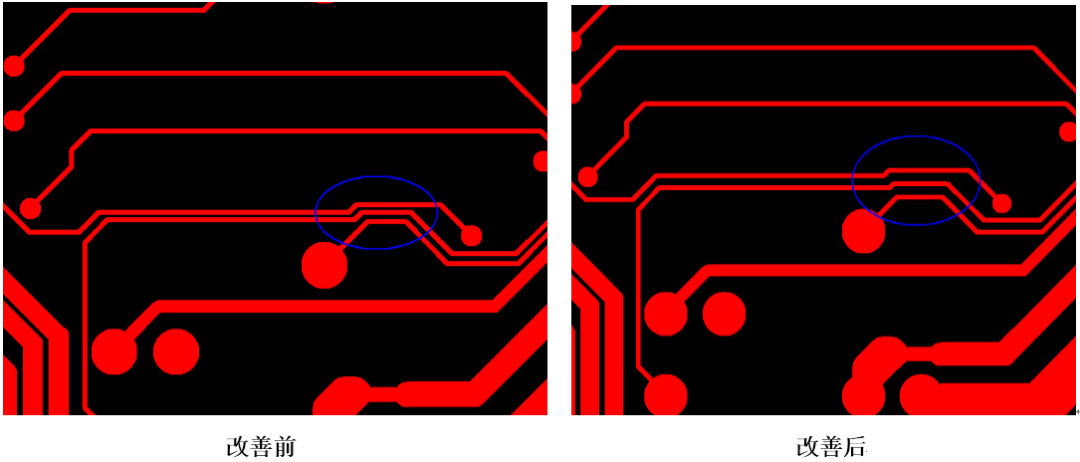

電流的大小與受鍍面積有關,如果板子上線路分布太過空曠,特別是分布不均勻的獨立線區域,所受到的電流非常大,嚴重會導致電流過大燒板,輕則導致獨立線區域鍍銅很厚,當線與線,線與焊盤,焊盤與焊盤等間隙過小時,如4mil以下間隙,則會導致這些間隙過小的地方存在線路板行業經常說的一個名詞叫“夾膜”就是把下圖中的干膜夾在中間,導致后續的不能蝕刻,從而造成品質問題。

以上說的夾膜,可能有些小伙伴不太理解,做正片線路工藝也叫圖電工藝,做外層線路時先在板面上壓干膜,再通過曝光,顯影等工序,露出需要電鍍的走線及銅面,成品無銅區域會被干膜覆蓋,這樣電鍍就只會鍍我們需要的走線及孔壁銅等,夾膜是指當線路間隙較小時,如果鋪銅不均勻或是沒有鋪銅的線路,電鍍時走線銅厚會超過干膜的厚度,隨著電鍍時間的增加,電鍍銅錫就有可能會從干膜兩側延伸包裹干膜,這種現象就稱為夾膜。在蝕刻時需要先把干膜退洗掉,露出需要蝕刻的銅面,而夾膜的地方干膜就無法完全去掉,由于干膜本身也是抗蝕層,蝕刻時此處的銅就保留下來造成板子短路。

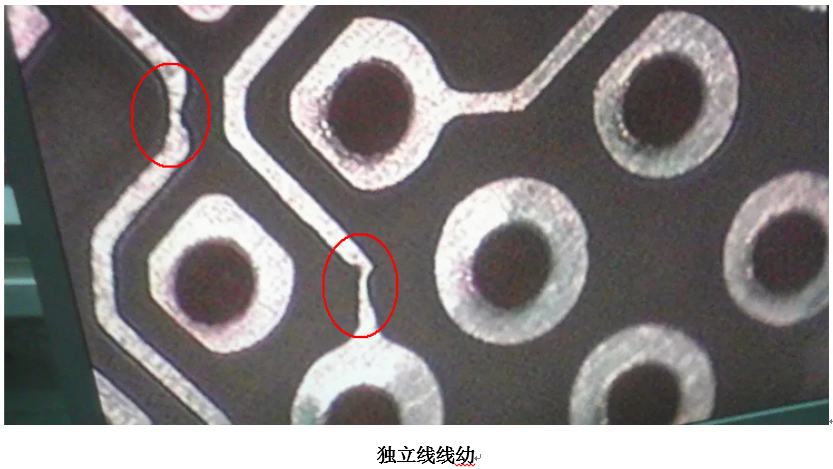

除夾膜外,獨立線路還會因為空曠區蝕刻藥水活性大,咬蝕過快,導致線幼。

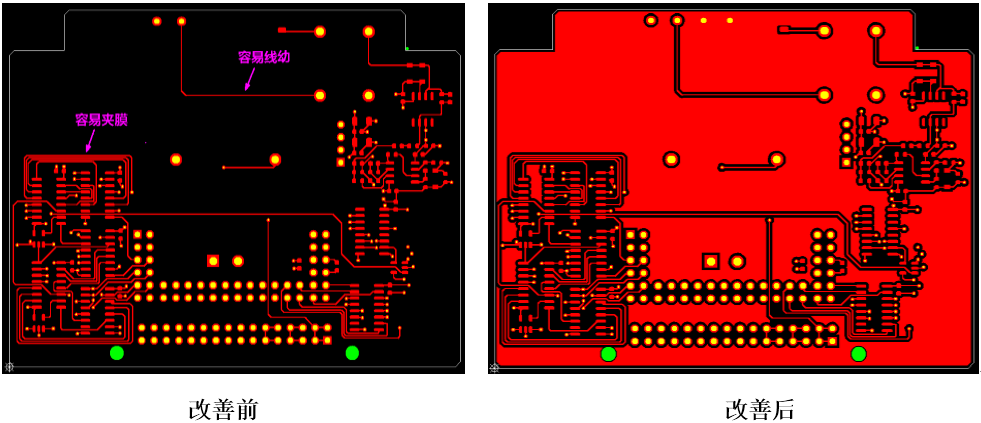

改善建議:

(1)空曠區鋪銅,提高受鍍面積,保證電鍍均勻。

(2)無法鋪銅時,可以加大獨立區線距至6mil以上(1OZ)

審核編輯 :李倩

-

pcb

+關注

關注

4365文章

23481瀏覽量

409252 -

電鍍

+關注

關注

16文章

468瀏覽量

24762 -

蝕刻

+關注

關注

10文章

424瀏覽量

16062

原文標題:【技術園地】電鍍夾膜成因及改善方法

文章出處:【微信號:江西省電子電路行業協會,微信公眾號:江西省電子電路行業協會】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

聚徽分享工業全貼合觸摸屏氣泡成因與工藝優化方案

SMT 貼片加工驚現散料危機!成因、影響全解析

通孔電鍍填孔工藝研究與優化

連接器電鍍金屬大揭秘:銅、鎳、錫、金誰最強?

膜厚測試儀的使用方法 膜厚測試儀的校準步驟

電鍍膜的性能測試方法

電鍍工藝流程詳解 電鍍技術在工業中的應用

HDI板電鍍與堆疊過程

電鍍夾膜成因及改善方法

電鍍夾膜成因及改善方法

評論