0 基本介紹

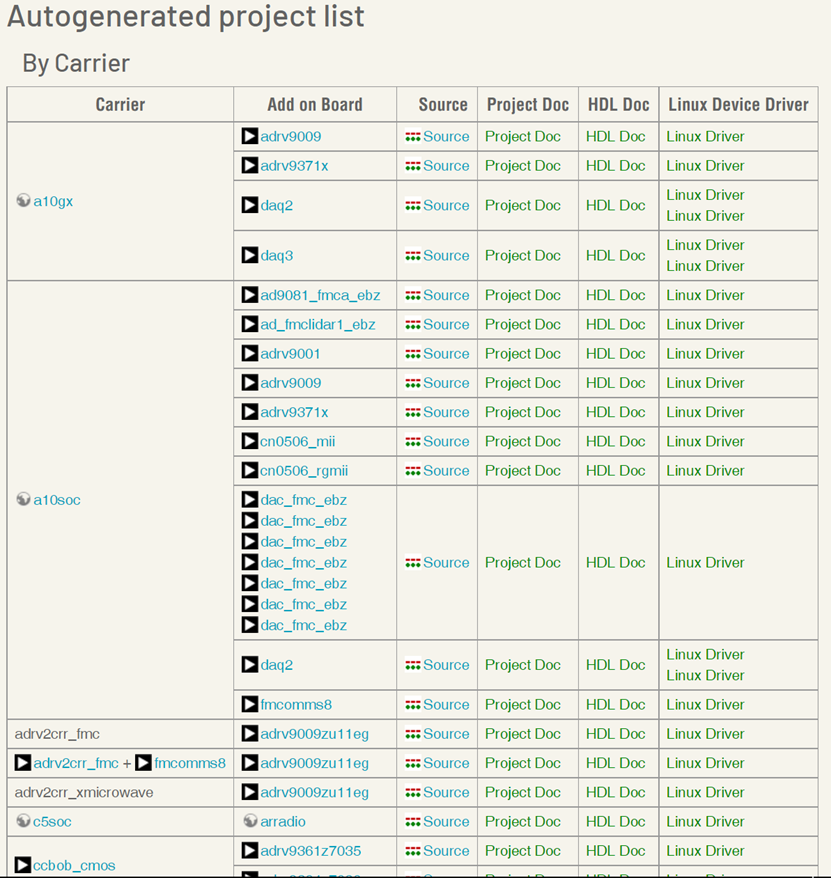

ADI的官方demo板整套快速設計是相當具有參考意義的,在購買官方開發板后,通過官方例程可以快速學習對應AD/DA的使用方法。不僅如此,ADI官方的IP核也是值得開發者深入學習的。ADI官方例程往往建立在Xilinx或Intel的官方評估板上的,所以ADI推出了在大廠FPGA上快速構建demo工程的設計流程。在產品設計上,可以采用與大廠開發板和ADI demo板類似的原理設計,這樣不僅可以減小硬件設計的風險,同時軟件設計可以在官方demo工程上進行小幅度修改,大大減小了軟硬件設計的工作量。下方鏈接為例程中載板與ADI評估板的搭配,圖1為部分例程截圖。

本文以Xilinx開發平臺為例,介紹ADI官方IP核與參考工程的快速構建流程。

1 源碼下載

首先,利用git工具將ADI的HDL源碼下載到本地,下載地址為:

https://github.com/analogdevicesinc/hdl

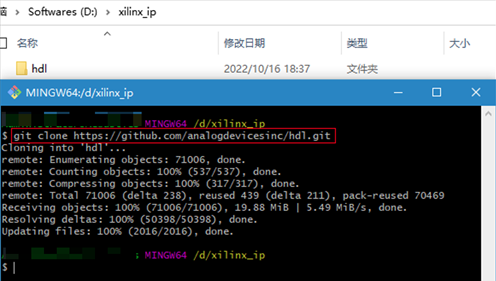

相關命令為:

git clone https://github.com/analogdevicesinc/hdl.git

如圖2所示:

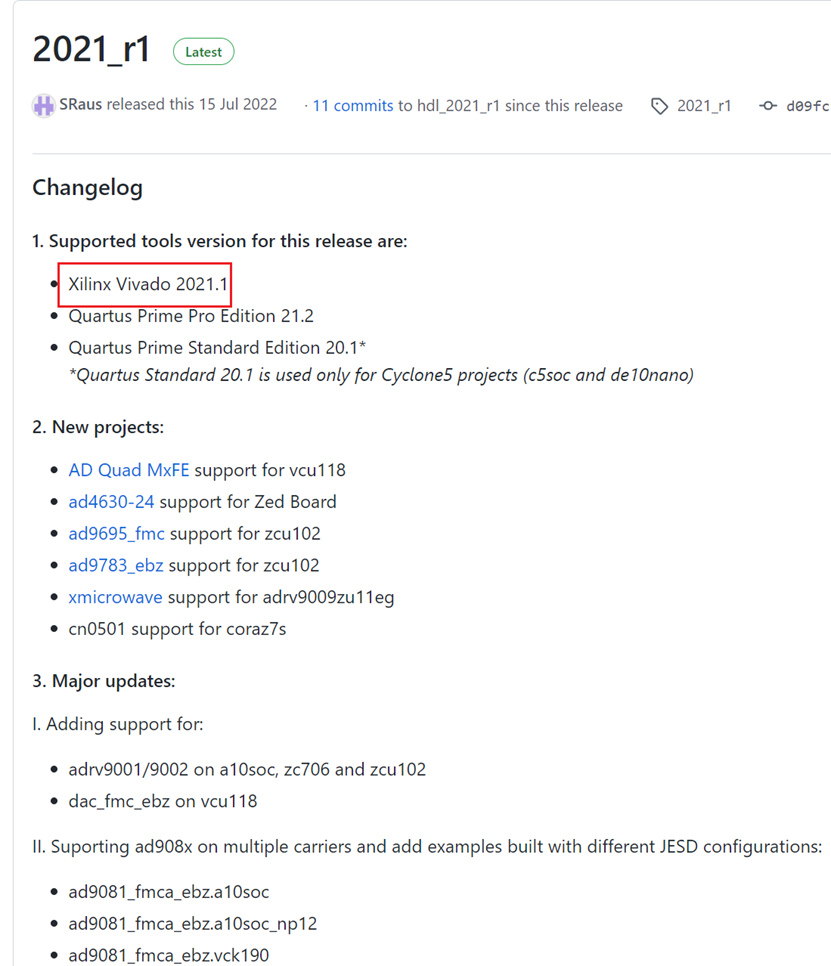

查看release網頁中構建工程所用的軟件版本,例如我們下載的master分支使用的Vivado版本為2021.1,網頁地址為:

https://github.com/analogdevicesinc/hdl

相關release頁面如圖3所示,闡明了官方例程所使用的軟件版本及相關更新說明:

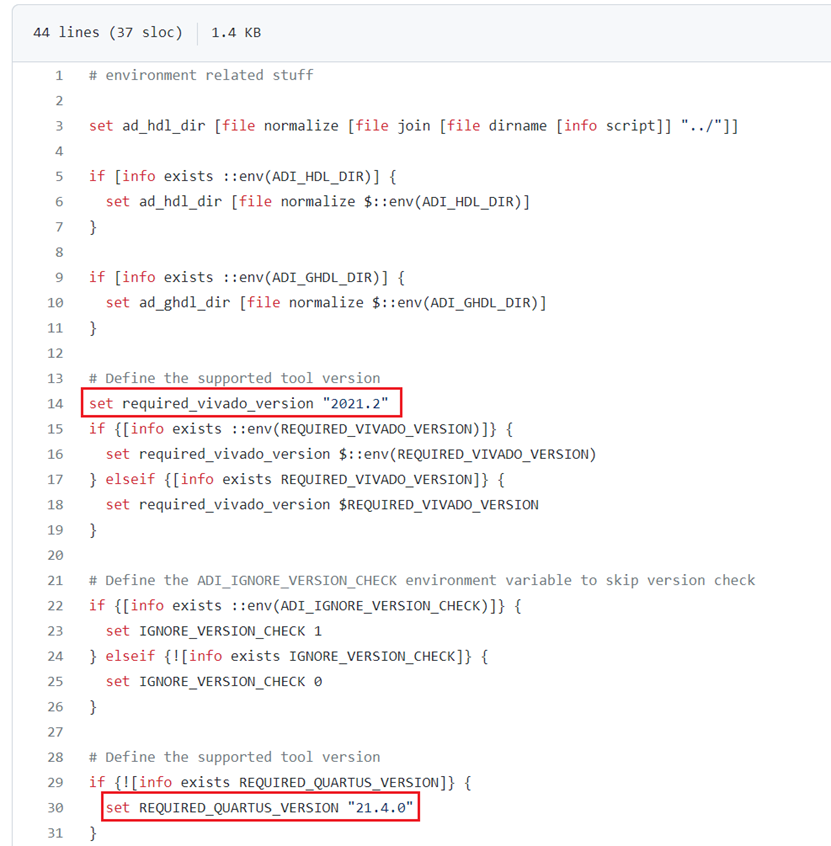

ADI官方給的腳本文件的提示也強調了軟件版本應與官方的保持一致,否則編譯無法進行。因此為了避免編譯出錯,我們構建工程所用的軟件版本應當與之保持一致,關于軟件版本相關設置在腳本“hdl/scripts/adi_env.tcl”中有所提及。此外,在腳本“hdl/library/scripts/adi_ip_xilinx.tcl”和“hdl/projects/scripts/”目錄的相關腳本中也可能提及到。圖4是相關的腳本截圖。

2 使用Cygwin64自動編譯IP核

ADI官方提供的IP核數量相當多,若選擇手動編譯,則效率太低,此處我們選擇使用Cygwin64輔助自動編譯相關的IP核。首先下載Cygwin64,下載地址為:

https://www.cygwin.com/

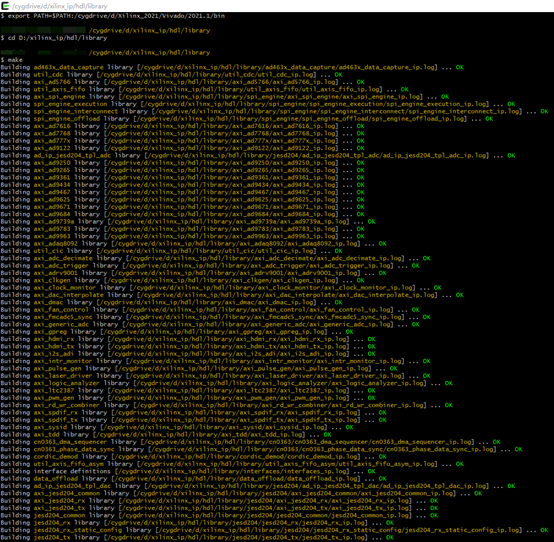

安裝務必記得勾選make工具,因為需要執行文件夾中的Makefile文件。安裝完成后,打開終端,輸入以下命令:

export PATH=$PATH:/cygdrive/d/Xilinx_2021/Vivado/2021.1/bin

(應當注意路徑使用了“/”而不是Windows系統默認的“”)

該命令是為了設置Vivado路徑,軟件版本應該與ADI官方使用的版本保持一致,否則可能編譯不通過,我們使用的版本為Xilinx Vivado 2021.1。

然后通過下述命令進入到IP核目錄:

cd D:/xilinx_ip/hdl/library

使用“make”命令自動編譯IP核即可,然后靜待IP核編譯完成(這個過程可能持續半小時左右),如圖5所示。

3 使用Tcl Shell自動搭建工程

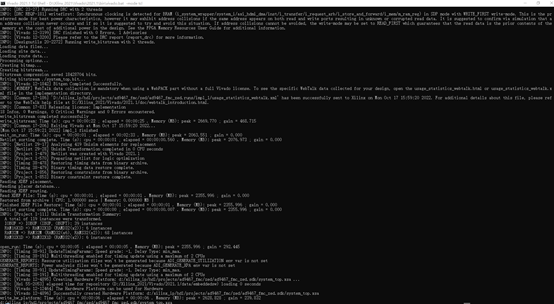

以Zedboard為載板的ad9467_fmc工程為例,打開Vivado 2021.1 Tcl Shell,輸入以下命令進入目錄:

cd D:/xilinx_ip/hdl/projects/ad9467_fmc/zed

然后輸入以下命令搭建工程,等待構建完成,如圖6所示:

source ./system_project.tcl

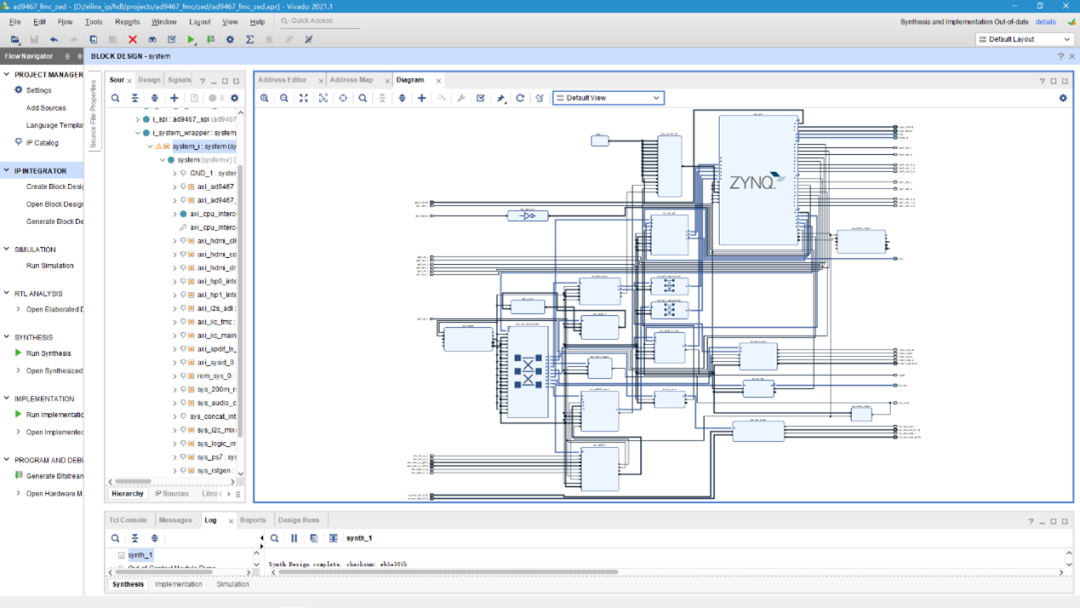

工程構建完成后,用Vivado2021.1打開即可,如圖7所示。

至此,ADI的IP核與示例工程搭建完畢。

4 總結

本文介紹了ADI官方IP核的編譯與例程的高效搭建流程。ADI官方IP核與例程對于從事ADC采集、軟件定義無線電(SDR)、FPGA開發等人群而言都是絕佳的學習資料。

審核編輯:湯梓紅

-

ADI

+關注

關注

148文章

46027瀏覽量

259186 -

IP核

+關注

關注

4文章

338瀏覽量

50522 -

demo板

+關注

關注

1文章

33瀏覽量

41300

原文標題:經驗貼:ADI官方IP核與例程編譯指南

文章出處:【微信號:純真學者出神入化,微信公眾號:純真學者出神入化】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

xilinx vivado 怎么封裝包含一個ip核的自定義ip?

請問CM408F評估板ADI官方有沒有移植TCP/IP協議棧的例程?

如何根據Xilinx官方提供的技術參數來實現對IP核的讀寫控制

MES50HP——IP核安裝與查看用戶指南

FPGA新IP核學習的正確打開方式

基于BIST的編譯碼器IP核測

在Vivado中使用SRIO高速串行協議的IP演示官方例程

經驗貼:ADI官方IP核與例程編譯指南

經驗貼:ADI官方IP核與例程編譯指南

評論