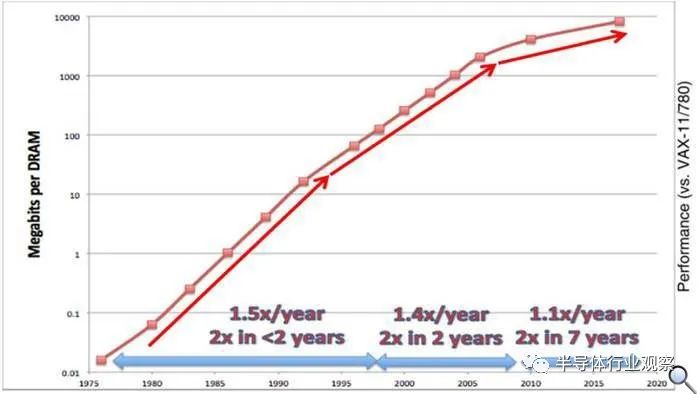

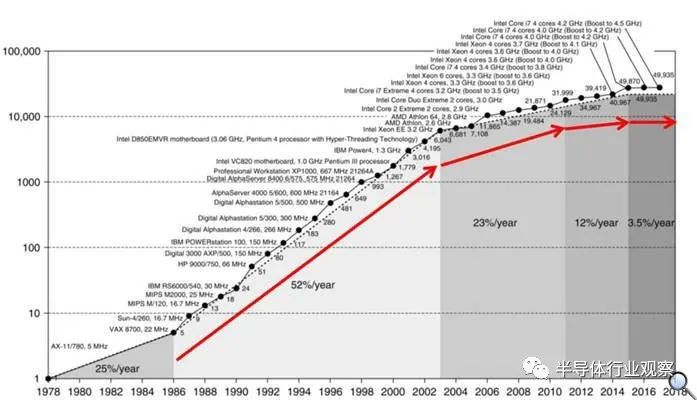

集成電路(IC) 發(fā)明至今已有50多年,自1991年問(wèn)世以來(lái),國(guó)際半導(dǎo)體技術(shù)藍(lán)圖(International Technology Roadmap for Semiconductors,ITRS) 一直是半導(dǎo)產(chǎn)業(yè)往前邁進(jìn)的指南,藍(lán)圖預(yù)測(cè)半導(dǎo)體技術(shù)會(huì)遵循摩爾定律(Moore's Law) 的縮放節(jié)奏邁進(jìn)。不過(guò),在2016年7月ITRS所釋出的半導(dǎo)體產(chǎn)業(yè)「未來(lái)藍(lán)圖」報(bào)告顯示,估計(jì)微處理器中的晶體管體積將在2021 年開(kāi)始停止縮小,這意味著微處理器中的晶體管數(shù)量將不會(huì)再如摩爾定律所說(shuō)的會(huì)逐步增加,也就是說(shuō)摩爾定律已宣告死亡。隨著摩爾定律的死亡,國(guó)際半導(dǎo)體技術(shù)藍(lán)圖ITRS也將步入歷史。取而代之的,將是異構(gòu)整合藍(lán)圖(Heterogeneous Integration Roadmap,HIR)。 雖然芯片設(shè)計(jì)和制程技術(shù)的創(chuàng)新仍然繼續(xù),但進(jìn)展已明顯趨緩,不管制程技術(shù)下殺到多少微米,芯片尺寸的縮減似乎已到了極限,更遑論同時(shí)要增加密度以提升性能。圖1及圖2是Alphabet的總裁John Hennessy 于2018 年7 月ERI會(huì)議中展示的兩張圖表。圖1顯示了40年間的DRAM的容量和密度增長(zhǎng)放緩的情況;而圖2則顯示了40年間的CPU運(yùn)算性能變化,明顯看出在近年成長(zhǎng)已趨于平穩(wěn)。

圖1. 40年間的DRAM的容量和密度增長(zhǎng)放緩的情況(資料來(lái)源:J Hennessy, ERI Conf July 2018) 半導(dǎo)體產(chǎn)業(yè)協(xié)會(huì)(SIA) 于2016年7月正式宣告ITRS國(guó)際半導(dǎo)體技術(shù)藍(lán)圖時(shí)代的結(jié)束。其后SIA 和SRC (半導(dǎo)體研究公司,Semiconductor Research Corporation)于2017 年3 月聯(lián)合發(fā)表了名為《半導(dǎo)體研究機(jī)會(huì):產(chǎn)業(yè)愿景和指南》報(bào)告(Semiconductor Research Opportunities:An Industry Vision and Guide)。報(bào)告中指出:「前進(jìn)的道路并不像摩爾定律時(shí)代那樣清晰,然而,巨大的經(jīng)濟(jì)和社會(huì)效益潛力— 其中一些是可以預(yù)見(jiàn)的,但有一些只能想像…… 在這個(gè)關(guān)鍵點(diǎn)上,需要產(chǎn)業(yè)界、政府和學(xué)術(shù)界攜手合作,才能持續(xù)進(jìn)步成長(zhǎng)。」

圖2. 40年間的CPU運(yùn)算性能成長(zhǎng),近年已趨緩 (資料來(lái)源:J Hennessy, ERI Conf July 2018)

應(yīng)用及市場(chǎng)需求帶動(dòng)

在今天,電子產(chǎn)品已深深融入我們的社會(huì)結(jié)構(gòu),改變著我們的生活、工作和娛樂(lè)方式,讓我們生活在數(shù)位時(shí)代,為我們的全球生活方式、產(chǎn)業(yè)和商業(yè)行為帶來(lái)高新的效率。而這種效率的達(dá)成主要?dú)w功于高效能運(yùn)算芯片的產(chǎn)出。另一方面,大數(shù)據(jù)的形成則推動(dòng)了市場(chǎng)需求,從而形成了技術(shù)研發(fā)的驅(qū)動(dòng)力。 在現(xiàn)實(shí)層面,推動(dòng)數(shù)據(jù)增長(zhǎng)的市場(chǎng)力量包括:

將數(shù)據(jù)、邏輯和應(yīng)用程序轉(zhuǎn)移到云端

社交媒體的推波助瀾

行動(dòng)設(shè)備的演變

5G/6G 通信加上物聯(lián)網(wǎng)(IoT)帶動(dòng)

人工智能(AI)、虛擬現(xiàn)實(shí)(VR)及增強(qiáng)現(xiàn)實(shí)(AR)的應(yīng)用

自動(dòng)駕駛汽車(chē)的興起及日漸普及

異構(gòu)整合興起

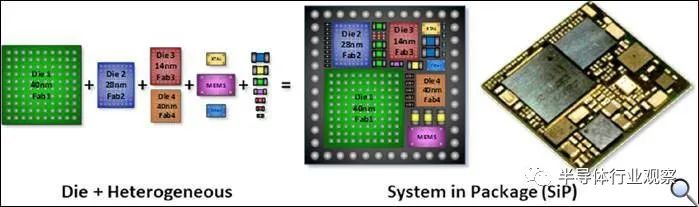

雖然制程技術(shù)的演進(jìn)已漸漸無(wú)法滿(mǎn)足芯片「體積縮小性能提升」的無(wú)止境需求,但需求并沒(méi)有消失,因此,人們開(kāi)始往構(gòu)裝技術(shù)動(dòng)腦筋。 異構(gòu)整合是指將單獨(dú)制造的「組件」整合到更高層次的組裝(系統(tǒng)級(jí)封裝- System in a Package,SiP),以使整體性能提升。系統(tǒng)級(jí)封裝不是隨便將兩個(gè)芯片封裝在一起就可以,而是必須滿(mǎn)足下列條件才行:

封裝后體積必須變小:將不同功能的芯片與被動(dòng)元件封裝成一顆IC,所以封裝后體積必定比個(gè)別數(shù)顆IC還小。

須整合不同類(lèi)型的封裝技術(shù):必須將數(shù)種不同類(lèi)型的封裝技術(shù)整合在一起,與單純將多個(gè)芯片封裝在一起的小型封裝技術(shù)不同。

必須包含各種類(lèi)型的主動(dòng)與被動(dòng)元件:必須包含處理器、記憶體、邏輯元件、類(lèi)比元件等數(shù)個(gè)芯片,甚至必須將被動(dòng)元件、連接器、天線等一起封裝進(jìn)去。

在異構(gòu)整合的定義中,「組件」指的是任何單元,無(wú)論是單顆芯片、MEMS器件、被動(dòng)元件和組裝的封裝或子系統(tǒng),都整合在一個(gè)封裝中。當(dāng)中可以涉及到材料、元件類(lèi)型、電路類(lèi)型、節(jié)點(diǎn)、互連方法……等等。

圖3. 異構(gòu)整合(圖左) 及系統(tǒng)級(jí)封裝(圖右) (資料來(lái)源:日月光半導(dǎo)體)

大廠紛紛投入

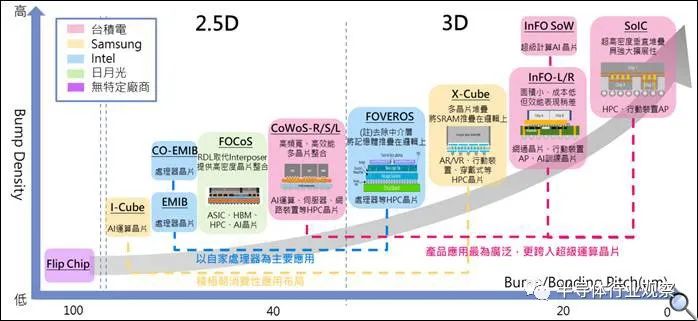

在芯片堆疊密度增長(zhǎng)及多芯片整合的需求下,大廠紛紛投入先進(jìn)封裝技術(shù)的發(fā)展。其中又以運(yùn)算芯片制程大廠Intel、TSMC及Samsung的投入最為理所當(dāng)然。這些大廠將其先進(jìn)制程技術(shù)所產(chǎn)出的芯片配合自家的先進(jìn)封裝,來(lái)完成客戶(hù)的產(chǎn)品;而封測(cè)大廠日月光則是從本身的封裝技術(shù)出發(fā),慢慢發(fā)展出2.5D及3D之先進(jìn)封裝技術(shù)(圖2)。

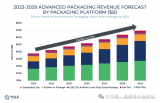

從圖2可見(jiàn),整體來(lái)看,TSMC目前是站在比較領(lǐng)先的地位,從2.5D到3D封裝都有相當(dāng)完整的技術(shù)。另一方面,Intel的Foveros及EMIB也逐漸形成了一個(gè)平臺(tái)。 由于先進(jìn)封裝要求的技術(shù)很高,因此很多大廠也相應(yīng)的在這方面投入很高的資本支出。從圖3可見(jiàn),2022年的資本支出已達(dá)到10 ~ 40億的等級(jí)。目前各大廠都有本身的技術(shù)平臺(tái),而最近產(chǎn)出的新產(chǎn)品也不少。

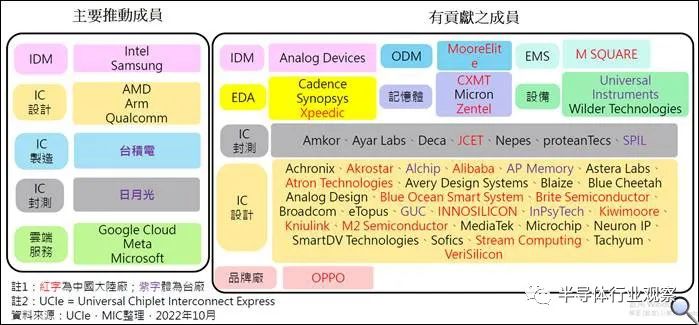

而其中一個(gè)于2022年最重要的動(dòng)態(tài)是Intel于2022年3月邀請(qǐng)了臺(tái)積電、Samsung、AMD、Microsoft、Google、日月光等大廠共同組成及推動(dòng)UCIe小芯片聯(lián)盟,有助于小芯片(Chiplet)資料傳輸架構(gòu)的標(biāo)準(zhǔn)化;未來(lái)在UCIe小芯片聯(lián)盟的推動(dòng)下,會(huì)越來(lái)越趨向標(biāo)準(zhǔn)化,從而降低小芯片先進(jìn)封裝設(shè)計(jì)的成本。 此外,透過(guò)制定統(tǒng)一的小芯片/晶粒(Die)間傳輸規(guī)范,以落實(shí)晶粒「隨插即用(Plug and Play)」的目的,使來(lái)自不同廠商、代工廠的晶粒能在單一封裝內(nèi)順利整合,一定程度上滿(mǎn)足了高階運(yùn)算芯片持續(xù)提升運(yùn)算單元密度以及整合多元功能的需求,成為開(kāi)發(fā)高階運(yùn)算芯片的關(guān)鍵。 UCIe自成立以來(lái),已有數(shù)十家包含IC設(shè)計(jì)、封測(cè)、材料設(shè)備、電子設(shè)計(jì)自動(dòng)化系統(tǒng)等不同類(lèi)型的業(yè)者紛紛加入,顯示小芯片先進(jìn)封裝的跨領(lǐng)域特性。從圖4可見(jiàn),圖右的貢獻(xiàn)會(huì)員除了IDM、IC封測(cè)及IC設(shè)計(jì)廠商外,還有EDA、ODM、記憶體、EMS及終端產(chǎn)品廠商, 顯示UCIe聯(lián)盟的影響力越來(lái)越廣。。

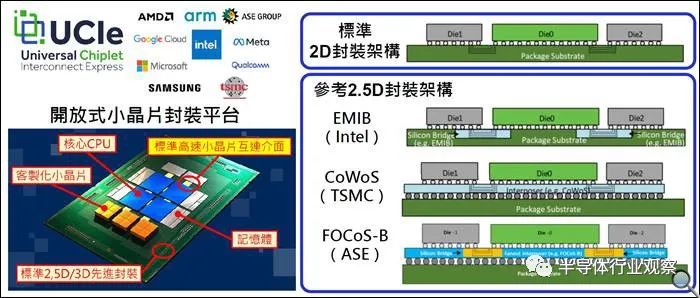

小芯片聯(lián)盟先導(dǎo)的推動(dòng)成員在標(biāo)準(zhǔn)主導(dǎo)上占了一定的優(yōu)勢(shì),像Intel便推出了自己的開(kāi)放式小芯片平臺(tái),如圖6左邊部分所示,可以用Intel自家的CPU去整合客戶(hù)的小芯片,輔以Intel本身的2.5D、3D技術(shù)去完成完整的封裝;而這就是Intel推動(dòng)其IDM 2.0一個(gè)很重要的助力,提供了一個(gè)平臺(tái)可讓Intel進(jìn)行代工及封測(cè)服務(wù)。 不過(guò),聯(lián)盟成員也不會(huì)獨(dú)厚Intel,目前已提供了成員數(shù)個(gè)小芯片封裝可用的架構(gòu),包括圖6右邊的標(biāo)準(zhǔn)2D封裝架構(gòu)及2.5D封裝架構(gòu) (可參考Intel的EMIB、TSMC的CoWoS及日月光的FOCoS)。

大廠技術(shù)

經(jīng)過(guò)長(zhǎng)時(shí)間的研發(fā),先導(dǎo)大廠的異構(gòu)整合先進(jìn)封整產(chǎn)品均已開(kāi)始提供服務(wù),像TSMC臺(tái)積電從CoWoS、InFO,到SoIC,已經(jīng)累積豐富的先進(jìn)封裝經(jīng)驗(yàn),形成3D Fabric平臺(tái);臺(tái)積電透過(guò)3D Fabric平臺(tái),整合2.5/3D先進(jìn)封裝技術(shù),為頂級(jí)客戶(hù)客制最佳化產(chǎn)品,透過(guò)綁定先進(jìn)制程,提供先進(jìn)制程代工到先進(jìn)封裝的一條龍服務(wù),主要產(chǎn)品類(lèi)別為HPC高效能運(yùn)算與高階智慧型手機(jī)芯片。 就Intel的部分,前面已經(jīng)提過(guò),發(fā)展先進(jìn)封裝技術(shù)為Intel IDM 2.0策略中關(guān)鍵的一環(huán)。近期Intel陸續(xù)推出2.5D封裝的嵌入式多芯片互連橋接(Embedded Multi-die Interconnect Bridge, EMIB)技術(shù)、3D堆疊的Foveros技術(shù),以及整合2.5D與3D封裝的共嵌入式多芯片互連橋接Co-EMIB技術(shù)。Intel的Foveros 封裝技術(shù)利用3D 堆疊整合不同的邏輯芯片,為IC設(shè)計(jì)公司提供了很大的靈活性,允許其將不同技術(shù)的IP 區(qū)塊與各種記憶體和I/O 元件混合和搭配。Intel的Foveros可以讓芯片產(chǎn)品分解成更小的小芯片(chiplets) 或細(xì)芯片(tiles),其中I/O、SRAM 和電源傳輸電路整合在基礎(chǔ)芯片中,而高性能邏輯小芯片則是堆疊在頂部。 至于記憶體大廠Samsung則是提供記憶體堆疊異構(gòu)整合封裝服務(wù),包括其在2020 International Wafer-Level Packaging Conference (IWLPC)中展示的記憶體堆疊(Memory Stack)異構(gòu)整合技術(shù),以及其「X-Cube (eXtended-Cube)」3D封裝技術(shù),包含把記憶體與其他芯片整合,以及硅穿孔、微凸塊等關(guān)鍵技術(shù)。

審核編輯 :李倩

-

摩爾定律

+關(guān)注

關(guān)注

4文章

637瀏覽量

79250 -

芯片設(shè)計(jì)

+關(guān)注

關(guān)注

15文章

1030瀏覽量

55037 -

封裝技術(shù)

+關(guān)注

關(guān)注

12文章

555瀏覽量

68046

原文標(biāo)題:【行業(yè)分析】先進(jìn)封裝技術(shù)的發(fā)展趨勢(shì)

文章出處:【微信號(hào):江西省電子電路行業(yè)協(xié)會(huì),微信公眾號(hào):江西省電子電路行業(yè)協(xié)會(huì)】歡迎添加關(guān)注!文章轉(zhuǎn)載請(qǐng)注明出處。

發(fā)布評(píng)論請(qǐng)先 登錄

相關(guān)推薦

電力電子技術(shù)的應(yīng)用與發(fā)展趨勢(shì)

先進(jìn)封裝成為AI時(shí)代的核心技術(shù)發(fā)展與創(chuàng)新

先進(jìn)封裝的核心概念、技術(shù)和發(fā)展趨勢(shì)

人工智能半導(dǎo)體及先進(jìn)封裝技術(shù)發(fā)展趨勢(shì)

先進(jìn)封裝的技術(shù)趨勢(shì)

先進(jìn)封裝技術(shù)的類(lèi)型簡(jiǎn)述

激光雷達(dá)技術(shù)的發(fā)展趨勢(shì)

智能駕駛技術(shù)發(fā)展趨勢(shì)

變阻器的未來(lái)發(fā)展趨勢(shì)和前景如何?是否有替代品出現(xiàn)?

如何控制先進(jìn)封裝中的翹曲現(xiàn)象

無(wú)線充電技術(shù)發(fā)展趨勢(shì)

1.3萬(wàn)字!詳解半導(dǎo)體先進(jìn)封裝行業(yè),現(xiàn)狀及發(fā)展趨勢(shì)!

先進(jìn)封裝技術(shù)綜述

智慧燈桿發(fā)展趨勢(shì)

先進(jìn)封裝技術(shù)的發(fā)展趨勢(shì)

先進(jìn)封裝技術(shù)的發(fā)展趨勢(shì)

評(píng)論