概述

浙江省微波毫米波射頻產業聯盟旗下杭州城芯科技有限公司隨著雷達系統數字化水平的提高,數字相控陣雷達的應用越來越廣泛,相較于傳統的模擬相控陣雷達系統,數字相控陣雷達系統具有合成波束的靈活性更強、旁辦抑制度更優、動態范圍更大等優點。是未來雷達系統的發展方向。相較于傳統的模擬相控陣雷達系統,數字相控陣雷達系統不再依靠模擬的移相器、衰減器以及微波合成網絡等來實現空間波束的合成與掃描。而是直接通過AD轉換器將接收到的模擬信號數字化,在數字域進行更靈活更復雜的數據處理。典型的數字相控陣系統框圖如下所示:

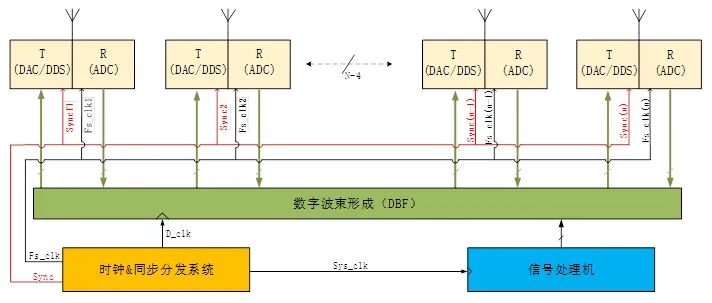

圖1 典型數字相控陣系統框圖

完整的數字相控陣系統包括數字T/R收發單元陣列(每一個收發單元包括一個接收的ADC模塊及一個發射的DAC/DDS模塊)、數字波束形成模塊(DBF)、信號處理機模塊以及時鐘生成及分發模塊。其中數字收發單元陣列實現模擬信號的收發及數字化,數字波束形成模塊通過對各個收發單元的數據進行加權、延時、補償等操作實現波束的合成,信號處理機模塊用于對接收到的數據進行處理并完成對整個系統的控制,時鐘生成及分發模塊實現采樣時鐘以及同步信號的分發。

由于數字相控陣系統需要嚴格控制每個收發單元的采樣時刻以方便數字波束合成,故時鐘生成及分發模塊需要嚴格約束分發到每一個收發單元的采樣時鐘(Fs_clk1~Fs_clk(n))的相位關系。理想情況下,需要保證分發到每一個收發單元的采樣時鐘(Fs_clk1~Fs_clk(n))嚴格對齊。在大規模數字相控陣系統中,不同的收發單元往往距離很遠,且位于不同的PCB板上。為實現同步采樣,時鐘分發網絡一般采用分布式實現以減小連線數量。典型的時鐘Fs_clk及同步信號Sync分發網絡如圖2所示:

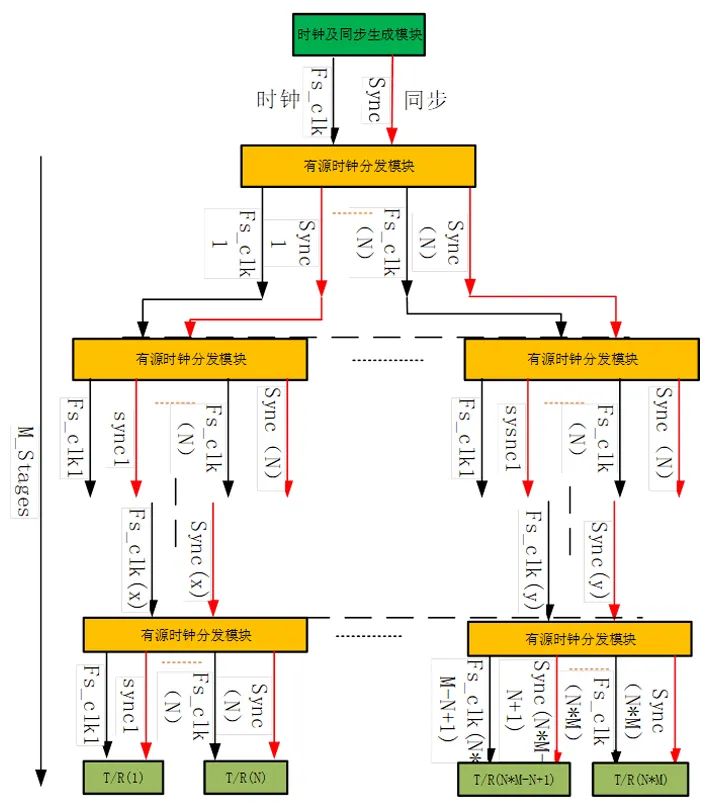

圖2 數字相控陣系統時鐘及同步信號分發網絡

時鐘及同步生成模塊產生采樣時鐘及同步信號,通過有源時鐘分發模塊將采樣時鐘及同步信號逐級分發,假設一級有源時鐘分發模塊可輸出N組時鐘及同步信號,采用M級串聯可實現NM組時鐘及同步信號。實際系統實現中由于每一級時鐘分發模塊及連接電纜均會引入一定的延時Td±Δt,M級模塊共引入延時M*(Td±Δt)。其中Td為時鐘分發模塊的平均絕對延時和電纜的固有延時(相對Fs_clk的延時),Δt為由于模塊制造誤差及所處環境溫度不同造成的延時誤差和電纜長度的差異造成的延時。

杭州城芯科技有限公司自主研發的CX3E04/CX3E04N芯片,可以為上述時鐘和同步的分發系統提供硬件支撐。可極大減小時鐘和同步信號分發網絡的設計和調試難度。

芯片概述

CX3E04/CX3E04N是一款高性能低電壓低功耗的時鐘分配器,能夠產生最多14路分頻比可配置的超低相位噪聲的同步時鐘,支持LVDS*和CML兩種輸出模式。

CX3E04/CX3E04N可滿足不同應用場景的時鐘頻率、同步配置、多通道和低噪聲的要求,并通過多種時鐘管理和分配特性來簡化大規模陣列板卡的時鐘樹設計,提供14路低噪聲且可配置的時鐘輸出,可靈活與多種器件連接,包括數據轉換器、現場可編程門陣列(FPGA)和混頻器本振(LO)。

CX3E04/CX3E04N共有14路時鐘和SYNC通道,各通道可以獨立配置分頻比、延時和輸出模式。每個通道可以獨立配置成CLK通道或者SYNC通道,當配置成SYNC輸出模式時,其SYNC信號可以由外部輸入,也可以由內部電路產生連續或者脈沖模式的SYNC信號。

CX3E04/CX3E04N具有多通道和多芯片同步功能,可以根據內部或者外部輸入的SYNC信號對芯片進行同步,可以保證每個通道輸出同步的時鐘信號。

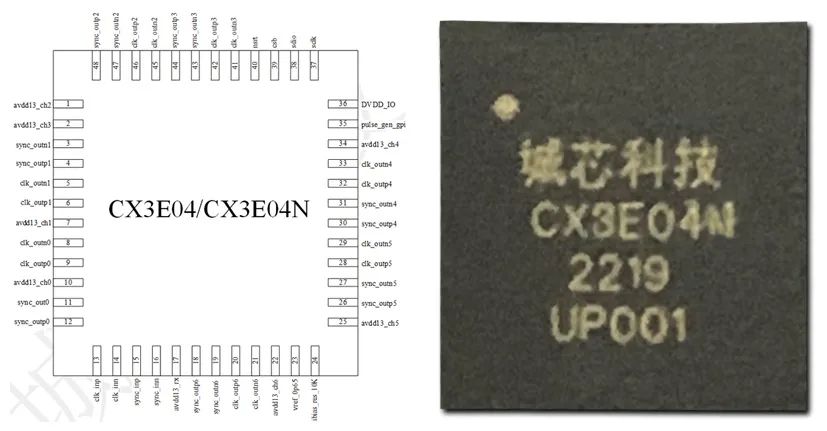

CX3E04/CX3E04N管腳定義及芯片實物如下所示:

圖3 CX3E04/CX3E04N管腳定義及實物

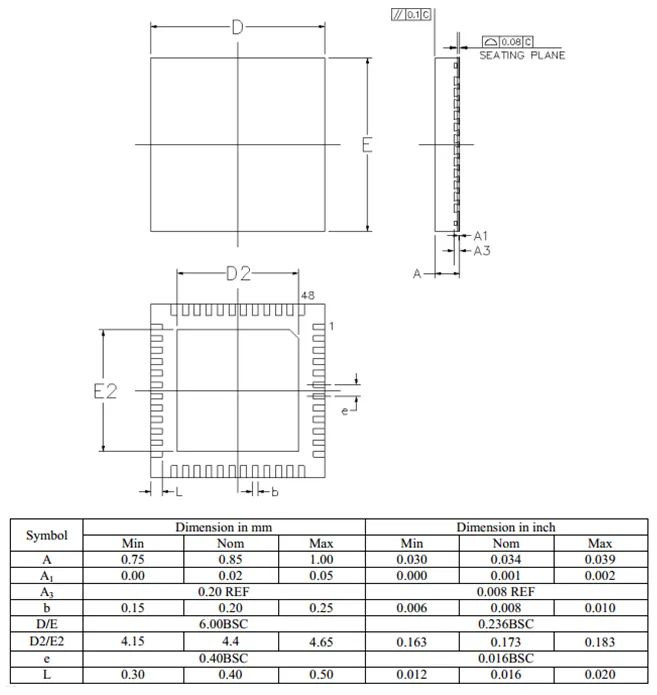

CX3E04為工業級,CX3E04N為軍品級,器件均為QFN 48pin封裝、封裝尺寸為6mm×6mm,其封裝如下所示:

圖4 CX3E04/CX3E04N芯片封裝圖

器件優良特性

CX3E04芯片正是采用了重同步時鐘方案,實現了Sync與采樣時鐘Fs_clk相對相位關系不隨時鐘網絡級數增加而增加,保證了整個數字相控陣系統同步的可靠性。

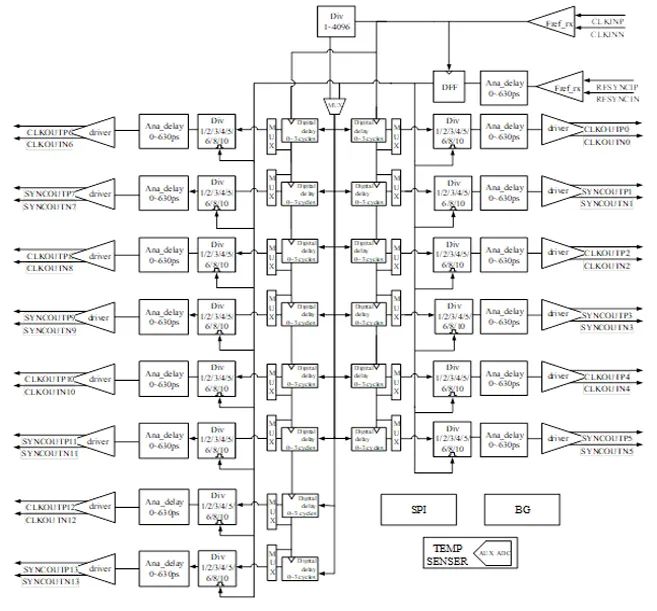

CX3E04芯片是一款專門為數字相控陣系統設計的時鐘/同步信號分發芯片,最多可實現14組時鐘信號的分發,優異的相位噪聲性能保證CX3E04芯片可配合任何一款時鐘生成模塊進行時鐘分發且幾乎不惡化相位噪聲性能。每個輸出通道均可對延時進行獨立配置,用于補償系統延時誤差,延時精度優于1.5ps。采樣時鐘對Sync的重采樣功能保證Sync的延時誤差不隨時鐘網絡級數的增加而累積,用戶僅需保證單級延時誤差不超過一個采樣時鐘周期即可輕松實現同步。此外,CX3E04采用了低功耗設計,典型情況下每個通道輸出功耗低于18mW。芯片內部系統框圖如下所示:

圖5 CX3E04/CX3E04N芯片系統框圖

其核心特性如下

· 附加時鐘抖動(Additive Jitter):10fs;

· 低電壓供電:1.3V;

· 低功耗:單個通道電流<15mA;

· 最多提供14路LVDS*或CML模式輸出時鐘:

參考時鐘輸入頻率范圍:10MHz~2GHz;

輸出延時可配置范圍:0~630ps;

輸出延時精度:1.5ps;

輸出級電流可配置范圍:3.2mA~8mA;

14路通道可獨立配置延時、分頻比和輸出模式;

· SYNC扇出功能:

延時可配置0~3個參考時鐘周期;

· SYNC片內產生:

連續模式;

脈沖模式(SPI控制);

脈沖模式(GPI控制);

脈沖模式(SYNC控制);

參考時鐘的1~4096分頻任意配置;

· 輸入管腳:

差分/單端;

片內50Ω阻抗匹配;

支持交流和直流耦合;

· 輸出管腳:

支持LVDS*(共模0.65V)和CML模式;

CML模式內部集成50Ω匹配電阻;

支持交流和直流耦合;

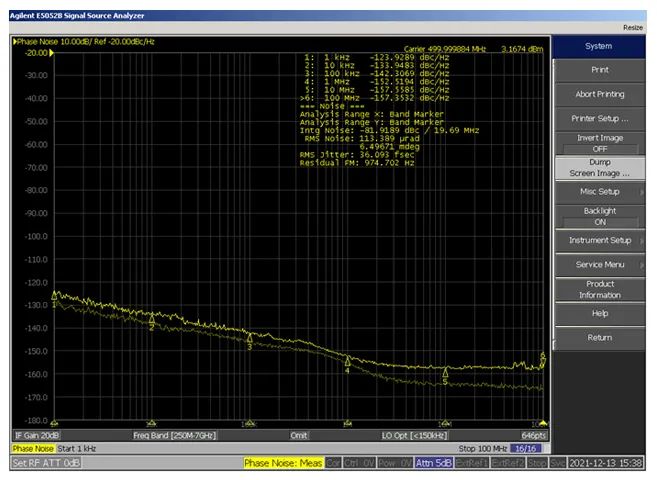

其相位噪聲典型特性如下

芯片在500MHz輸出情況下,典型相位噪聲測試結果如下所示:

圖6 CX3E04/CX3E04N相位噪聲測試圖

時鐘與同步信號分發系統架構

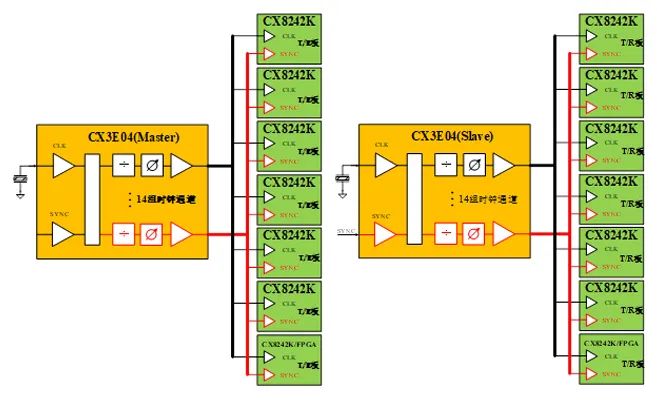

CX3E04/CX3E04N芯片支持MASTER和SLAVE 2種工作模式,典型應用方案如下所示:

圖7 CX3E04/CX3E04N

典型應用方案一

圖8 CX3E04/CX3E04N

典型應用方案二

如圖7所示,CX3E04可以用作Master模式,外部輸入CLK時鐘信號,芯片內部產生SYNC信號輸出,14路輸出可以最多同時驅動7顆CX8242K射頻直采收發芯片或者其他芯片。如圖8所示,CX3E04可以用作Slave模式,外部輸入CLK時鐘信號和SYNC信號,再經過14路輸出可以最多同時驅動7顆CX8242K芯片或者其他芯片。

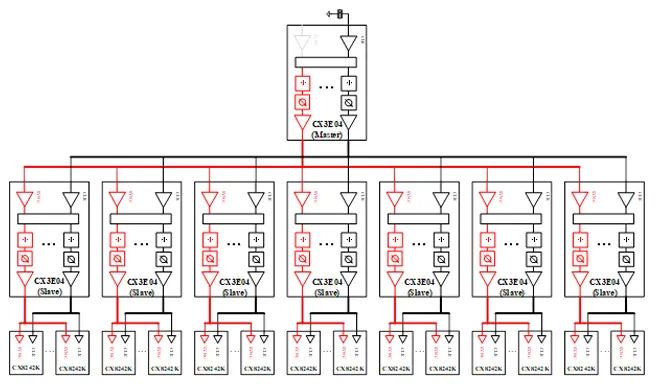

如圖9 所示,當需要大規模組陣的時候,可以采用CX3E04(配置成Master模式,內部產生SYNC信號)驅動7顆CX3E04(Slave模式),可給最多49顆CX8242K射頻直采收發芯片提供采樣時鐘和SYNC信號。以此類推,通過更多CX3E04芯片增加時鐘通道,可以實現更大規模的陣列系統,且整個陣列系統SYNC信號的延時不累積。

圖9 CX3E04/CX3E04N典型應用方案三

審核編輯:湯梓紅

-

adc

+關注

關注

99文章

6650瀏覽量

548389 -

雷達系統

+關注

關注

6文章

258瀏覽量

29066 -

相控陣

+關注

關注

3文章

93瀏覽量

14363

原文標題:CX3E04用于數字相控陣系統同步解決方案

文章出處:【微信號:浙江射頻產業聯盟,微信公眾號:浙江射頻產業聯盟】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

Qorvo 推出用于相控陣雷達系統的先進電源解決方案 三芯片解決方案提供可配置的 GAN 偏置點自動校準

同步控制的大功率機載相控陣雷達電源設計

【模擬對話】相控陣波束成形IC簡化天線設計

索尼(sony)數碼攝像機 HDR-CX100E/CX105

NXP CX24109數字衛星電視調諧方案

CX3E04用于數字相控陣系統同步解決方案

CX3E04用于數字相控陣系統同步解決方案

評論