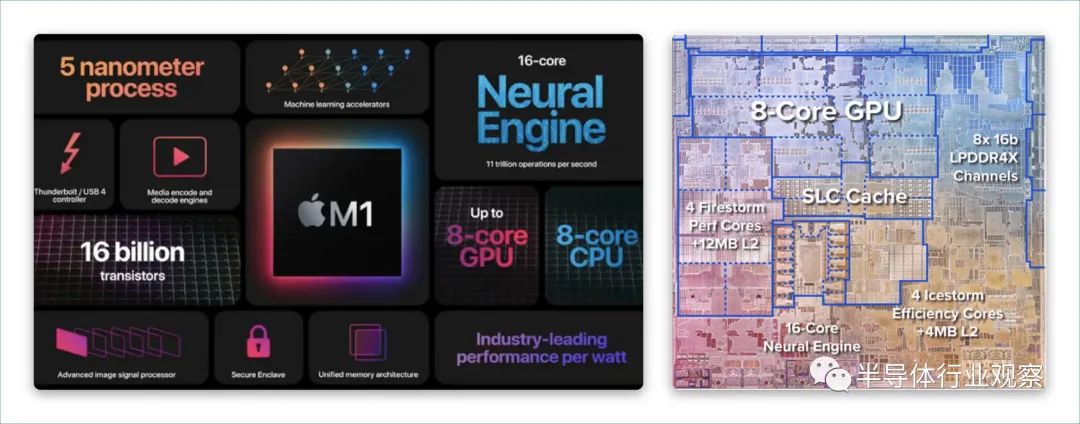

圖 1:Apple M1 SoC 參考:AnandTech

在這種情況下,主要挑戰(zhàn)是:

1.選擇并與多家 IP 供應(yīng)商合作

2.不同的 IP 供應(yīng)商可能有不同的 IP 許可方案,工程師將無(wú)法自由地定制 ISA 和設(shè)計(jì),因?yàn)樗麄兏敢鉂M足他們的設(shè)計(jì)目標(biāo)。

3.所有專(zhuān)門(mén)的 ISA 都不會(huì)持續(xù)/生存很長(zhǎng)時(shí)間,從而影響長(zhǎng)期產(chǎn)品支持計(jì)劃和路線圖。

4.此外,涉及多個(gè) ISA 和工具鏈的軟件/應(yīng)用程序開(kāi)發(fā)和更新將具有挑戰(zhàn)性。

什么是 RISC-V,它與其他 ISA 有何不同?

二、RISC-V 基礎(chǔ) ISA

RISC-V 是一個(gè)相關(guān) ISA 家族:RV32I、RV32E、RV64I、RV128I。

RV32I/ RV32E/ RV64I/RV128I 是什么意思:

RV——RISC-V

32/64/128 – 定義寄存器寬度 [XLEN] 和地址空間

I – 整數(shù)基 ISA

32 個(gè)用于所有基本 ISA 的寄存器

E – 嵌入式:只有 16 個(gè)寄存器的基本 ISA

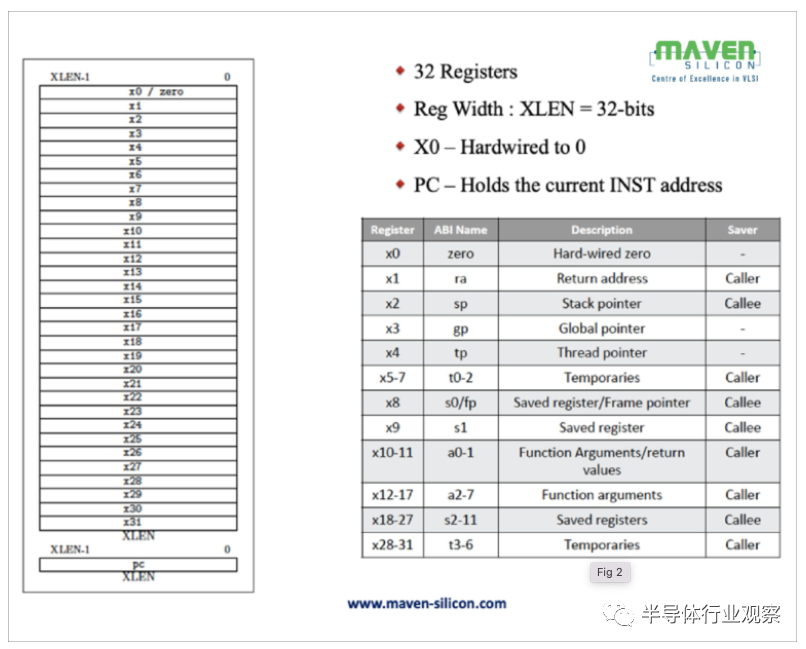

(1)RISC-V 寄存器:

圖 2:RISC-V 寄存器和 ABI 名稱(chēng)參考:RISC-V 規(guī)范

(2)RISC-V內(nèi)存:

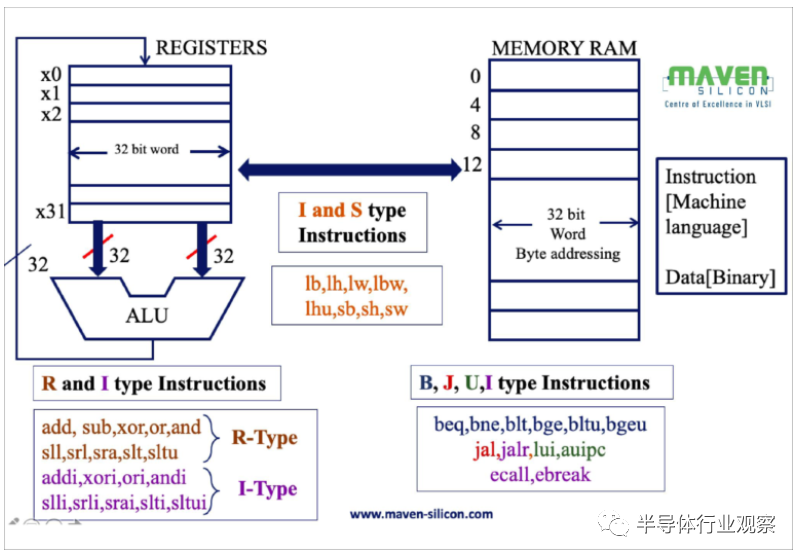

(3)RISC-V 加載存儲(chǔ)架構(gòu)

RISC-V處理器根據(jù)PC中的地址從主存中取/載指令,譯碼32位指令,然后ALU進(jìn)行算術(shù)/邏輯/內(nèi)存讀寫(xiě)操作。ALU 的結(jié)果將存儲(chǔ)回其寄存器或內(nèi)存中。

圖 3:RISC-V 加載存儲(chǔ)架構(gòu)

(4)RISC-V RV32 I 基礎(chǔ) ISA

R-Type:注冊(cè)到注冊(cè)說(shuō)明

I-Type:立即注冊(cè)、加載、JLR、Ecall 和 Ebreak

S型:商店

B型:分支

J型:跳躍和鏈接

U 型:立即加載/添加上層

圖 4:RV32I 基本 ISA 指令格式

(5)用于優(yōu)化 RTL 設(shè)計(jì)的 RISC-V ISA

立即數(shù)總是經(jīng)過(guò)符號(hào)擴(kuò)展,并且通常被打包到指令中最左邊的可用位,并且已被分配以降低硬件復(fù)雜性。尤其是,

主要操作碼總是在位 0-6 中。

目標(biāo)寄存器(如果存在)始終位于位 7-11 中。

第一個(gè)源寄存器(如果存在)始終位于第 15-19 位。

第二個(gè)源寄存器(如果存在)始終位于第 20-24 位。

但是為什么立即位會(huì)被打亂呢?想想解碼直接場(chǎng)的物理電路。由于它是硬件實(shí)現(xiàn),因此這些位將被并行解碼;輸出立即數(shù)中的每一位都有一個(gè)多路復(fù)用器來(lái)選擇它來(lái)自哪個(gè)輸入位。多路復(fù)用器越大,成本越高,速度也越慢。

值得注意的是,只需要主要操作碼(位 0-6)就可以知道如何解碼立即數(shù),因此立即數(shù)解碼可以與指令其余部分的解碼并行完成。

(6)RV32I 基本 ISA 指令

RISC-V ISA 擴(kuò)展

此處列出了所有 RISC-V ISA 擴(kuò)展:

圖 5:RISC-V ISA 擴(kuò)展

整數(shù) 64 位基本 ISA + 擴(kuò)展:[乘法 + 原子 + SP 浮動(dòng) + DP 浮動(dòng) + 壓縮]

RISC-V 特權(quán)架構(gòu)

RISC-V 特權(quán)架構(gòu)涵蓋了 RISCV 系統(tǒng)的所有方面,超出了我到目前為止所解釋的非特權(quán) ISA。特權(quán)架構(gòu)包括特權(quán)指令以及運(yùn)行操作系統(tǒng)和連接外部設(shè)備所需的附加功能。

示例:運(yùn)行類(lèi) Unix 操作系統(tǒng)的桌面等系統(tǒng)

Hypervisor Execution Environment – HEE:RISC-V hypervisor,為來(lái)賓操作系統(tǒng)提供多個(gè)管理級(jí)執(zhí)行環(huán)境。

示例:運(yùn)行多個(gè)guest操作系統(tǒng)的云服務(wù)器

圖 6:RISC-V 特權(quán)軟件堆棧參考:RISC-V 規(guī)范

原文鏈接:https://semiwiki.com/semiconductor-services/maven-silicon/321555-is-your-career-at-risk-without-risc-v/

END

(添加請(qǐng)備注公司名和職稱(chēng))

對(duì)話Imagination中國(guó)區(qū)董事長(zhǎng):以GPU為支點(diǎn)加強(qiáng)軟硬件協(xié)同,助力數(shù)字化轉(zhuǎn)型

原文標(biāo)題:RISC-V給我們帶來(lái)了什么?

文章出處:【微信公眾號(hào):Imagination Tech】歡迎添加關(guān)注!文章轉(zhuǎn)載請(qǐng)注明出處。

-

imagination

+關(guān)注

關(guān)注

1文章

598瀏覽量

62083

原文標(biāo)題:RISC-V給我們帶來(lái)了什么?

文章出處:【微信號(hào):Imgtec,微信公眾號(hào):Imagination Tech】歡迎添加關(guān)注!文章轉(zhuǎn)載請(qǐng)注明出處。

發(fā)布評(píng)論請(qǐng)先 登錄

RISC-V MCU技術(shù)

risc-v芯片在電機(jī)領(lǐng)域的應(yīng)用展望

賽昉科技將亮相RISC-V產(chǎn)業(yè)發(fā)展大會(huì),帶來(lái)應(yīng)用、軟件、人才三大核心主題分享

《RISC-V能否復(fù)制Linux 的成功?》

直播預(yù)約 | RISC-V大使談RISC-V軟硬件生態(tài)最新進(jìn)展和未來(lái)趨勢(shì)張國(guó)斌

RISC-V,即將進(jìn)入應(yīng)用的爆發(fā)期

加入全球 RISC-V Advocate 行列,共筑 RISC-V 的未來(lái) !

RISC-V Summit China 2024 青稞RISC-V+接口PHY,賦能RISC-V高效落地

RISC-V Summit China 2024 | 青稞RISC-V+接口PHY,賦能RISC-V高效落地

2024 RISC-V 中國(guó)峰會(huì):華秋電子助力RISC-V生態(tài)!

2024 RISC-V 中國(guó)峰會(huì):華秋電子助力RISC-V生態(tài)!

risc-v的發(fā)展歷史

rIsc-v的缺的是什么?

走進(jìn)RISC-V:芯片界的新革命

【議題征集】2024 Hong Kong RISC-V Day 來(lái)了!

RISC-V給我們帶來(lái)了什么?

RISC-V給我們帶來(lái)了什么?

評(píng)論